LA FEDERAL DE ENGENHARIA DE ITAJUBÁ

Projeto de um Modulador Sigma-Delta de Segunda Ordem em Low Voltage, Utilizando a Técnica de Capacitores Chapeados

CARLOS RENATO TREVISAN DE MORI

JULHO / 1999

## Escola Federal de Engenharia de Itajubá

# Projeto de um Modulador Sigma-Delta de Segunda Ordem em *Low Voltage*, Utilizando a Técnica de Capacitores Chaveados

por

## Carlos Renato Trevisan de Mori

Orientadores: Prof. Tales Cleber Pimenta, PhD. Prof. MSc. Paulo César Crepaldi

Dissertação apresentada à Escola Federal de Engenharia de Itajubá como parte dos requisitos necessários para a obtenção do título de Mestre em Engenharia Elétrica.

Aos meus pais, José e Odila, e irmãos, Luiz Fernando e Ana Claudia, dedico.

## Agradecimentos

À Deus, pelo seu insuperável amparo em todos os momentos.

A todos os meus familiares, especialmente meus pais e irmãos, por seu incondicional incentivo e amor.

Aos professores orientadores, Tales Cleber Pimenta e Paulo César Crepaldi, pelo crédito, confiança, amizade e pela ajuda na realização desse trabalho.

Aos amigos e ex-colegas de trabalho, engenheiros Robson Luiz Moreno e Adriano Marques Pereira, e a todos do Grupo de Microeletrônica da EFEI, pelas constantes sugestões e contribuições para esse trabalho.

Aos amigos e quase irmãos, próximos ou distantes, Luiz Aurélio, Leandro, Ernesto, Claudio, Renata e Gisele, por seu incontestável apoio, pelos momentos de descontração e, principalmente, pela paciência.

À fundação CAPES, que através do programa "Demanda Social" viabilizou esse projeto.

Meus humildes e sinceros agradecimentos.

## Resumo

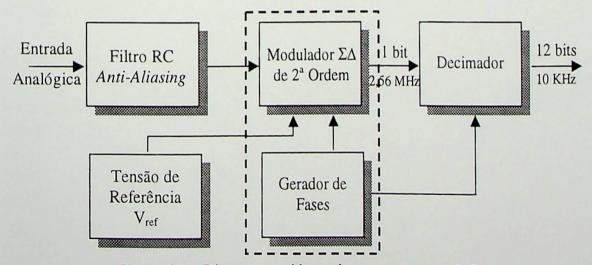

Os recentes avanços nas tecnologias digitais aplicadas a circuitos de processamento de sinal possibilitaram a sua utilização em larga escala em circuitos integrados devido ao seu baixo custo, à sua alta precisão e à possibilidade de se alcançar altas velocidades. Dessa forma, tornou-se também necessário o desenvolvimento de conversores análogo/digitais capazes de suprir as necessidades dos circuitos digitais de processamento de sinal, ou seja, conversores compatíveis com esses últimos. Conversores A/D baseados na modulação sigmadelta (ΣΔ) são uma alternativa de baixo custo para conversores de alta resolução e podem ser integrados sem maiores problemas em CIs de processamento digital de sinal. Normalmente, outros tipos de conversores convencionais não alcançam as velocidades exigidas por esses circuitos, além de se tornarem muito complexos quando a precisão exigida é alta.

Esse trabalho mostra o projeto de um modulador ΣΔ de precisão, implementado com a técnica de capacitores chaveados e que opera em baixa tensão (low voltage). A operação em low voltage é fundamental nos sistemas eletrônicos portáteis modernos, pois permite a utilização de um número menor de baterias nestes sistemas. A utilização da técnica de capacitores chaveados, ao invés de uma implementação analógica convencional, é importante na redução do tamanho do circuito modulador (menor custo) e proporciona a implementação de "resistores simulados" mais lineares e precisos que os circuitos implementados com resistores integrados.

## **Abstract**

The recently advances in digital circuits, such as high speed, high precision and low cost, made possible the wide use of signal processing circuits. In that way, it became also necessary the development of analog-to-digital converters to meet the needs of the digital signal processing circuits. The A/D converters based on sigma-delta ( $\Sigma\Delta$ ) modulation are a low cost alternative for converters of high resolution and can be a part of digital signal processing IC. Usually, other types of conventional converters don't reach the speeds required by digital signal processing circuits and can become very complex as the precision increases.

This work aims the design of a resolution  $\Sigma\Delta$  modulator implemented using the switched-capacitor technique for low voltage operation. The low voltage operation is essential in modern portable electronic systems to guarantee a smaller number of batteries. The use of switched-capacitor technique allows a reduction of modulator size (smaller cost) and more linear and precise "simulated resistors".

# Índice

| Capit | ulo 1                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | - Introdução                                         |     |

|-------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------|-----|

|       | 1.1                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | Considerações Gerais                                 | 01  |

|       | 1.2                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | Justificativas                                       | ()2 |

|       |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | Objetivo                                             | 03  |

|       | 1.4                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | Estrutura do Trabalho                                | 03  |

| Capít |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | - Conceitos Básicos                                  |     |

|       |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | Princípio da Sobreamostragem                         | 05  |

|       | 2.2                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | Modulador Delta e Sigma-Delta                        | 08  |

|       |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 2.2.1 Modulador Delta                                | 08  |

|       |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 2.2.2 Modulador Sigma-Delta                          | ()9 |

|       | 2.3                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | Técnica de Capacitores Chaveados                     | 12  |

|       |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 2.3.1 Princípio de Funcionamento                     | 12  |

|       |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 2.3.2 Integradores com Capacitores Chaveados         | 13  |

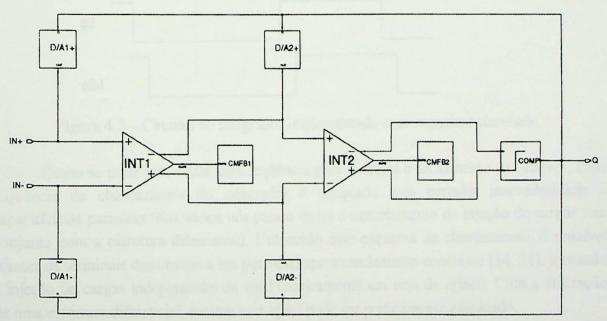

| Capít | ulo 3                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | – Definição da Arquitetura                           |     |

|       | 3.1                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | Considerações Iniciais                               | 15  |

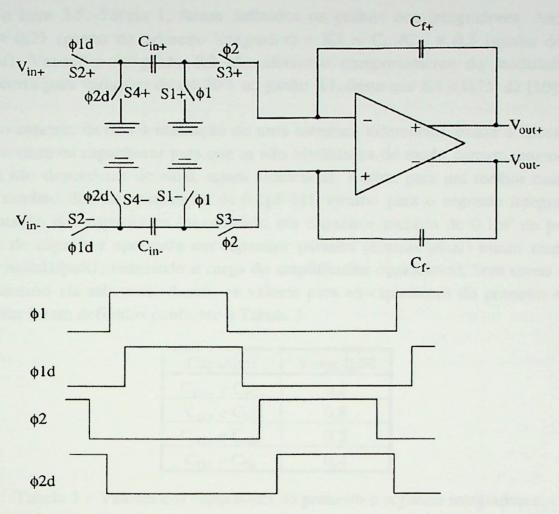

|       | 3.2                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | Integradores                                         | 17  |

|       |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 3.2.1 Primeiro Integrador                            | 17  |

|       |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 3.2.2 Segundo Integrador                             | 22  |

|       | 3.3                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | Comparador                                           | 23  |

|       | 3.4                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | Conversor D/A                                        | 24  |

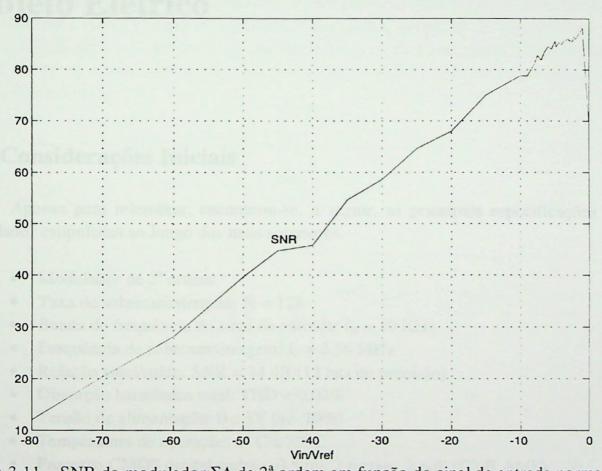

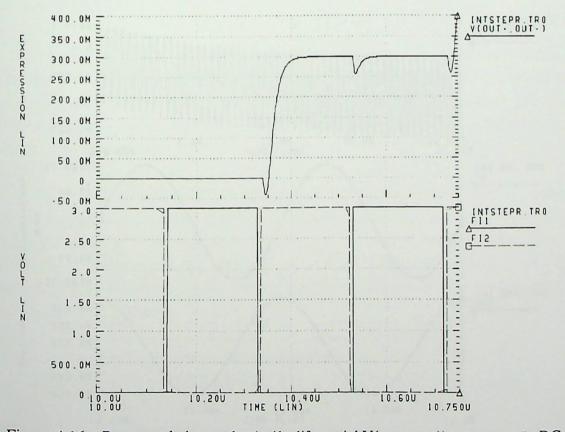

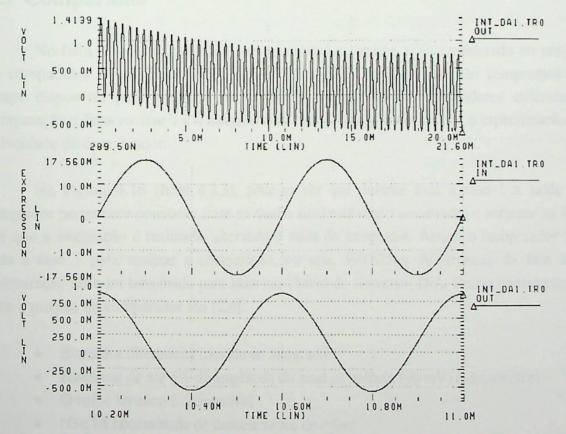

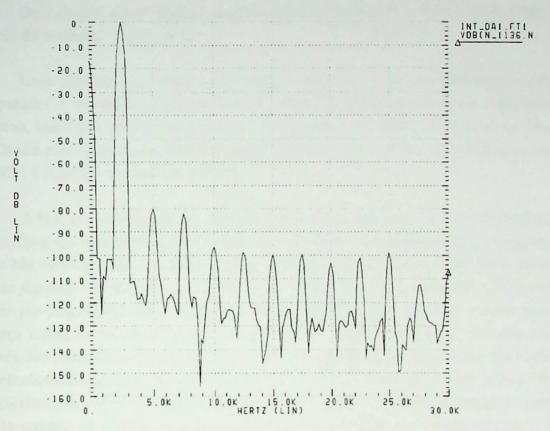

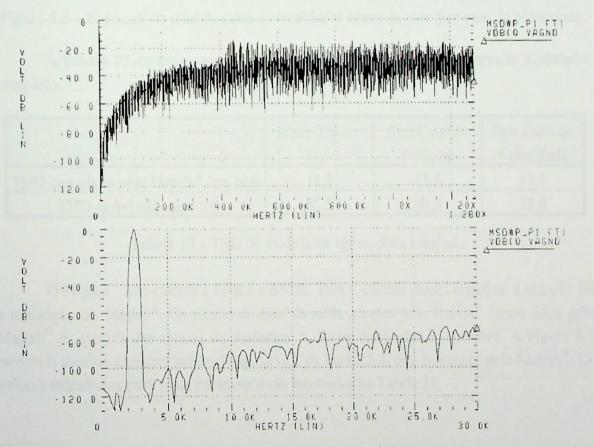

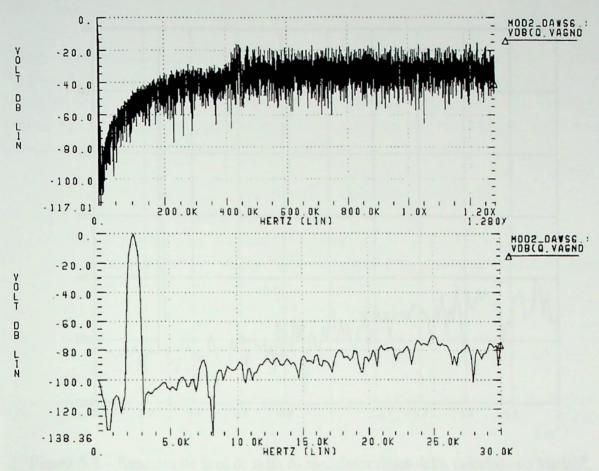

|       | 3.5                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | Simulação Funcional                                  | 25  |

| Capít | ulo 4                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | - Projeto Elétrico                                   |     |

|       | 4.1                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | Considerações Iniciais                               | 33  |

|       | 4.2                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | Integradores                                         | 34  |

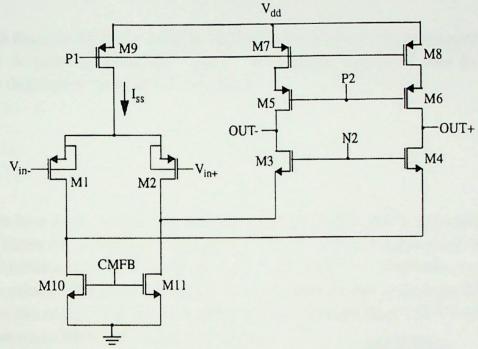

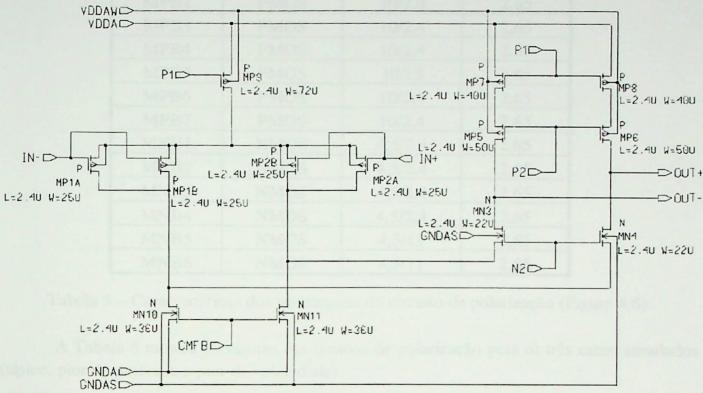

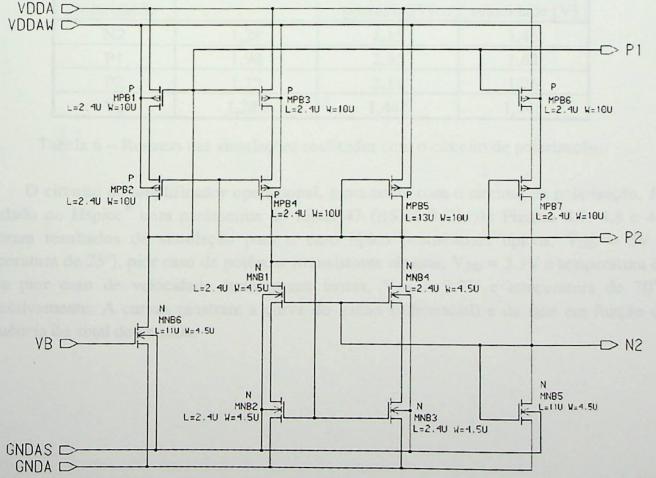

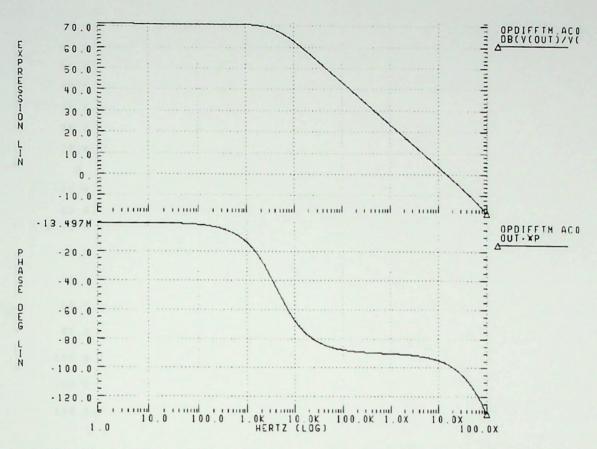

|       |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 4.2.1 Projeto do Amplificador Operacional            | 37  |

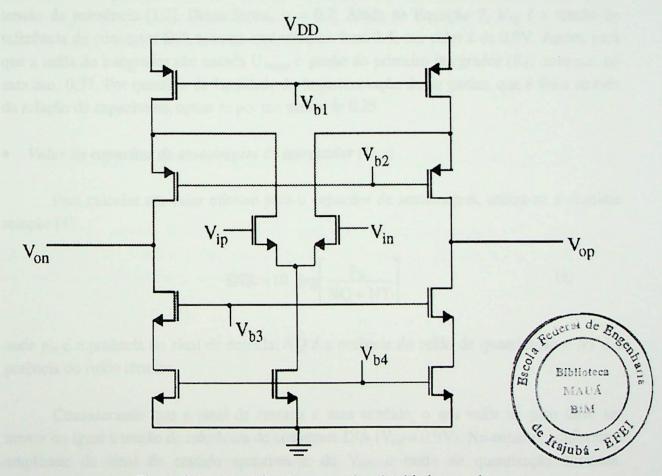

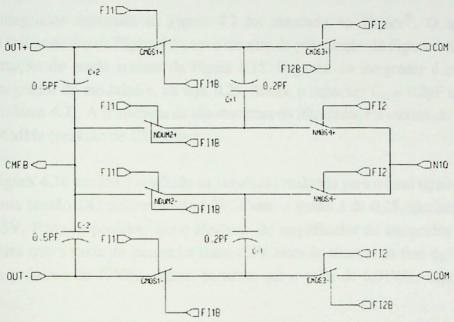

|       |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 4.2.2 Circuito de Realimentação de Modo Comum (CMFB) | 49  |

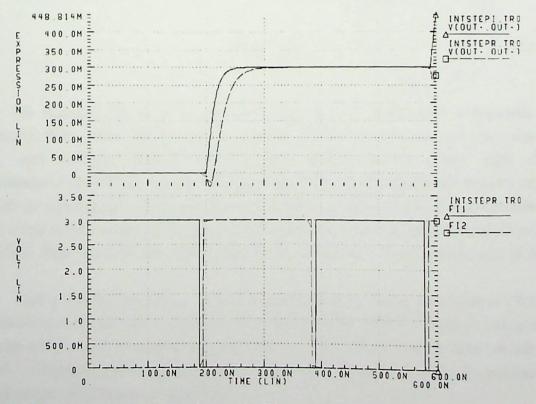

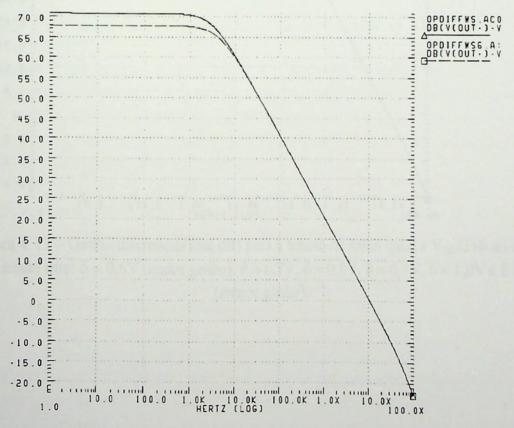

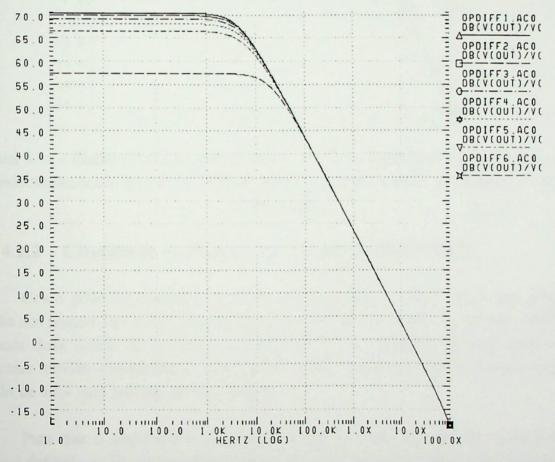

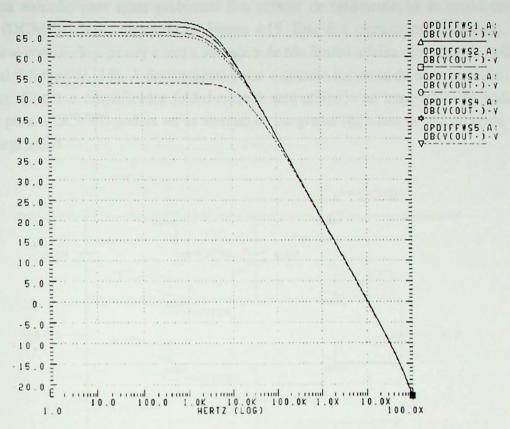

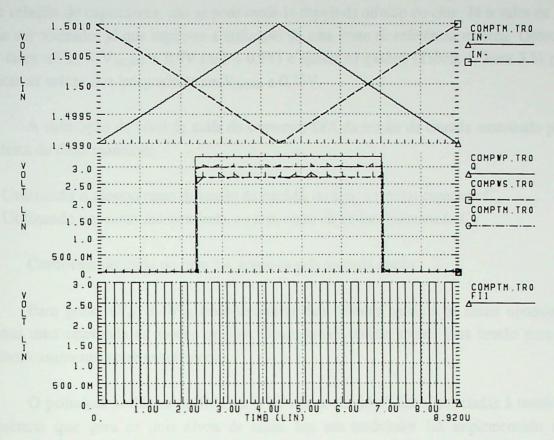

|       |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 4.2.3 Simulação Elétrica do Integrador               | 51  |

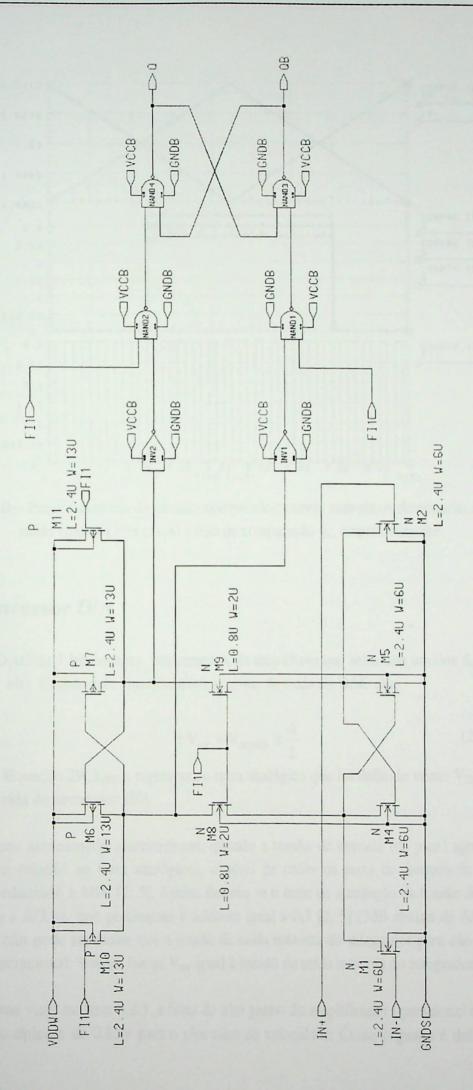

|       | 4.3                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | Comparador                                           | 53  |

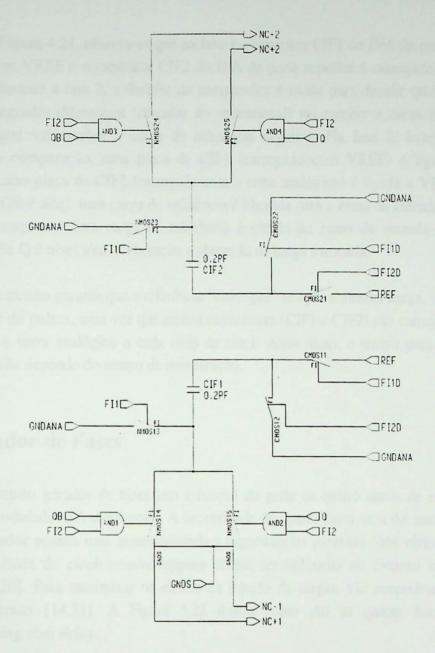

|       |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | Conversor D/A                                        | 56  |

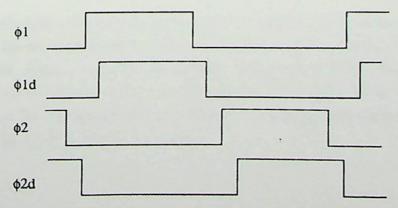

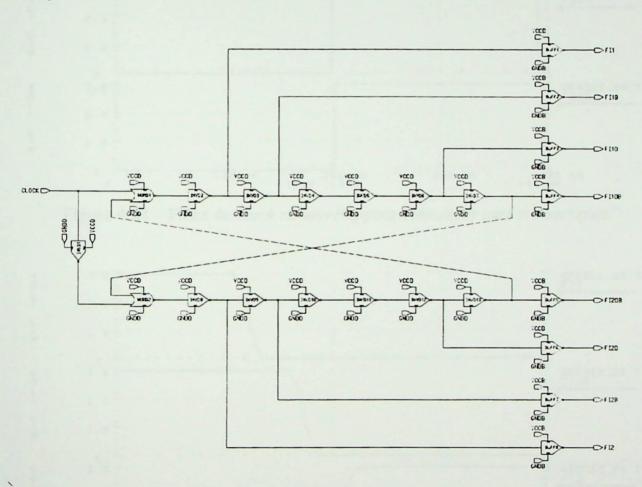

|       | 4.5                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | Gerador de Fases                                     | 59  |

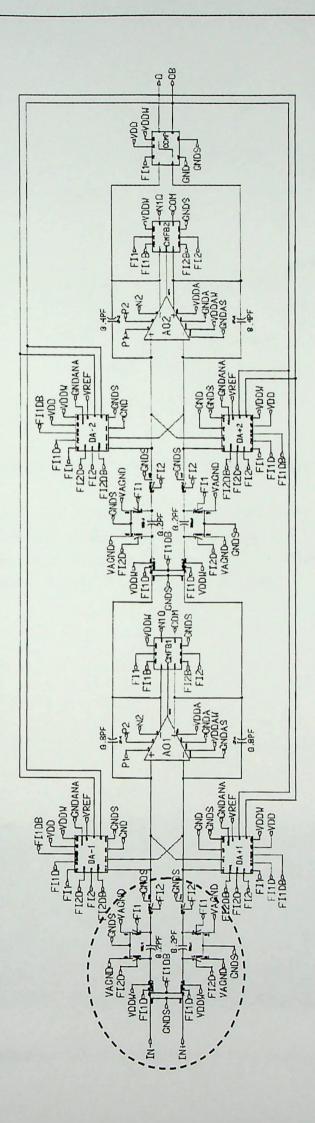

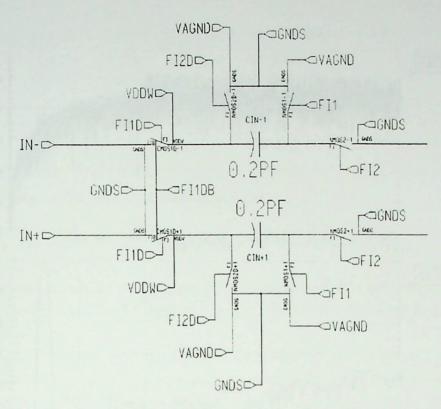

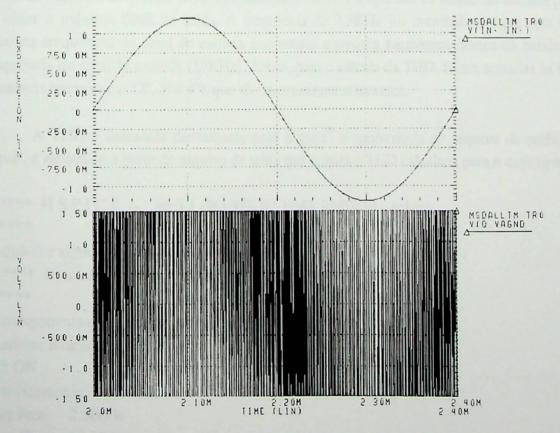

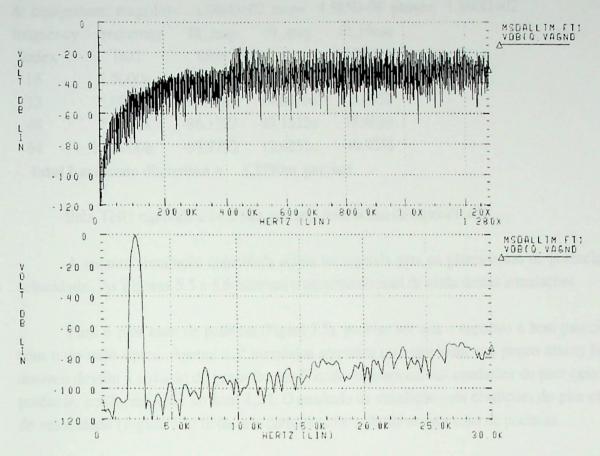

| Capít | ulo 5                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | - Circuito Final                                     |     |

|       | 5.1                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |                                                      | 64  |

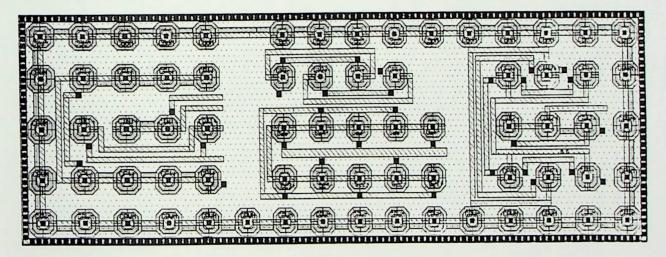

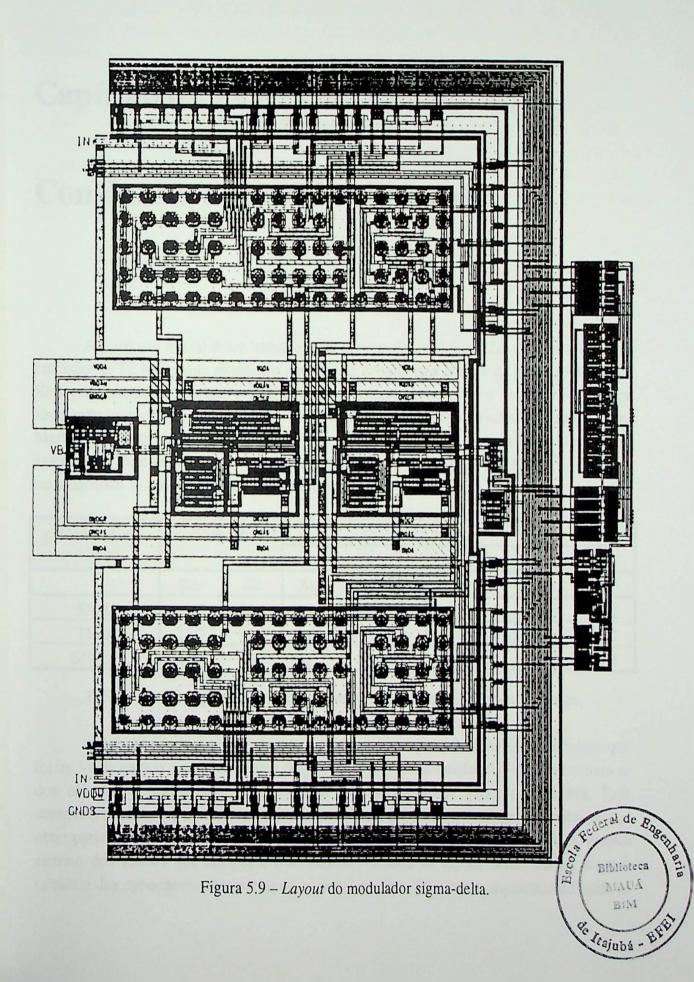

|       |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | Layout                                               | 71  |

|       | The state of the s |                                                      |     |

| Capítulo 6 – Conclusões e Trabalhos Futuros    | 74 |

|------------------------------------------------|----|

| Apêndice A – Rotinas do Matlab®                | 76 |

| Apêndice B – Recomendações para Simulação      | 81 |

| Apêndice C − Descrição do Modulador em Hspice® | 83 |

| Referência Bibliográficas                      | 94 |

# Lista de Figuras

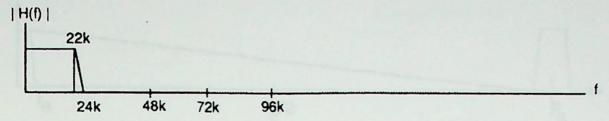

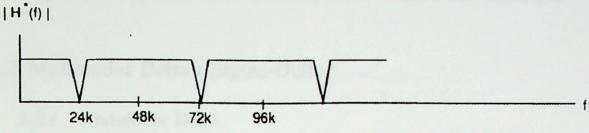

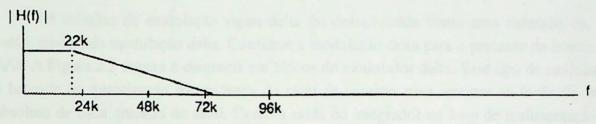

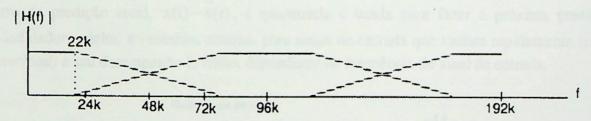

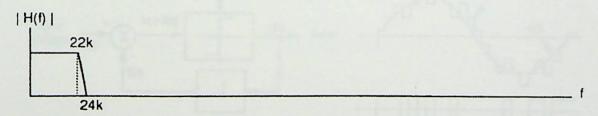

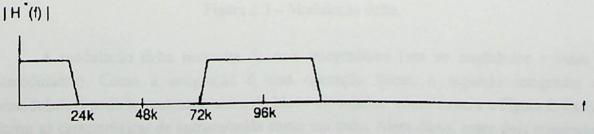

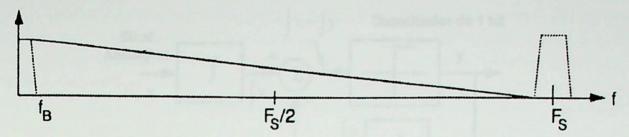

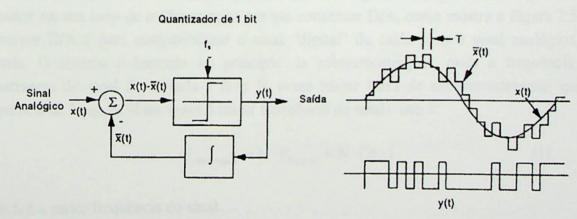

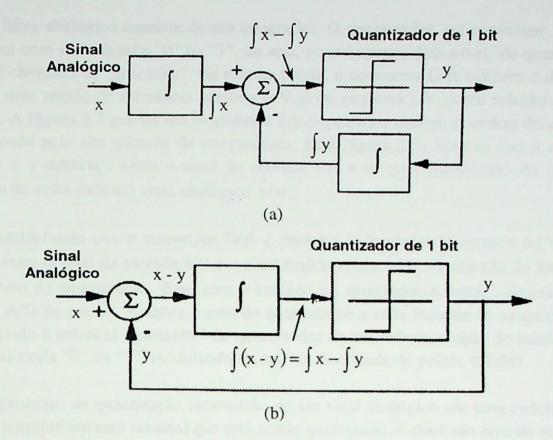

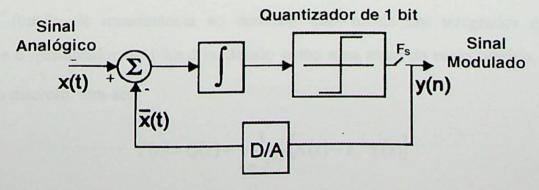

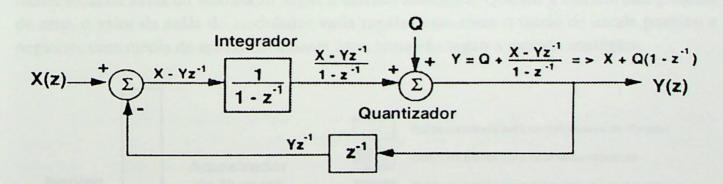

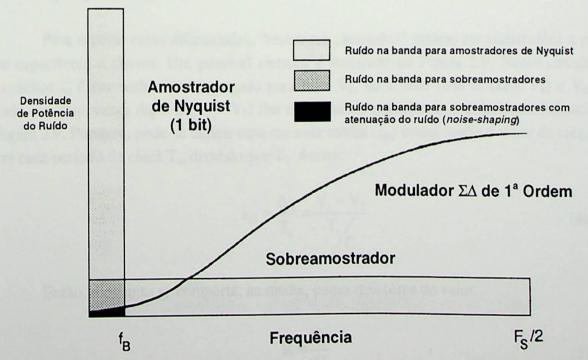

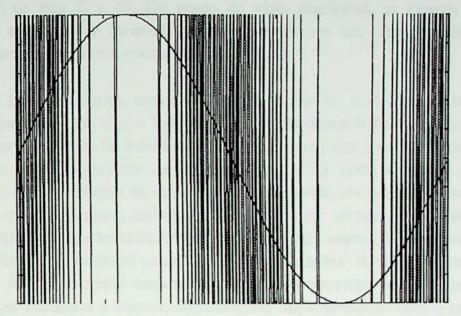

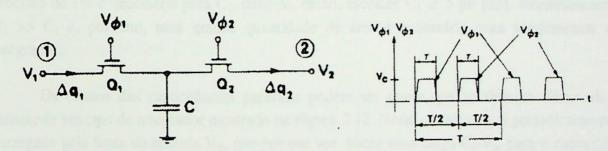

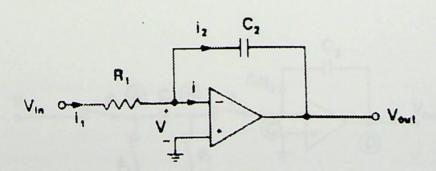

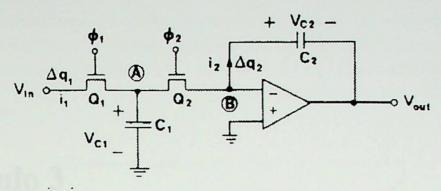

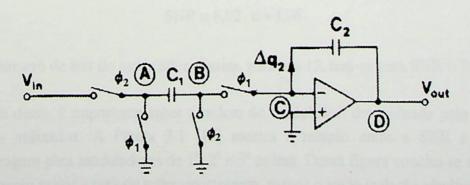

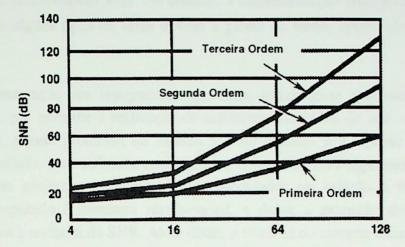

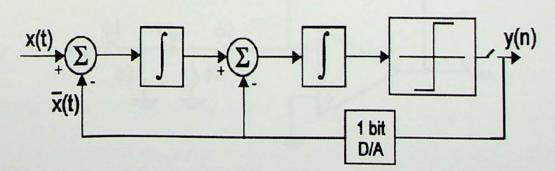

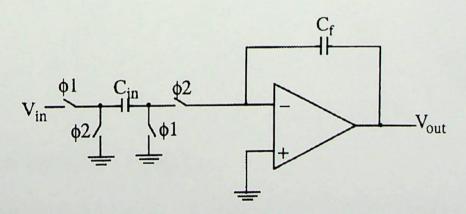

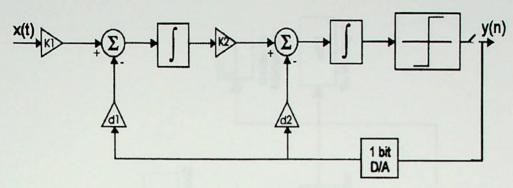

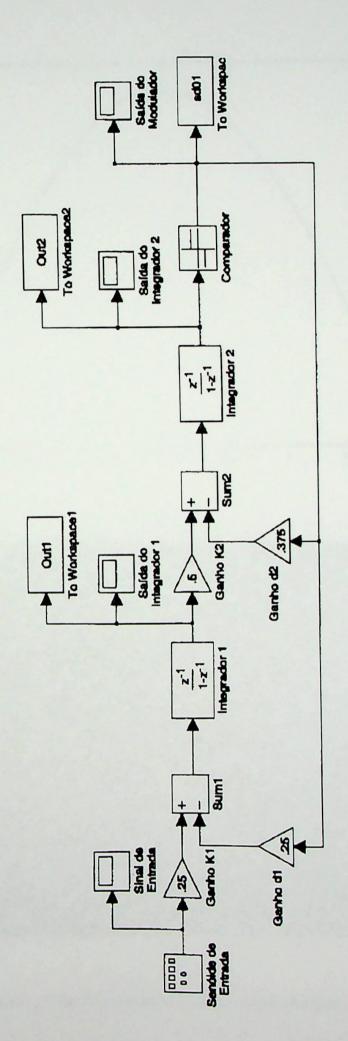

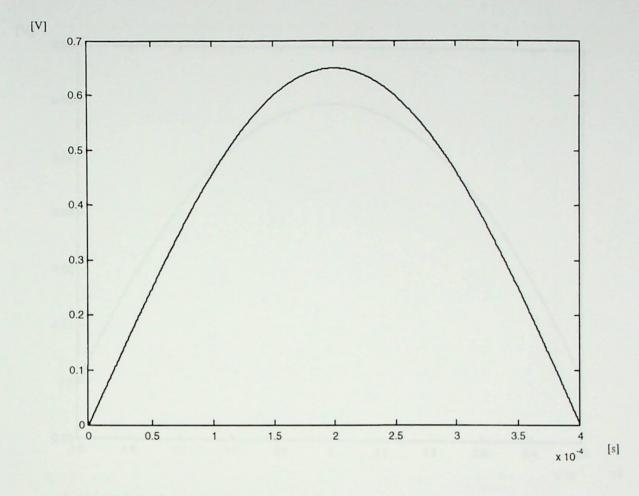

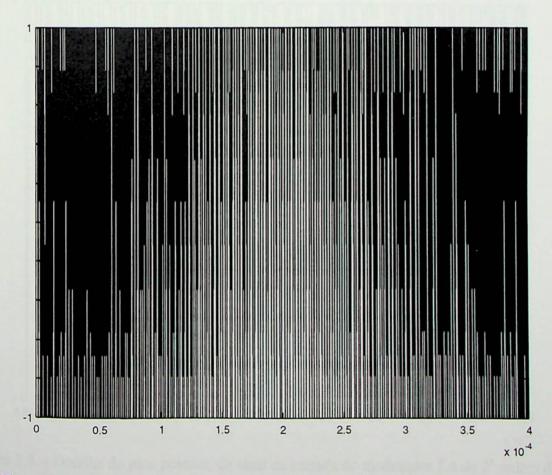

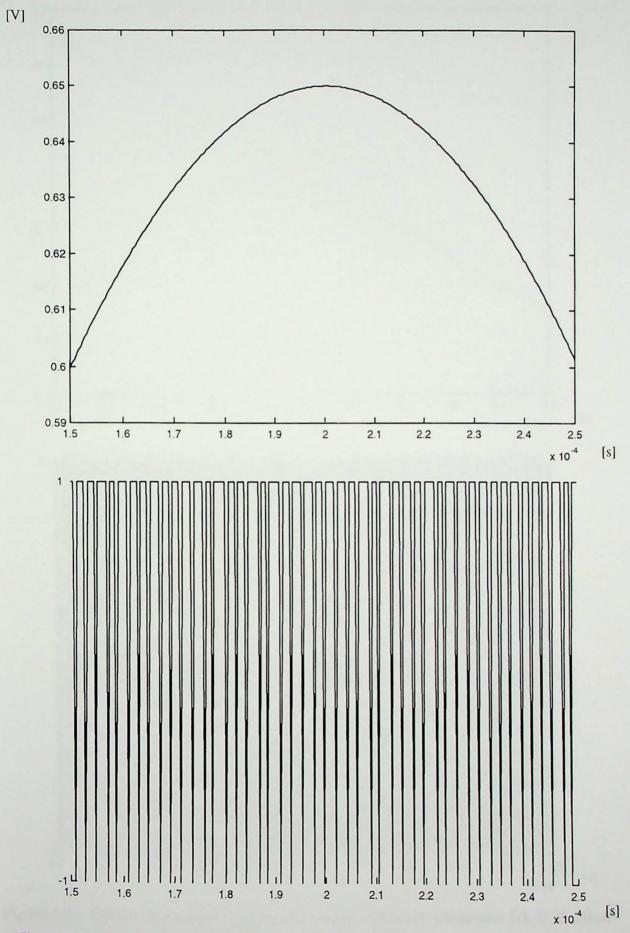

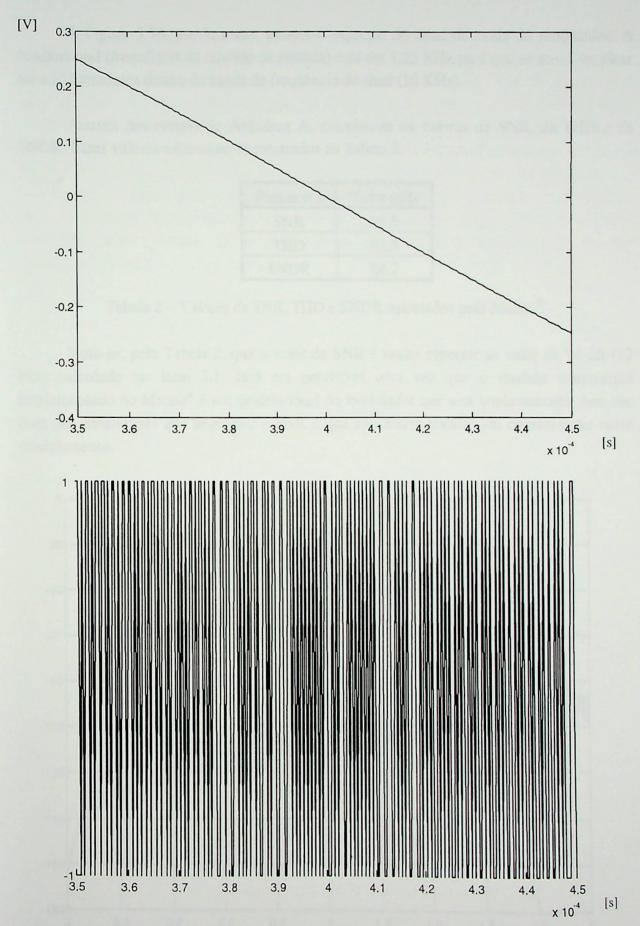

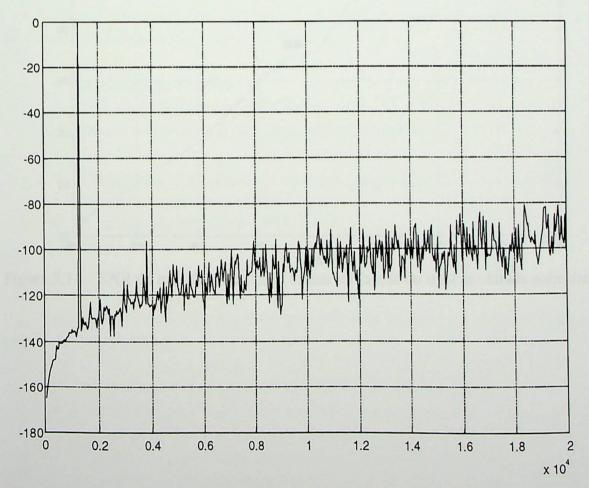

| Figura 2.2 – Resposta do filtro $anti-aliasing$ de conversores de sobreamostragem Figura 2.3 – Modulação delta Figura 2.4 – Modulador $\Sigma\Delta$ a partir do modulador delta Figura 2.5 – Diagrama em blocos de um modulador $\Sigma\Delta$ Figura 2.6 – Análise de um modulador $\Sigma\Delta$ de 1 $^a$ ordem no domínio discreto Figura 2.7 – Espectro de um modulador $\Sigma\Delta$ de 1 $^a$ ordem no domínio discreto Figura 2.8 – Entrada e saída de um modulador $\Sigma\Delta$ de 1 $^a$ ordem Figura 2.9 – Circuito com capacitor chaveado Figura 2.10 – Forma clássica do integrador Figura 2.11 – Integrador com capacitor chaveado Figura 2.12 – Integrador com capacitor chaveado insensível às capacitâncias parasitas  Capítulo 3  Figura 3.1 – SNR versus taxa de sobreamostragem para moduladores sigma-delta Figura 3.2 – Diagrama em blocos de um modulador sigma-delta de 2 $^a$ ordem Figura 3.4 – Amplificador operacional folded-cascode Figura 3.5 – Diagrama em blocos do modulador $\Sigma\Delta$ de 2 $^a$ ordem com os ganhos da arquitetura Figura 3.6 – Diagrama em blocos do modulador $\Sigma\Delta$ de 2 $^a$ ordem utilizado para simulação no Matlab $^{60}$ Figura 3.7 – Entrada e saída do modulador $\Sigma\Delta$ de 2 $^a$ ordem simulado no Matlab $^{60}$ Figura 3.9 – Detalhe da passagem por zero do sinal de entrada do modulador $\Sigma\Delta$ de 2 $^a$ ordem da Figura 3.7 e respectiva saída Figura 3.9 – Detalhe do pico positivo do sinal de entrada do modulador $\Sigma\Delta$ de 2 $^a$ ordem da Figura 3.7 e respectiva saída Figura 3.10 – Espectro do sinal de saída do modulador $\Sigma\Delta$ de 2 $^a$ ordem, calculado no Matlab $^{60}$ Figura 3.10 – Espectro do sinal de saída do modulador $\Sigma\Delta$ de 2 $^a$ ordem, calculado no Matlab $^{60}$ | Capítulo 2                                                                            |     |