**UNIVERSIDADE FEDERAL DE ITAJUBÁ

PROGRAMA DE PÓS-GRADUAÇÃO EM

ENGENHARIA ELÉTRICA**

**Um retificador ativo CMOS de baixa

potência para aplicações biomédicas

implantadas.**

**João Ricardo de Castilho Louzada**

**Itajubá, Fevereiro de 2017**

**UNIVERSIDADE FEDERAL DE ITAJUBÁ

PROGRAMA DE PÓS-GRADUAÇÃO EM

ENGENHARIA ELÉTRICA**

**João Ricardo de Castilho Louzada**

**Um retificador ativo CMOS de baixa

potência para aplicações biomédicas

implantadas.**

Dissertação submetida ao Programa de Pós-Graduação em Engenharia Elétrica como parte dos requisitos para obtenção do Título de Mestre em Ciências em Engenharia Elétrica.

**Área de Concentração: Microeletrônica**

**Orientador: Robson Luiz Moreno

Coorientador: Leonardo B. Zoccal**

**Fevereiro de 2017

Itajubá - MG**

**UNIVERSIDADE FEDERAL DE ITAJUBÁ

PROGRAMA DE PÓS-GRADUAÇÃO EM

ENGENHARIA ELÉTRICA**

**Um retificador ativo CMOS de baixa

potência para aplicações biomédicas

implantadas.**

**João Ricardo de Castilho Louzada**

Dissertação aprovada por banca examinadora em

17 de fevereiro de 2017, conferindo ao autor o

título de **Mestre em Ciências em Engenharia

Elétrica**.

***Banca Examinadora:***

Prof. Dr. Robson Luiz Moreno

Prof. Dr. Leonardo Bresegħello Zoccal

Prof. Dr. Leonardo Mesquita

Prof. Dr. Gustavo Colletta

**Itajubá

2017**

*"O homem inteligente reflete sobre as palavras dos sábios e, com ouvido atento, deseja sabedoria."*

(Eccl 3, 31)

# Agradecimentos

Agradecimentos.

Quero agradecer aos professores Prof. Gustavo Colletta e Prof. Odilon Dutra pelas incontáveis ajudas com *layout*, simulações, medições e dúvidas tiradas durante todo o desenvolvimento deste trabalho.

Ao Prof. Tales Pimenta meu muito obrigado pelo apoio com nosso artigo que provavelmente não teria sido apresentado sem sua ajuda.

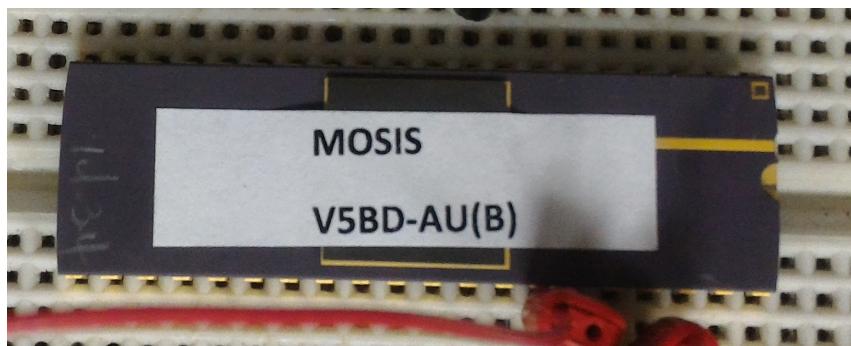

Agradeço a CAPES que através da disponibilidade de bolsas de mestrado viabilizou financeiramente este trabalho. Agradeço também a MOSIS que por meio de seu programa educacional MOSIS (MEP) viabilizou a fabricação do retificador descrito neste trabalho durante a fase de estudos.

Aos meus orientadores Prof. Robson Moreno e Prof. Leonardo Zoccal não tenho como ser mais grato por me conduzirem durante todo esse tempo, pelas infinitas reuniões, ajuda, e e-mails respondidos. Muitíssimo Obrigado!

Por fim, agradeço aos meus pais, José Louzada e Adalice Louzada, não só pelo apoio durante o tempo dessa pós-graduação, mas por toda a vida que me deram e me permitiram ter.

Muito obrigado a todos.

# Resumo

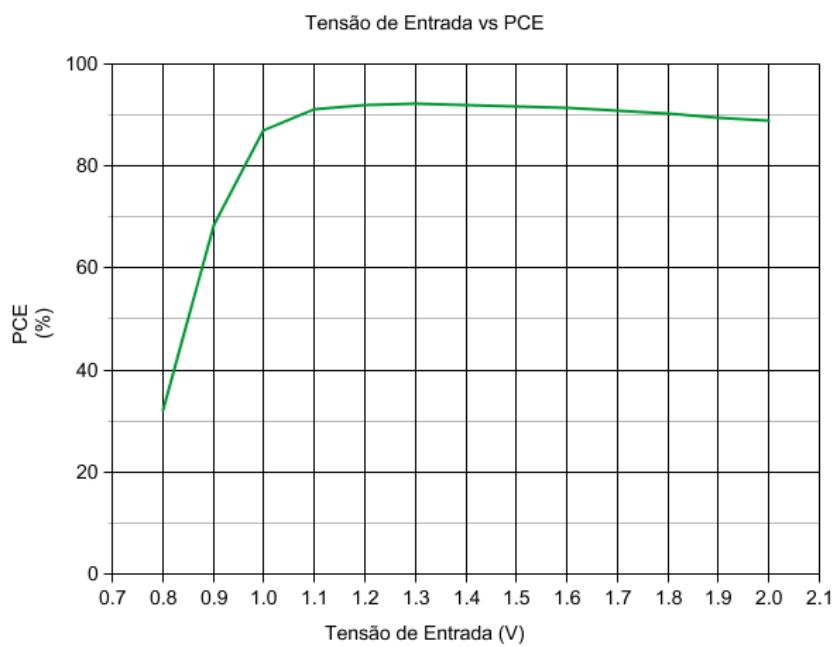

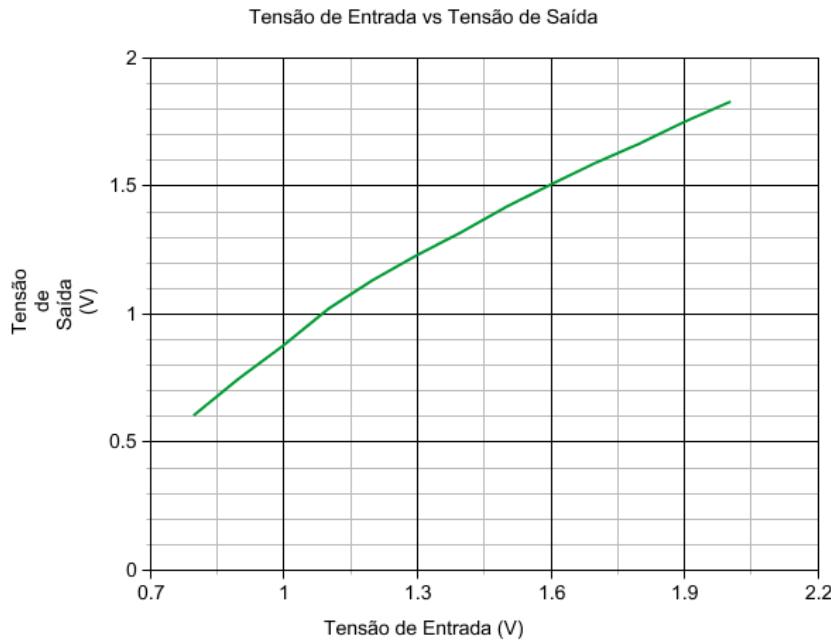

Este trabalho apresenta o desenvolvimento de um retificador ativo CMOS de baixa potência projetado para fornecer alimentação elétrica a circuitos biomédicos que estejam implantados. Apesar do retificador poder ser facilmente aplicado em outras finalidades, todos os detalhes do projeto como tipo de enlace eletromagnético, tipo de retificador e frequência de operação foram pensados para aplicações implantadas. O retificador ativo utiliza comparadores que aceleram o chaveamento dos transistores do retificador e reduzem assim as perdas causadas pela corrente reversa originada pela baixa velocidade de chaveamento dos transistores MOS conectados como diodos. O tipo de comparador proposto e utilizado nesta aplicação foi resultado do estudo feito com outros comparadores já empregados em aplicações semelhantes. Desenvolvido em processo Digital IBM 130-nm e projetado para operar na frequência de 13,56MHz, todo o projeto apresentou rendimento acima da média encontrada em publicações atuais. A eficiência PCE máxima é de 92% e o retificador consegue entregar uma tensão de saída de 1,233V para uma tensão de entrada de 1,3V.

**Palavras Chaves:** Retificador, Retificador Ativo, Comparador, PCE.

# Abstract

This work presents a development of a low power CMOS active rectifier designed to supply implanted biomedical circuits. Despite the rectifier can be used in another application with others goals, all the details like electromagnetic link, kind of rectifier type and operational frequency were designed for implanted applications. The active rectifier make use of comparators to speed up the ON-OFF switch of the rectifier's transistors and decreases the loss caused by the reverse current originated from the low switch speed of the MOS transistors connected as diodes. The proposed rectifier is a result of the study among others comparators already used in similar applications. Developed in IBM 130-nm process and designed to work at 13,56MHz, the project showed to be more efficient than the average yield found in current publications. The maximum PCE efficiency is 92% and the rectifier can delivery an output voltage of 1.233V from an 1.3V input voltage.

**Key-words:** Rectifier, Active Rectifier, Comparator, PCE.

# Lista de ilustrações

|                                                                                                                                                       |    |

|-------------------------------------------------------------------------------------------------------------------------------------------------------|----|

| Figura 1 – Esquemático do sistema de captação de energia RF e conversão para DC. . . . .                                                              | 19 |

| Figura 2 – Esquema de funcionamento de um dispositivo TEG. . . . .                                                                                    | 21 |

| Figura 3 – Regiões de Fresnel e Fraunhofer em uma antena radiante. . . . .                                                                            | 22 |

| Figura 4 – Circuito equivalente de um sistema RFID utilizando acoplamento indutivo. . . . .                                                           | 22 |

| Figura 5 – Diagrama conceitual de um link de potencia capacitivo implantado. . . . .                                                                  | 24 |

| Figura 6 – Consumo de potência de implantes vs velocidade de transmissão de dados relatados em trabalhos prévios. . . . .                             | 30 |

| Figura 7 – Tradicional retificador de onda completa construído com ponte de diodos. . . . .                                                           | 32 |

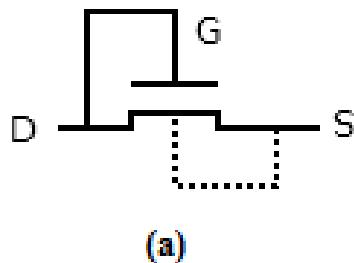

| Figura 8 – Transistores CMOS conectados para trabalhar como diodos. (a) NMOS, (b) PMOS. . . . .                                                       | 33 |

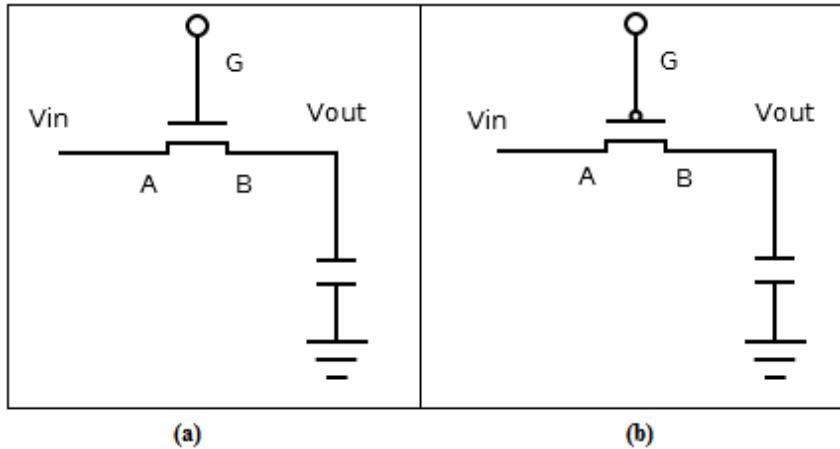

| Figura 9 – Circuitos esquemáticos de funcionamento dos transistores NMOS (a) e PMOS (b). . . . .                                                      | 34 |

| Figura 10 – Esquema de retificador em ponte utilizando transistores CMOS como diodos. . . . .                                                         | 35 |

| Figura 11 – Retificador com cancelamento de $V_{th}$ por fonte externa. . . . .                                                                       | 36 |

| Figura 12 – Retificador com auto cancelamento de $V_{th}$ . . . . .                                                                                   | 37 |

| Figura 13 – Esquema de retificador Cross-Coupled. . . . .                                                                                             | 38 |

| Figura 14 – Esquemático de um único estágio do multiplicador de tensão Dickson Charge Pump. . . . .                                                   | 38 |

| Figura 15 – Forma de onda do funcionamento de um retificador Cross-Coupled com destaque para a corrente reversa. . . . .                              | 40 |

| Figura 16 – Esquema de retificador ativo utilizando comparadores. . . . .                                                                             | 40 |

| Figura 17 – (a) Retificador 1X/2X Reconfigurável, (b) Modo 1X, (c) Modo 2X. . . . .                                                                   | 42 |

| Figura 18 – Comparador <i>Two-input Common-gate</i> . . . . .                                                                                         | 44 |

| Figura 19 – Esquemático de funcionamento do comparador <i>Two-input Common-gate</i> . . . . .                                                         | 44 |

| Figura 20 – Comparador apresentado em (33) . . . . .                                                                                                  | 45 |

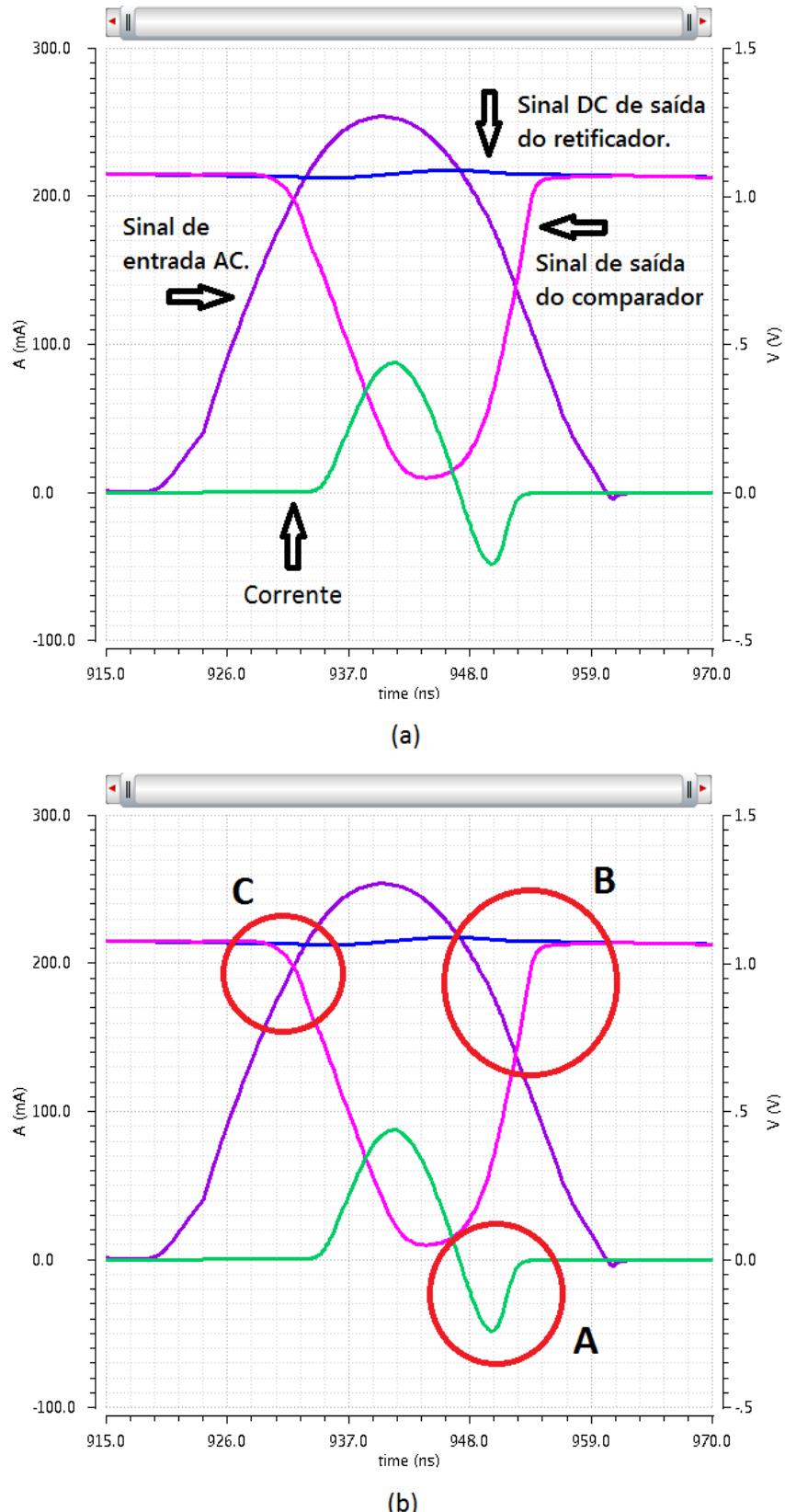

| Figura 21 – Forma de onda de um retificador com comparadores. (a) designação das curvas, (b) destaque para atrasos e corrente reversa. . . . .        | 46 |

| Figura 22 – Comparador Proposto . . . . .                                                                                                             | 47 |

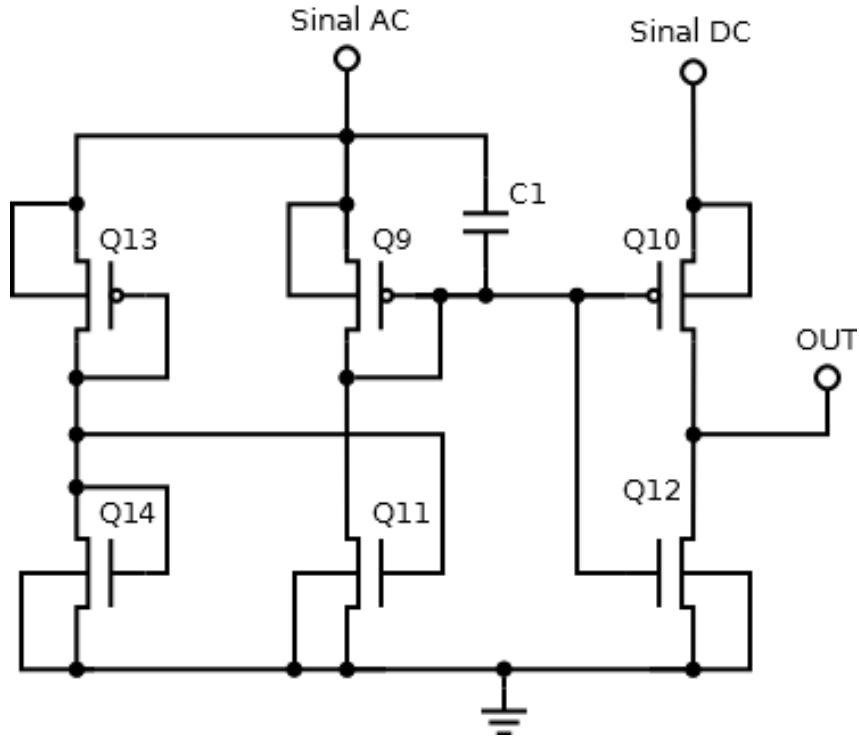

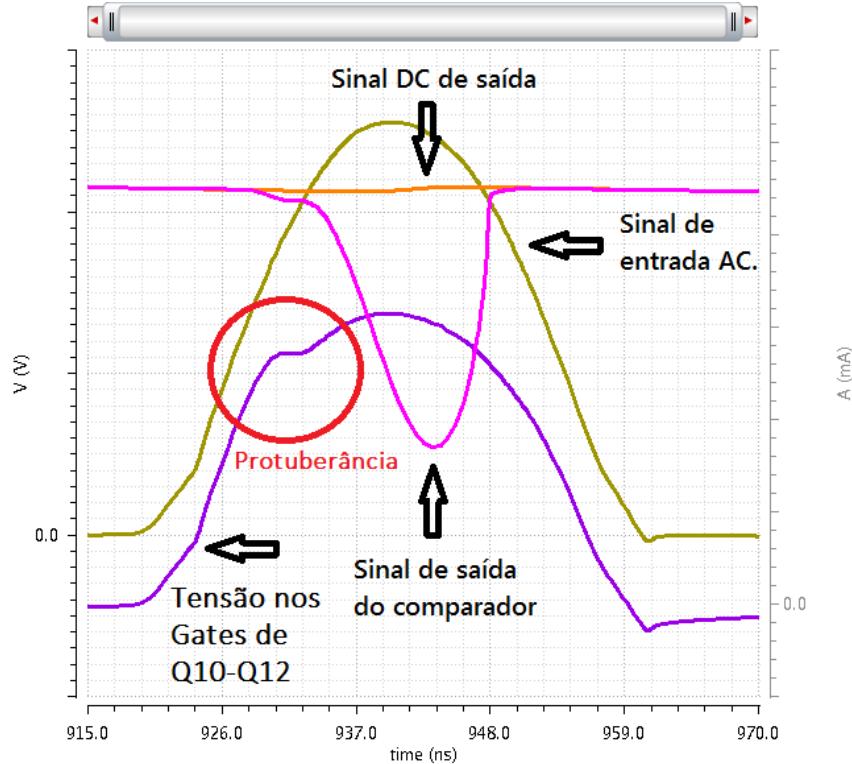

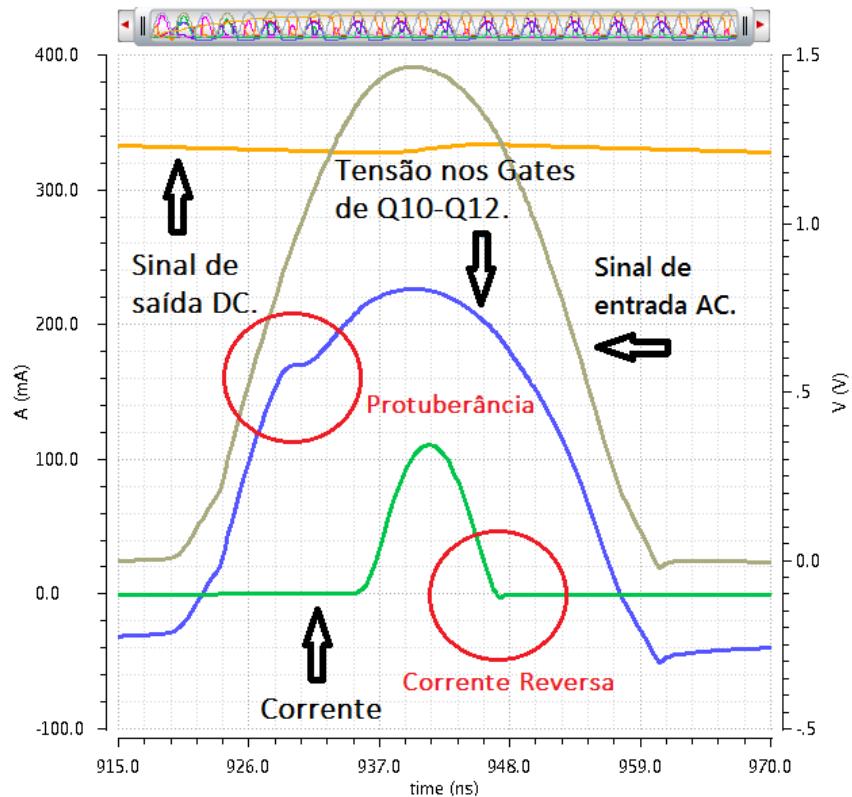

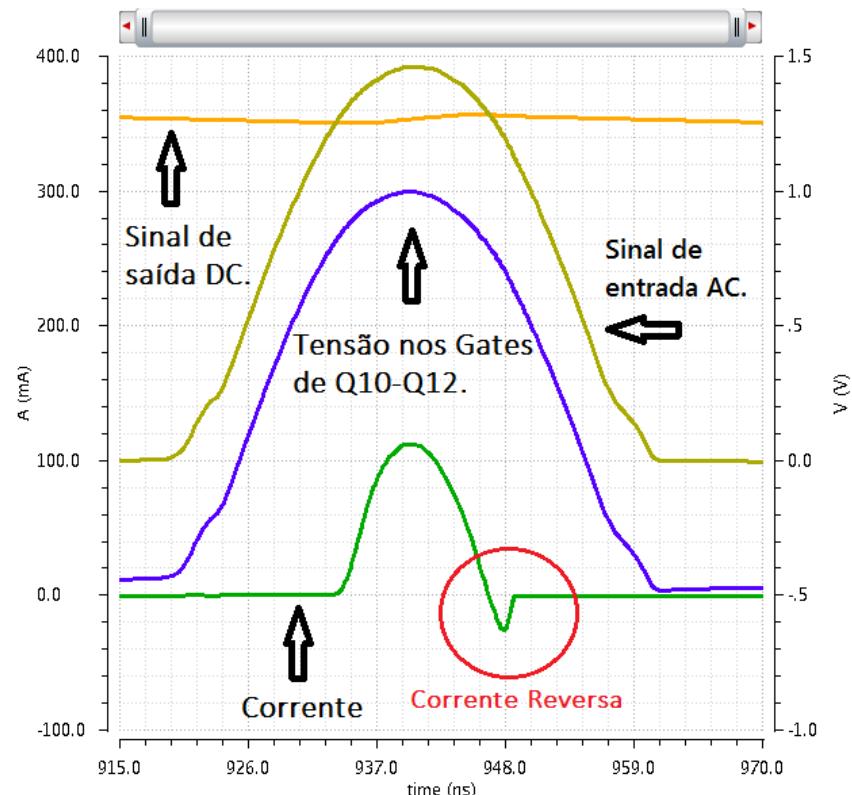

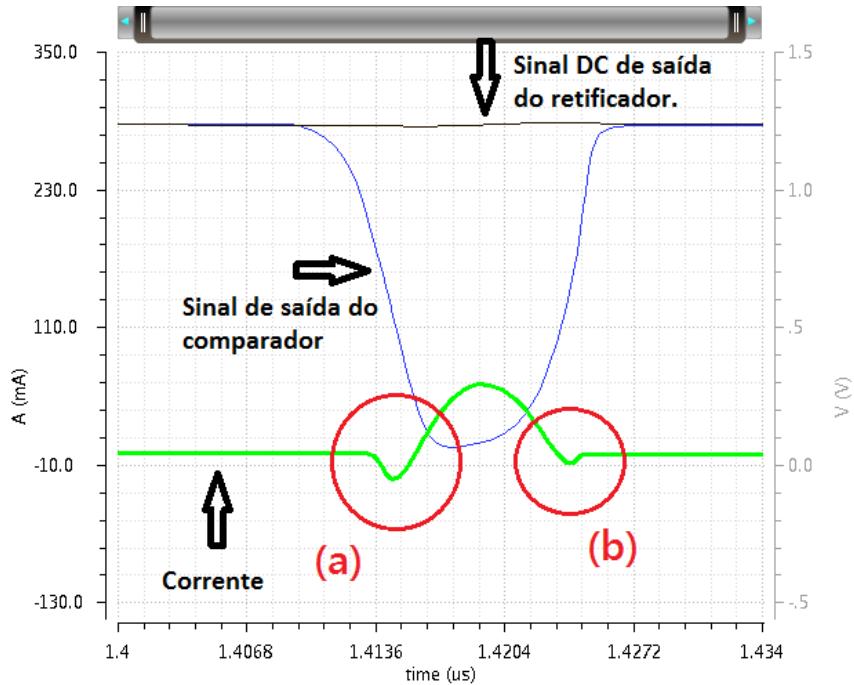

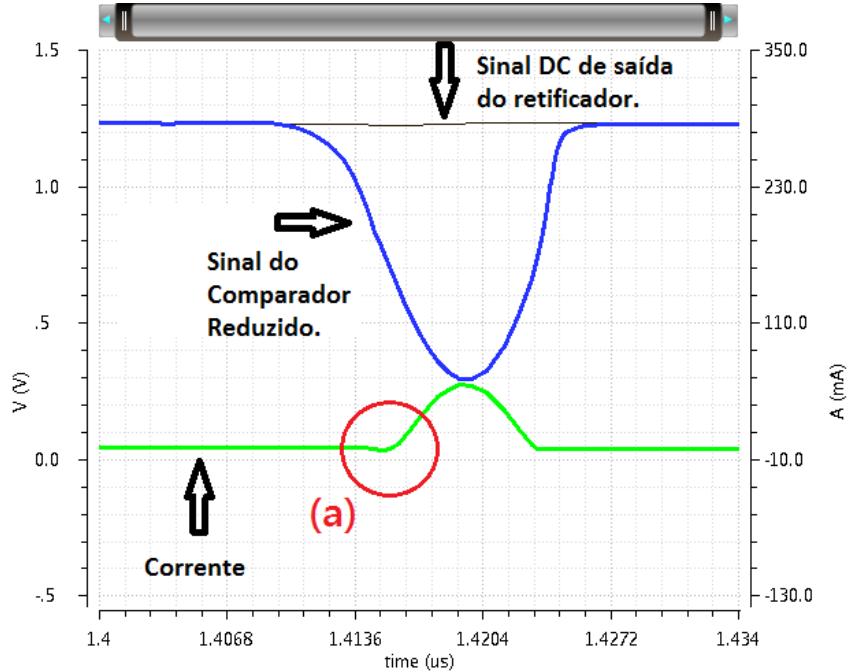

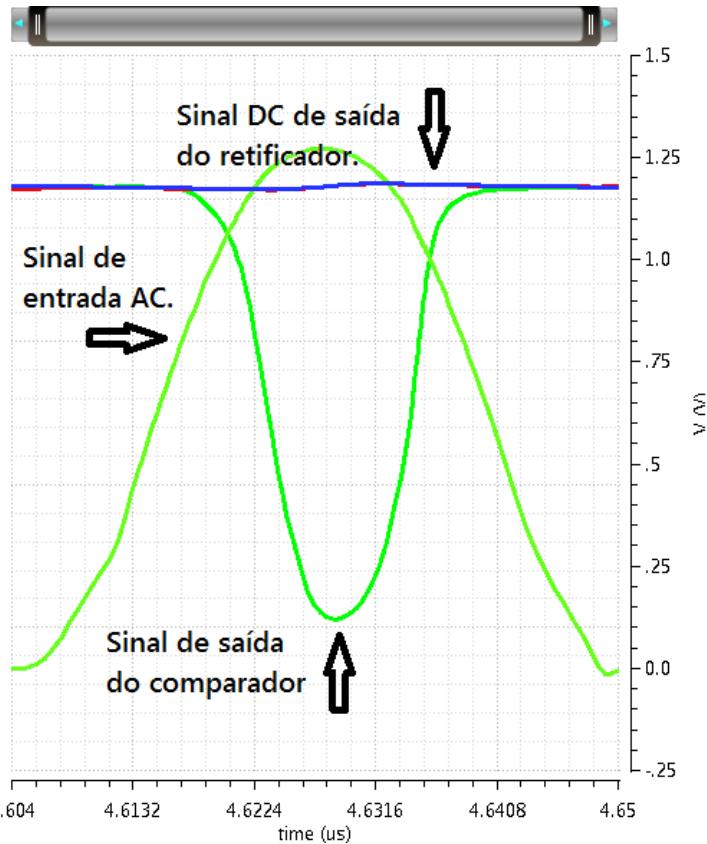

| Figura 23 – Forma de onde do comparador com destaque para a protuberância do sinal do divisor de tensão. . . . .                                      | 48 |

| Figura 24 – Comparação de formas de onda utilizando (a) capacitor $C_1$ de valor adequado, (b) capacitor $C_1$ de valor acima do ponto ótimo. . . . . | 51 |

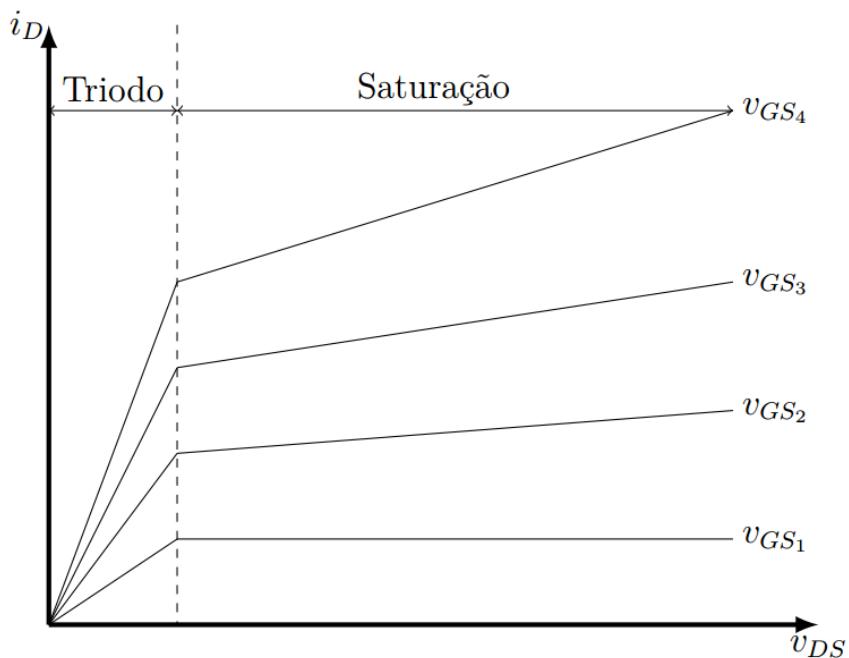

| Figura 25 – Inclinação nas curvas $V_{ds}$ x $I_d$ devido ao estreitamento do canal. . . . .                                                          | 53 |

|                                                                                                                                                                           |    |

|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----|

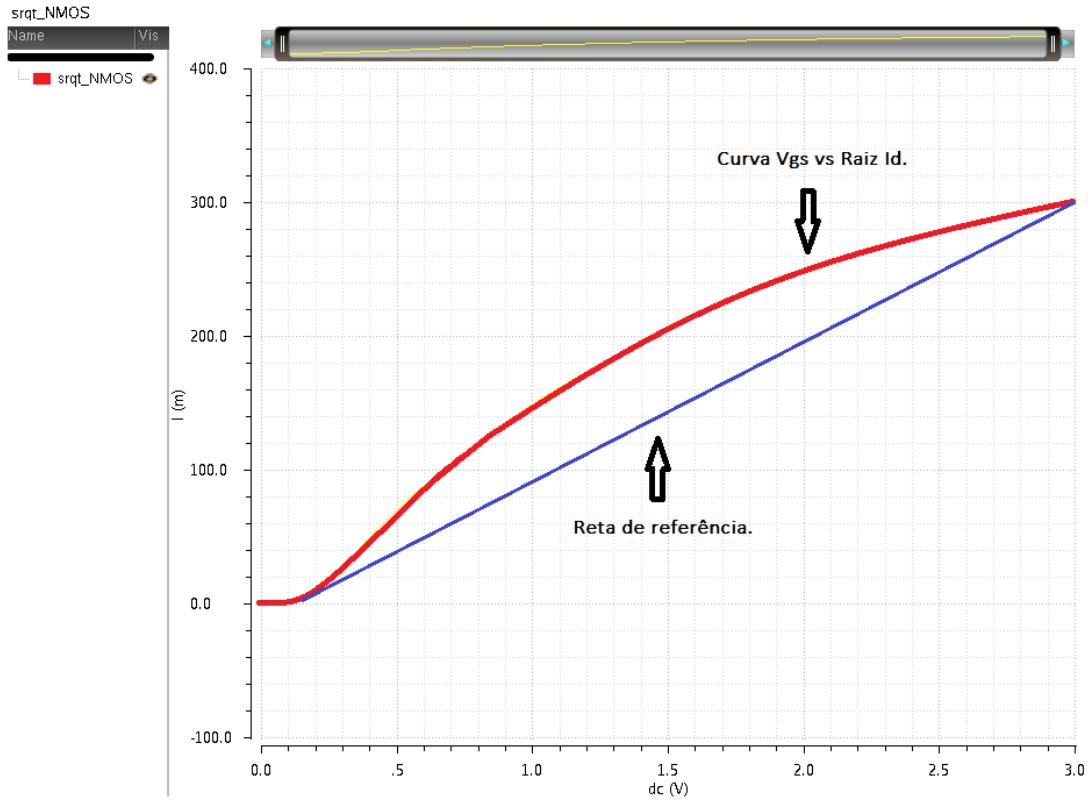

| Figura 26 – Gráfico de $V_{gs}$ vs $\sqrt{Id}$ para o transistor NMOS acompanhado de reta de referência para comparação com a curva. . . . .                              | 54 |

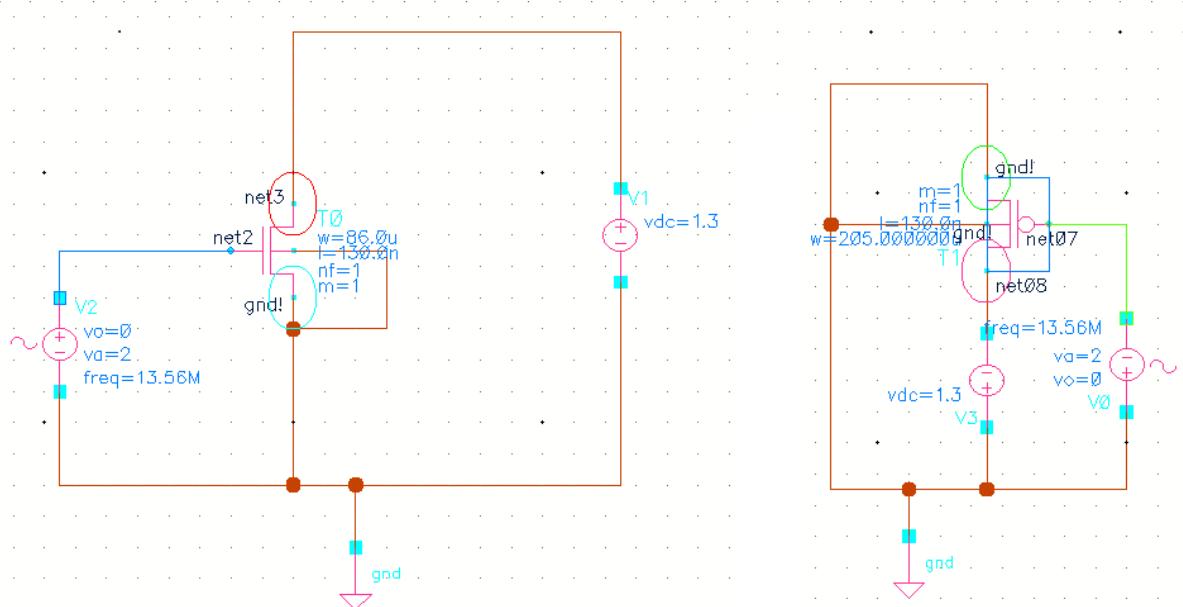

| Figura 27 – Circuitos de polarização e caracterização do transistor NMOS (esquerda) e PMOS (direita). . . . .                                                             | 54 |

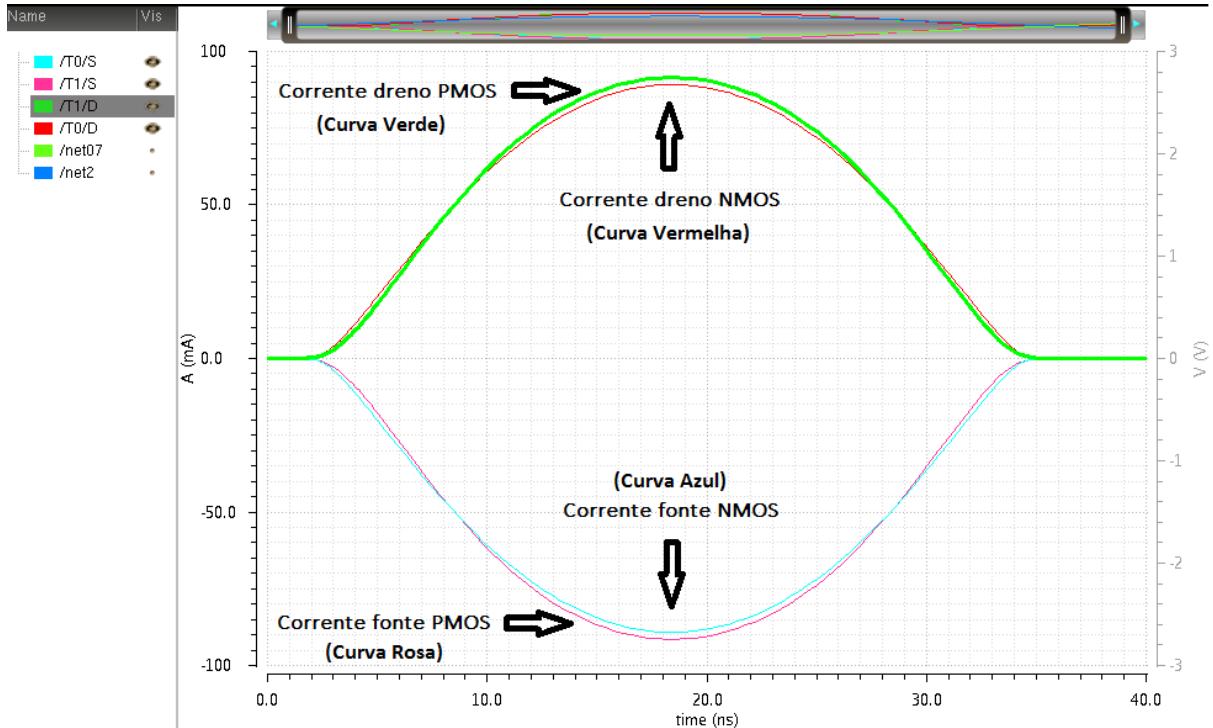

| Figura 28 – Curva de correntes de caracterização dos transistores PMOS e NMOS. .                                                                                          | 55 |

| Figura 29 – Esquemático do circuito de polarização de corpo dinâmica. . . . .                                                                                             | 56 |

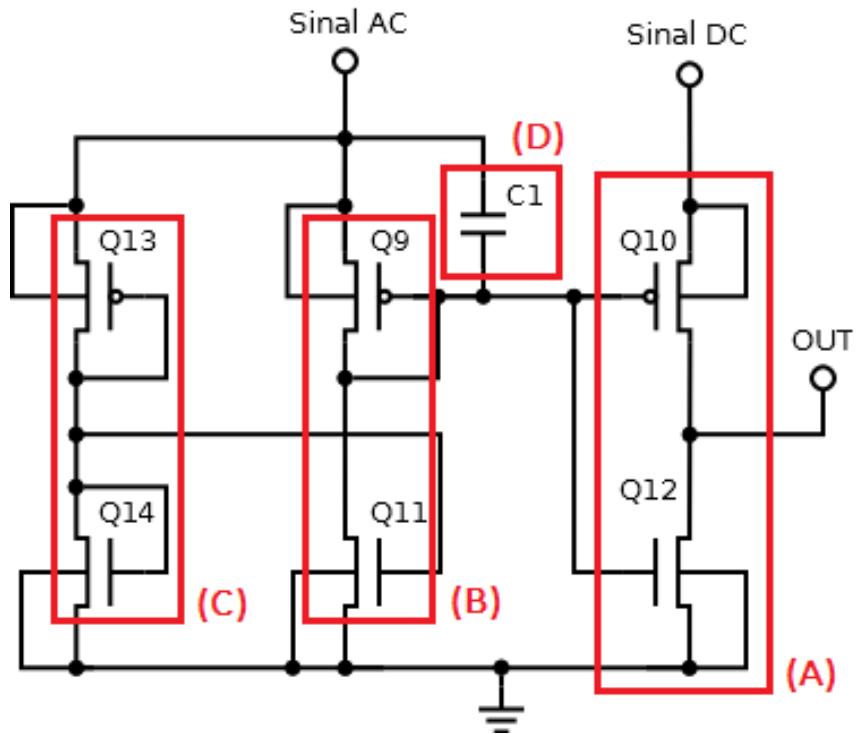

| Figura 30 – Comparador proposto com destaque para as quatro partes: (A) Inversor, (B) divisor de tensão principal, (C) divisor de tensão auxiliar, (D) capacitor. . . . . | 58 |

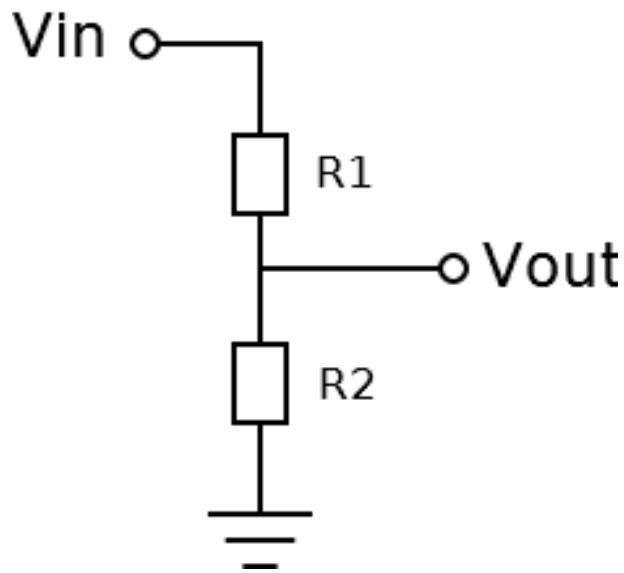

| Figura 31 – Divisor de tensão. . . . .                                                                                                                                    | 59 |

| Figura 32 – Divisor de tensão com fuga de corrente simbolizada pela resistência $R_3$ . .                                                                                 | 60 |

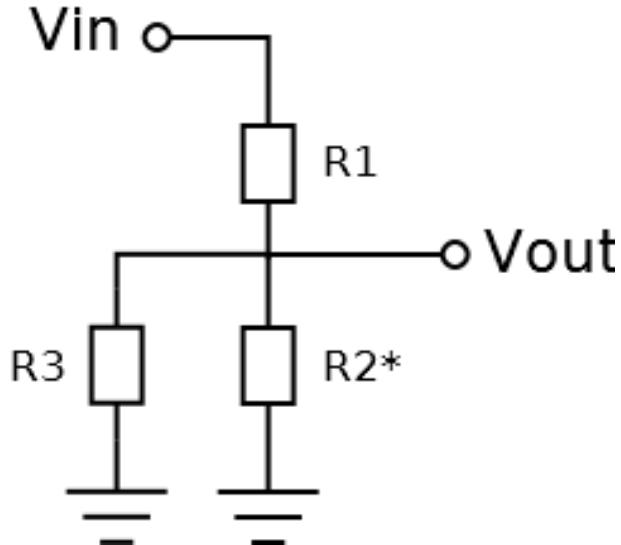

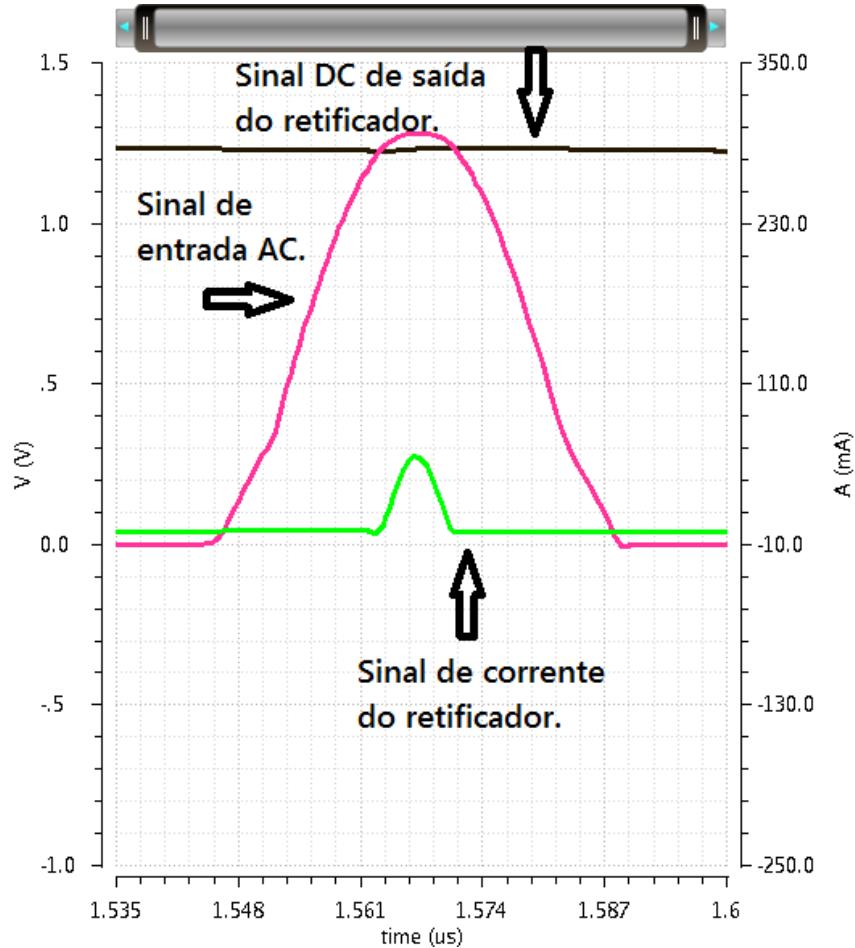

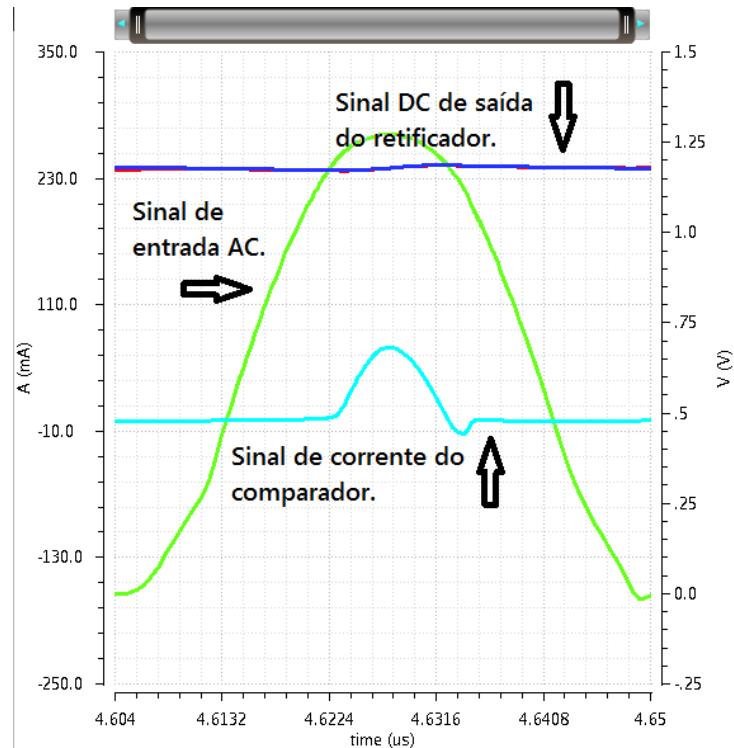

| Figura 33 – Forma de onda da corrente do retificador. (a) Corrente reversa de início de ciclo, (b) corrente reversa de final de ciclo. . . . .                            | 62 |

| Figura 34 – Forma de onda da corrente do retificador e sinal de tensão da saída do comparador. (a) Corrente reversa de início de ciclo . . . . .                          | 62 |

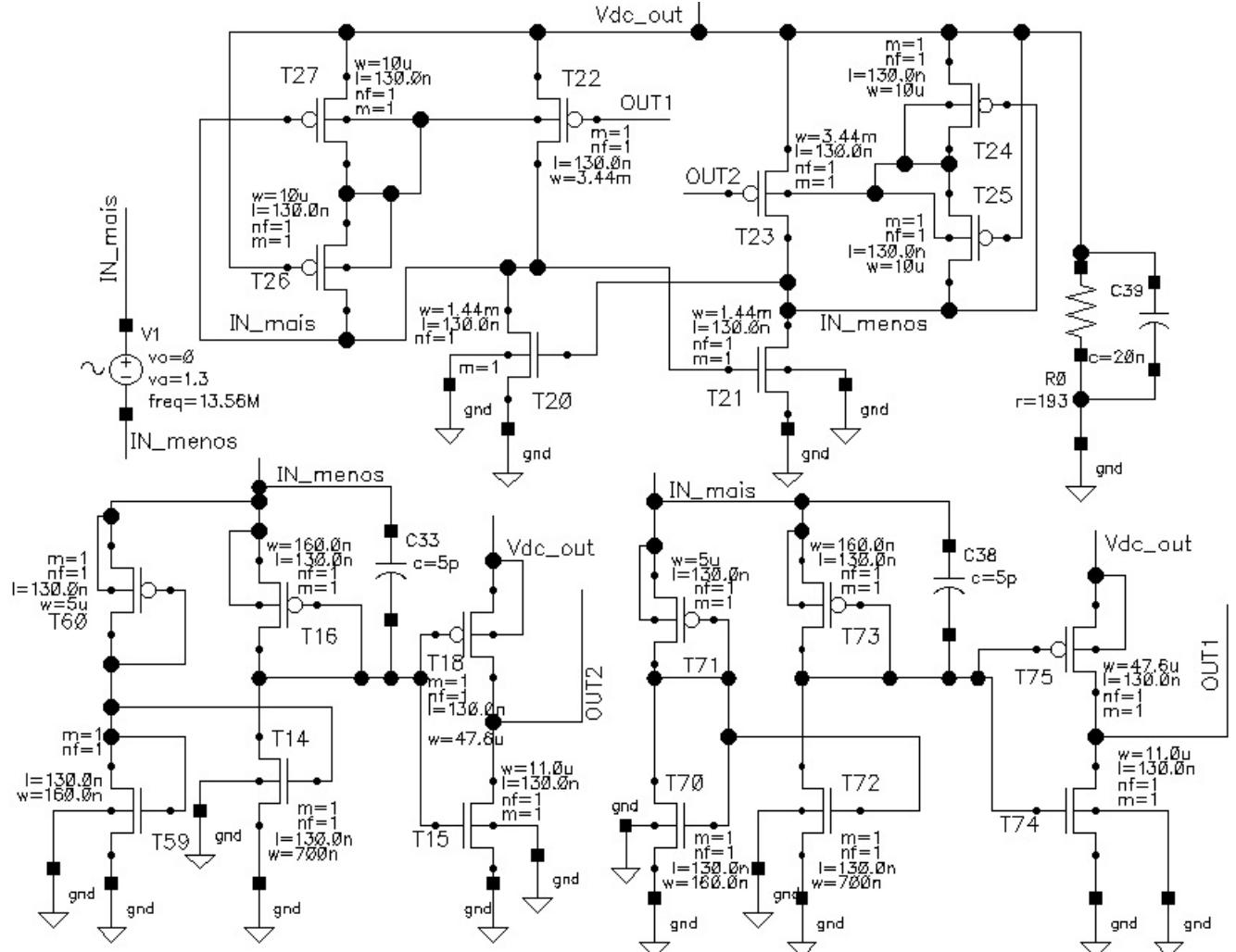

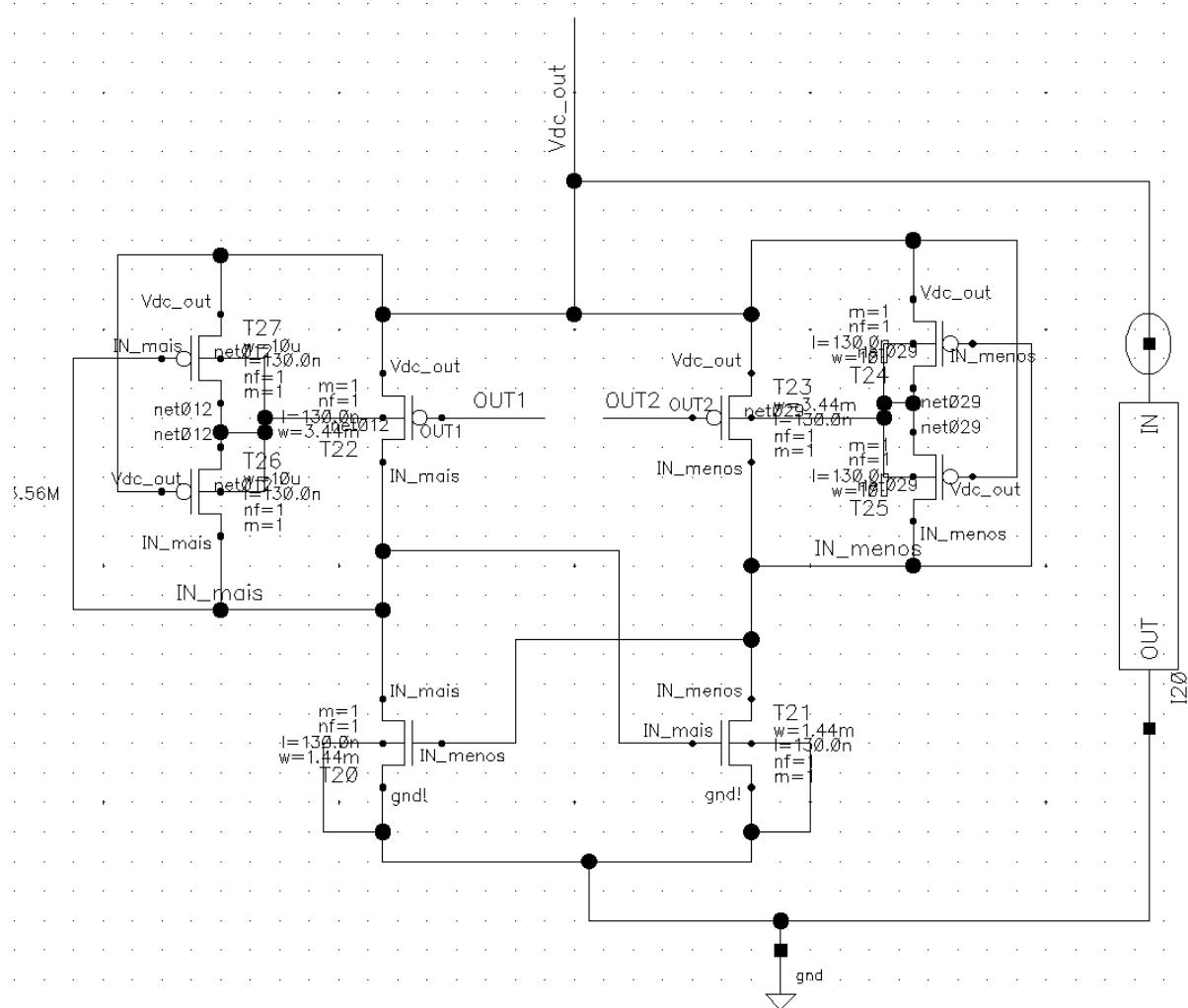

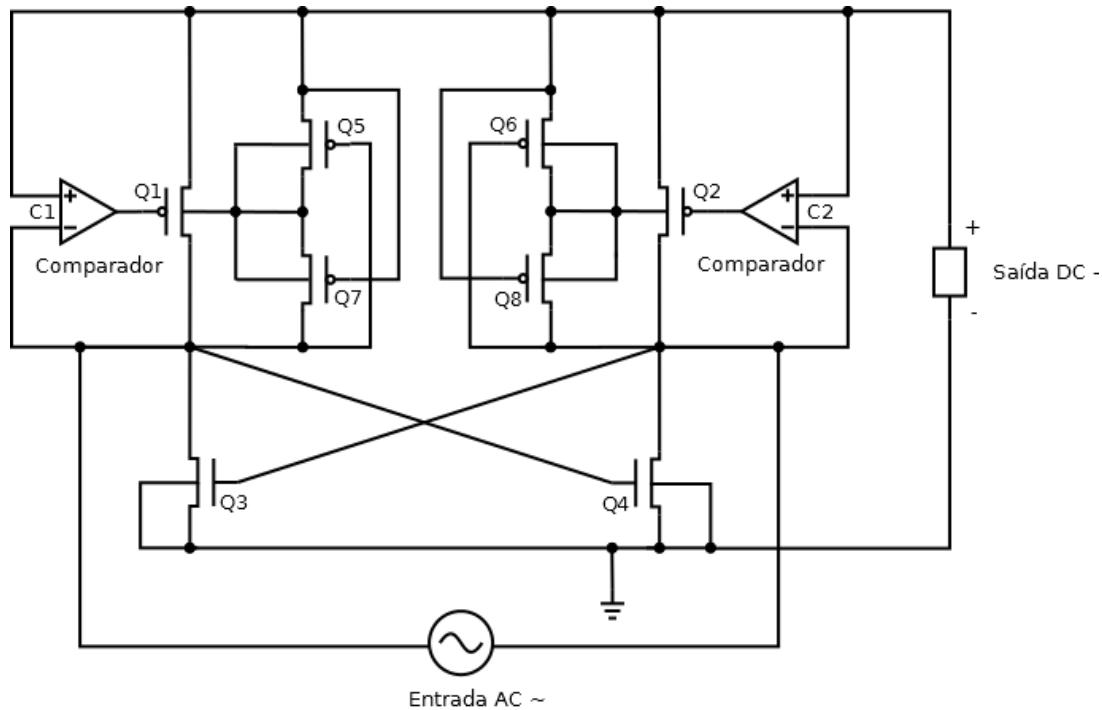

| Figura 35 – Circuito completo do Retificador utilizando dois comparadores propostos. .                                                                                    | 63 |

| Figura 36 – Circuito do Retificador sem os comparadores. . . . .                                                                                                          | 64 |

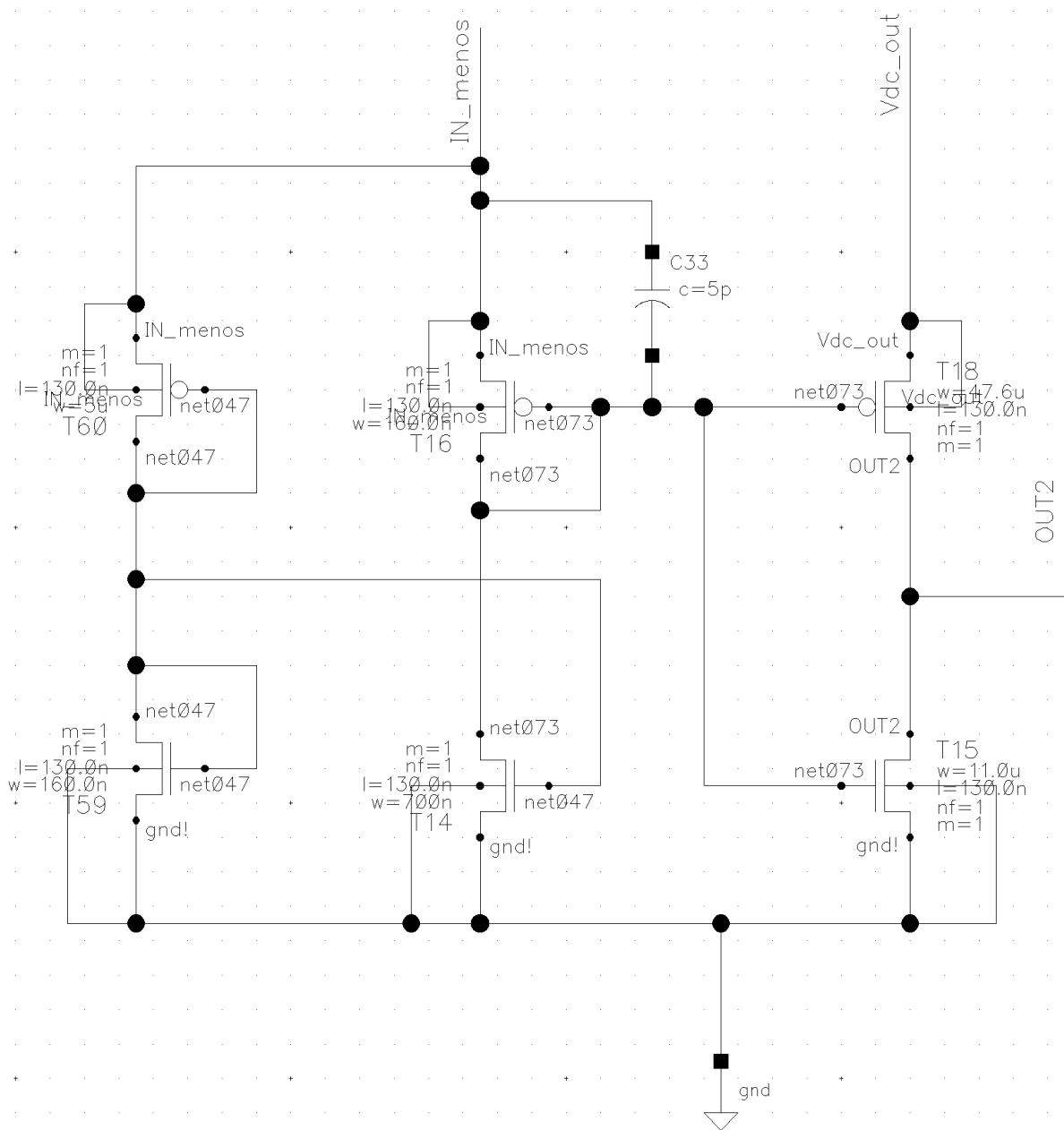

| Figura 37 – Circuito completo Comparador 1. . . . .                                                                                                                       | 65 |

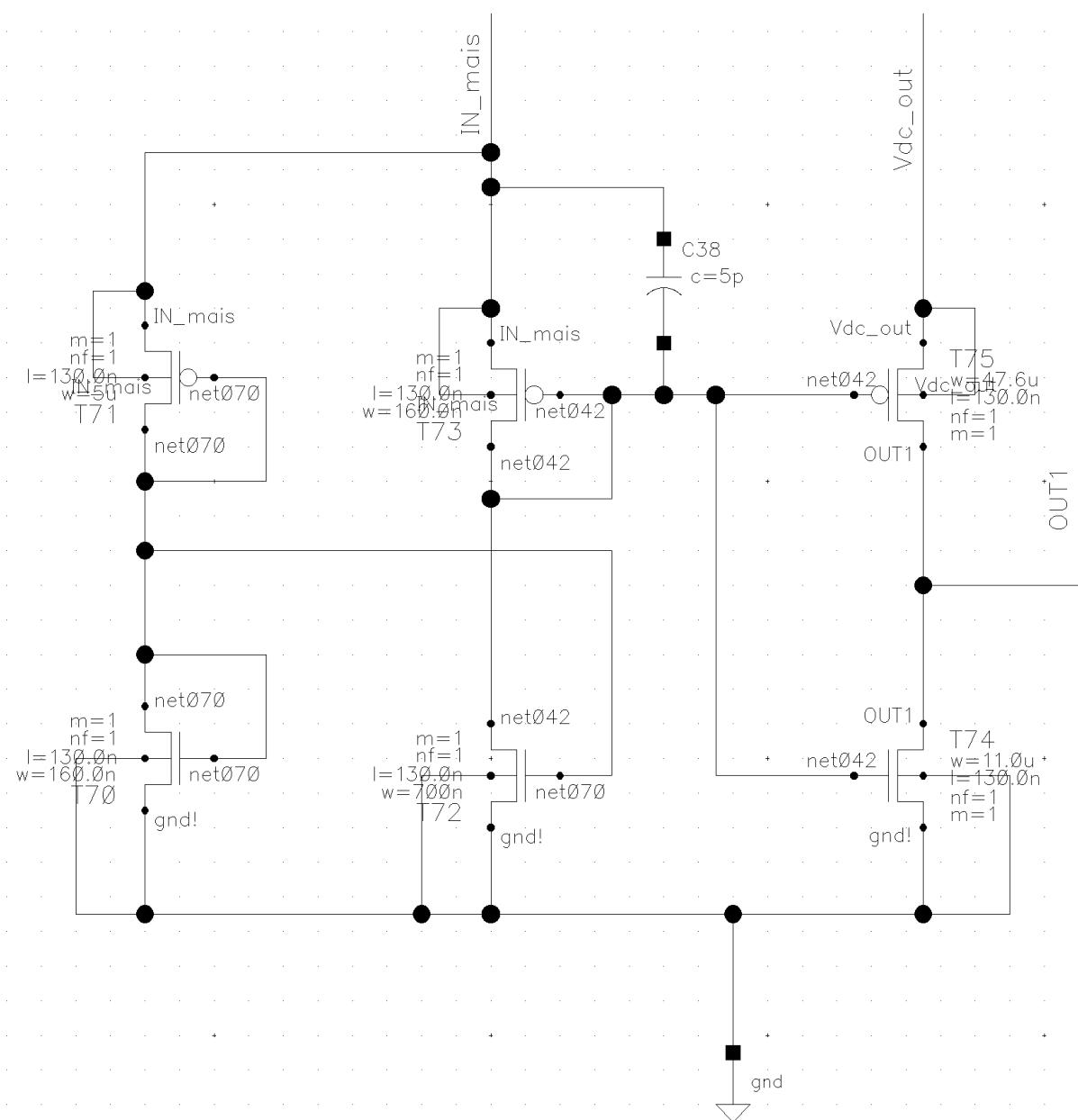

| Figura 38 – Circuito completo Comparador 2. . . . .                                                                                                                       | 66 |

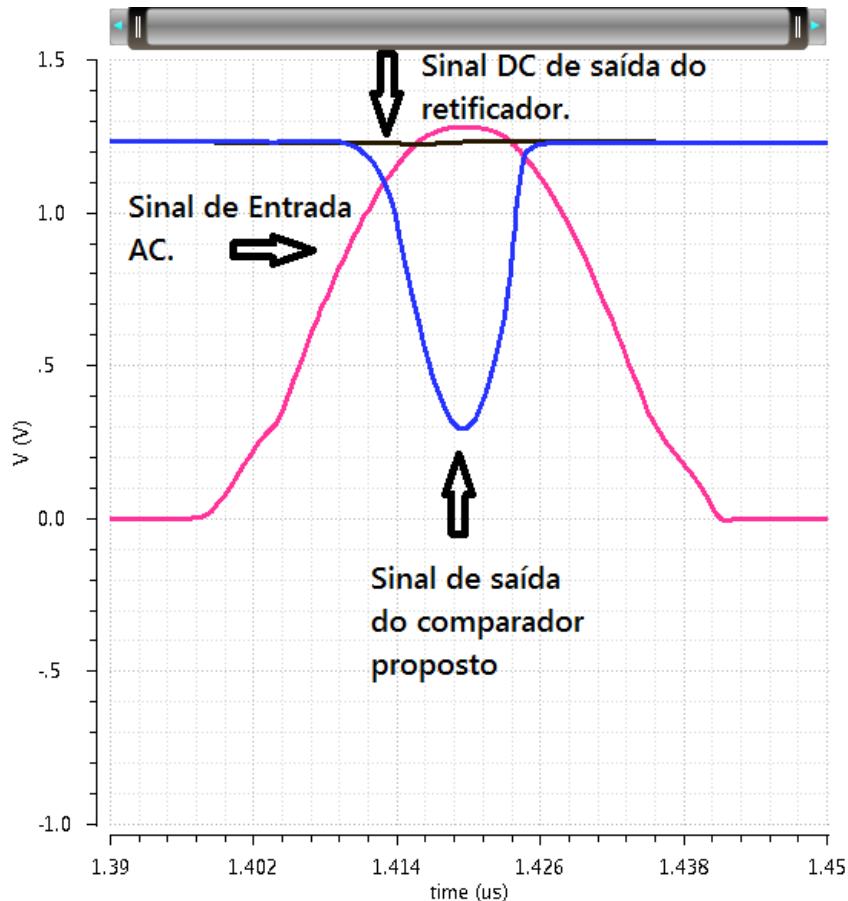

| Figura 39 – Sinal de saída do comparador proposto. . . . .                                                                                                                | 67 |

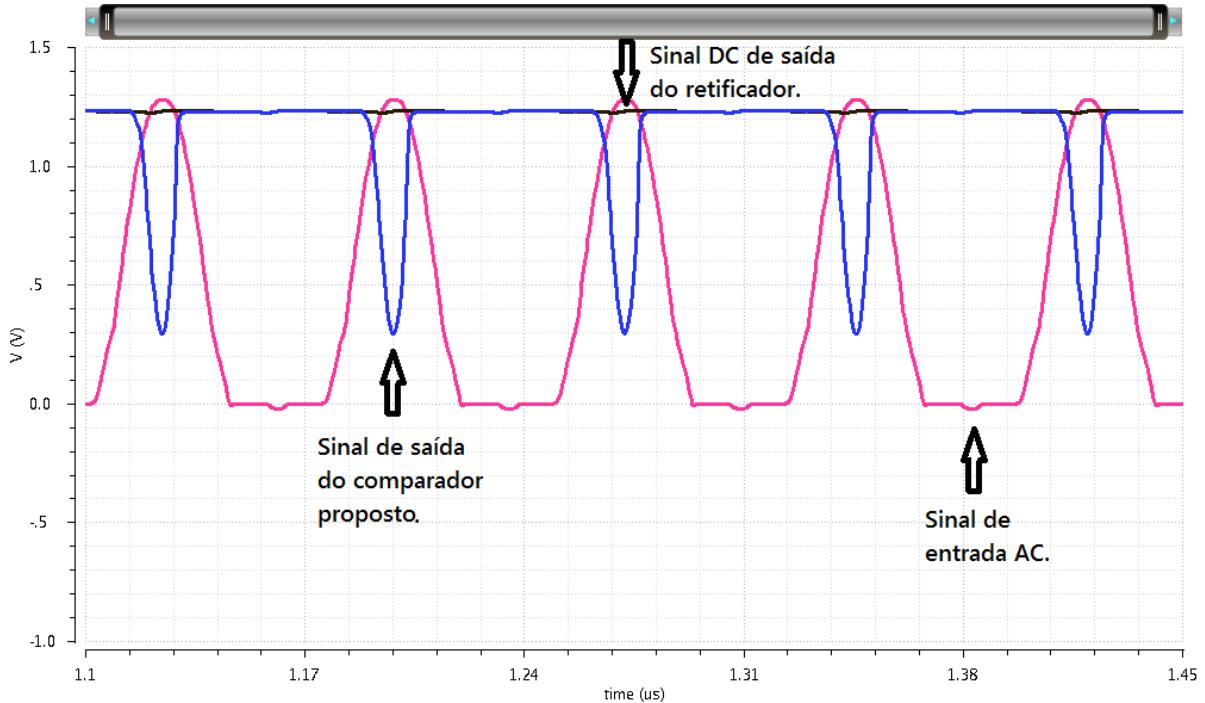

| Figura 40 – Sinal de saída do comparador proposto com janela de tempo maior. . .                                                                                          | 68 |

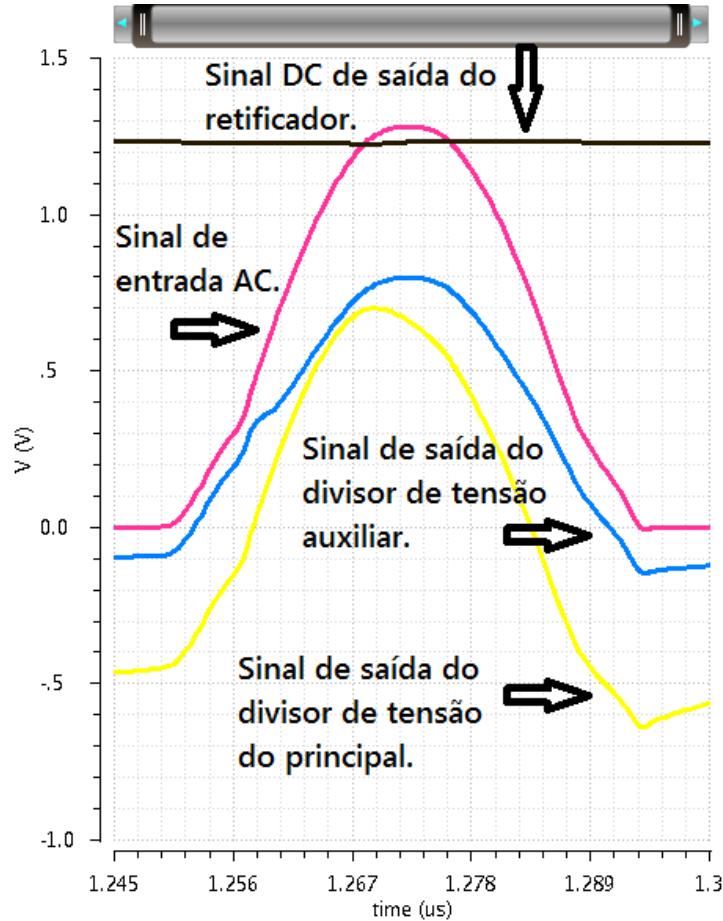

| Figura 41 – Sinais internos dos divisores de tensão principal e auxiliar. . . . .                                                                                         | 69 |

| Figura 42 – Formas de onda de operação do retificador projetado. . . . .                                                                                                  | 70 |

| Figura 43 – Curva de tensão de entrada por PCE. . . . .                                                                                                                   | 70 |

| Figura 44 – Curva de tensão nominal de entrada por tensão de saída do retificador. .                                                                                      | 71 |

| Figura 45 – Sinal de saída do comparador com comparador auxiliar. . . . .                                                                                                 | 72 |

| Figura 46 – Forma de onda da saída do retificador utilizando comparador com comparador auxiliar. . . . .                                                                  | 72 |

| Figura 47 – Chip fabricado pelo convênio MOSIS contendo o comparador com comparador auxiliar. . . . .                                                                     | 73 |

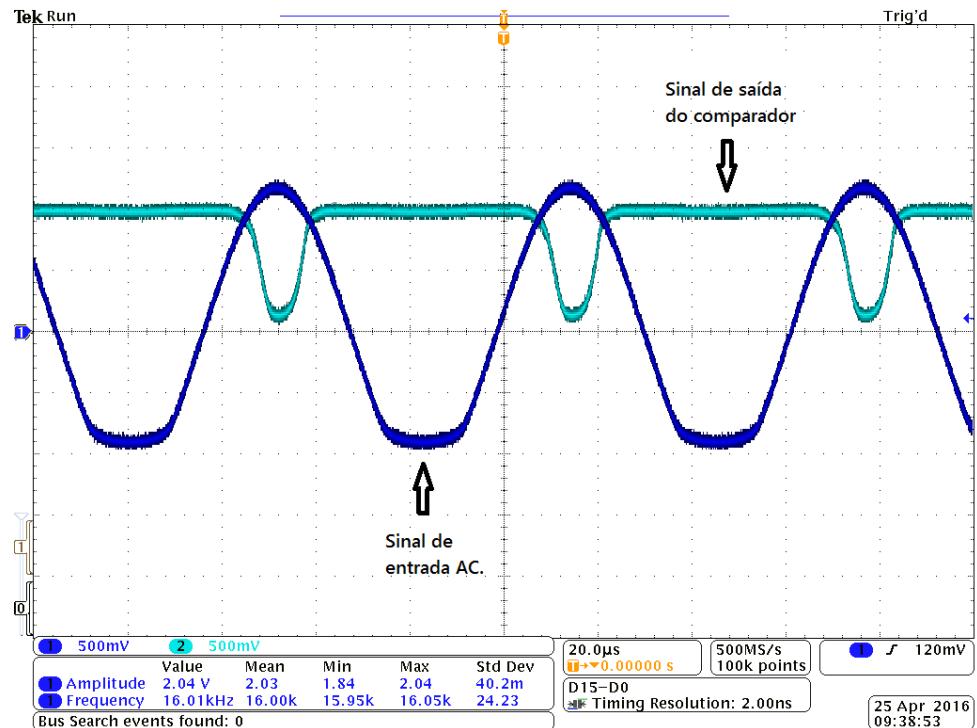

| Figura 48 – Teste de bancada do comparador com frequência de 16KHz. . . . .                                                                                               | 74 |

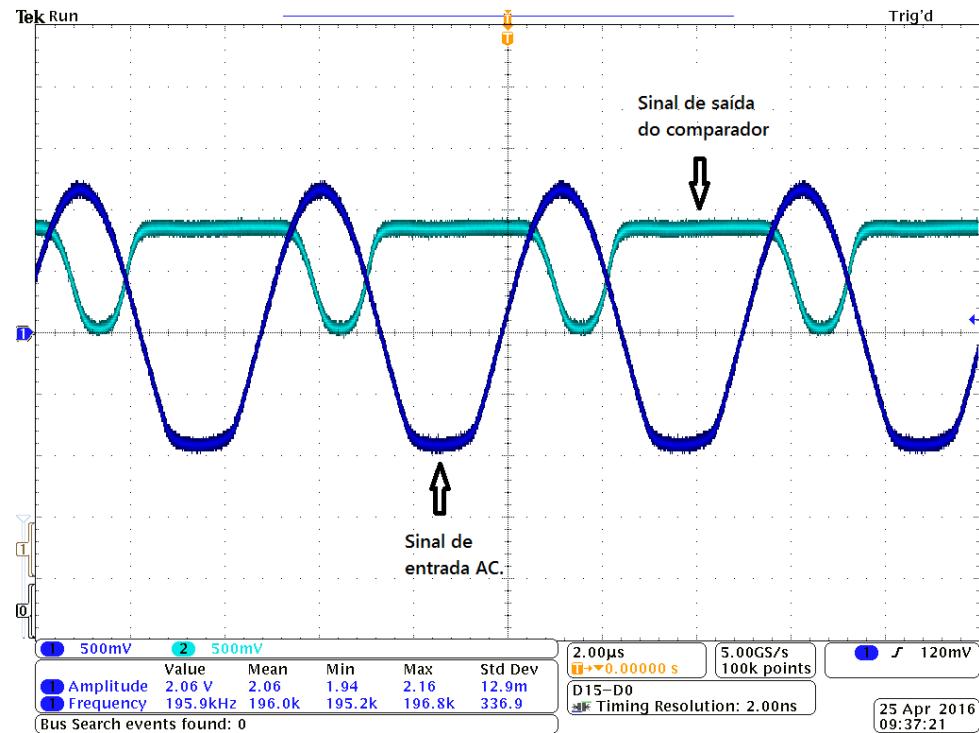

| Figura 49 – Teste de bancada do comparador com frequência de 195KHz. . . . .                                                                                              | 75 |

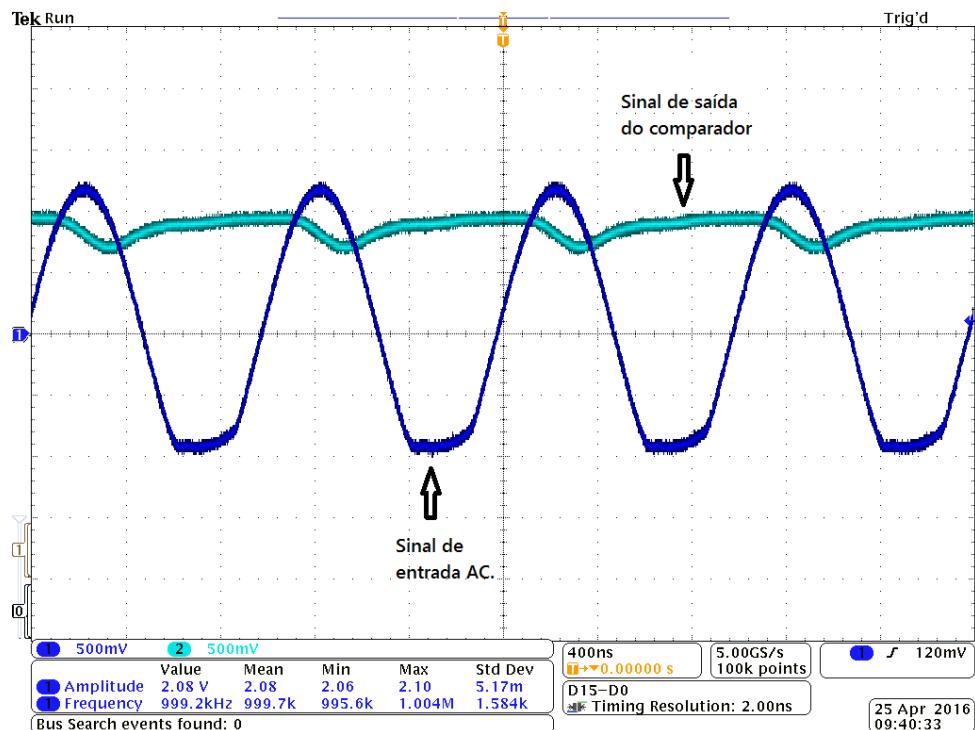

| Figura 50 – Teste de bancada do comparador com frequência de 1MHz. . . . .                                                                                                | 75 |

| Figura 51 – Teste de bancada do comparador com frequência de 13.56MHz. . . . .                                                                                            | 76 |

| Figura 52 – Simulação do chip real do comparador fabricado para frequência de 16KHz com capacitor de carga na saída do comparador. . . . .                                | 76 |

| Figura 53 – Simulação do chip real do comparador fabricado para frequência de 195KHz com capacitor de carga na saída do comparador. . . . .                               | 77 |

|                                                                                                                                                                                                                                                                                                                                                                                          |    |

|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----|

| Figura 54 – Simulação do chip real do comparador fabricado para frequência de 1MHz com capacitor de carga na saída do comparador. . . . .                                                                                                                                                                                                                                                | 77 |

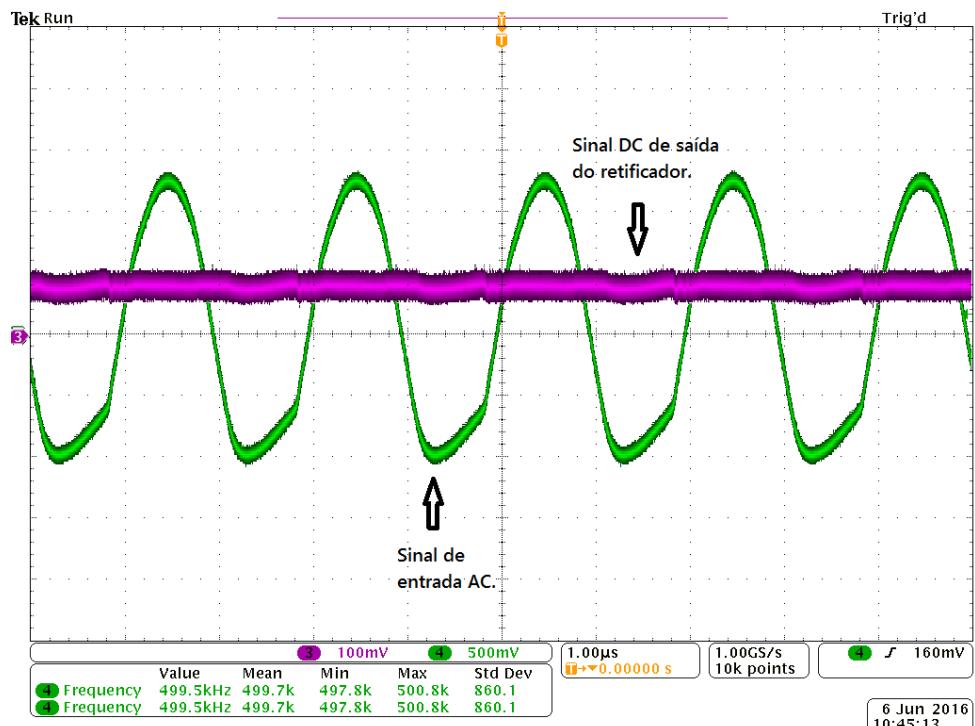

| Figura 55 – Forma de onda do retificador fabricado (499,5KHz). . . . .                                                                                                                                                                                                                                                                                                                   | 78 |

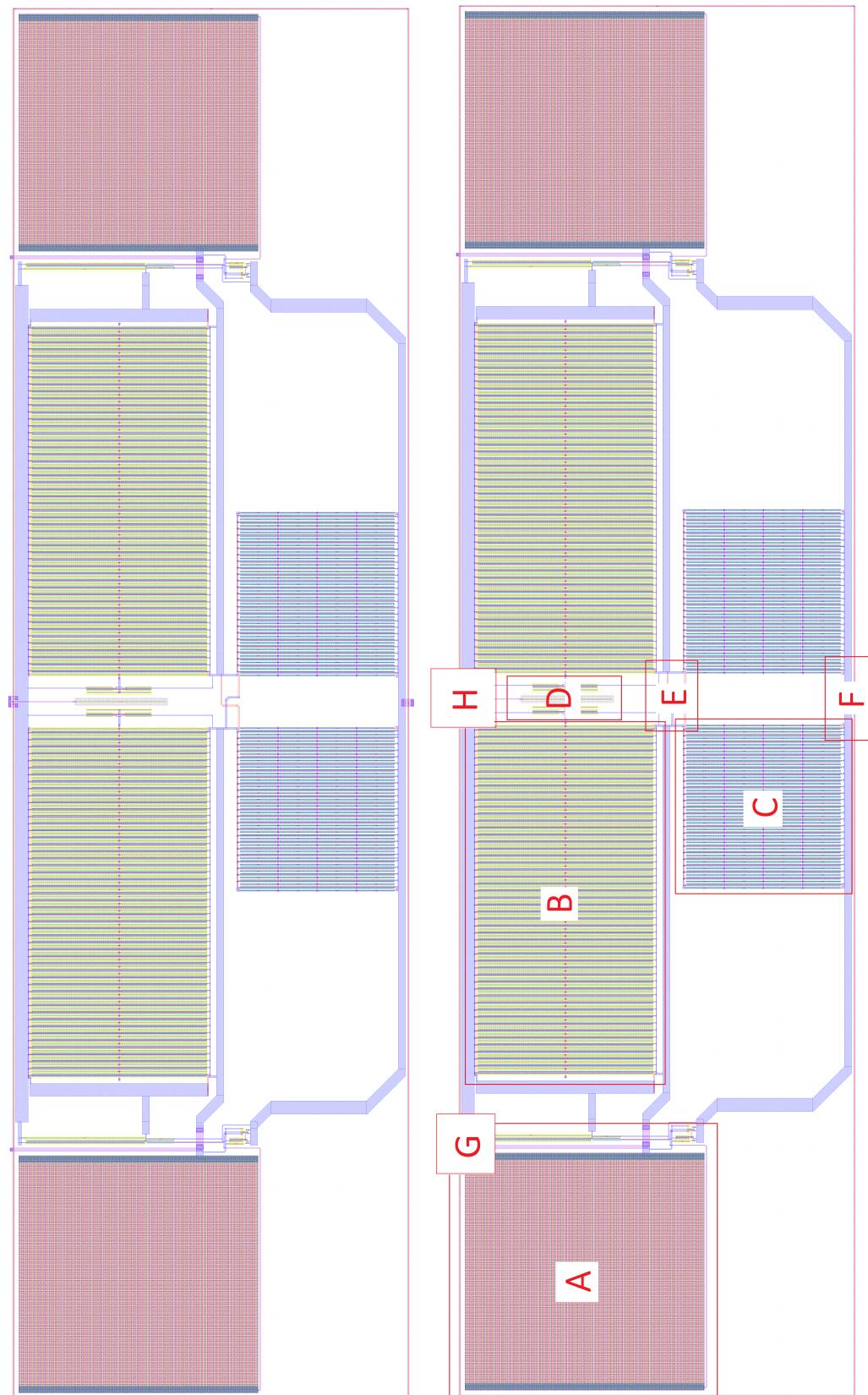

| Figura 56 – Circuito de Retificador utilizado no desenvolvimento do <i>Layout</i> . . . . .                                                                                                                                                                                                                                                                                              | 88 |

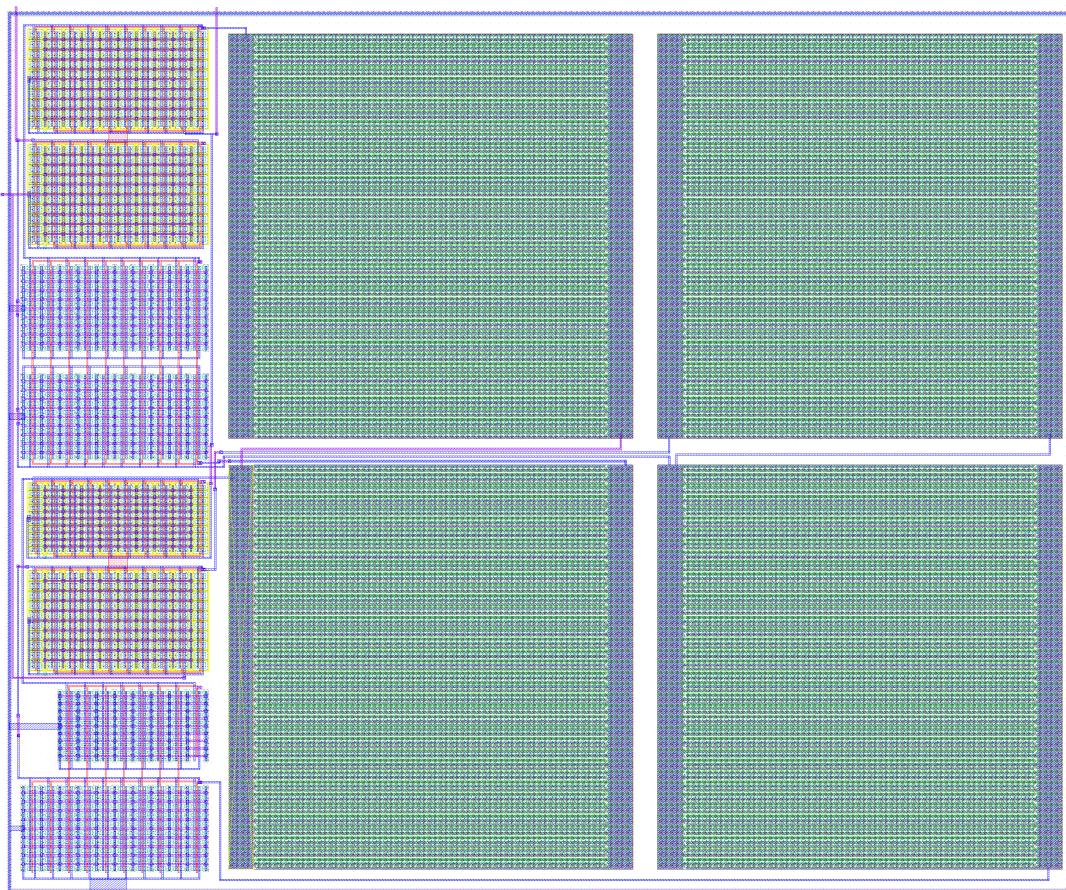

| Figura 57 – (Esquerda) <i>Layout</i> completo do retificador, (Direita) <i>Layout</i> do Retificador com destaque de referência: A - Comparador, B - Transistor PMOS, C - Transistor NMOS, D - Circuito de polarização de corpo dinâmica, E - Conexão dos transistores do retificador e F - Conector externo GND, G - Conector externo IN+ (Sinal AC), H - Conector externo VDC. . . . . | 89 |

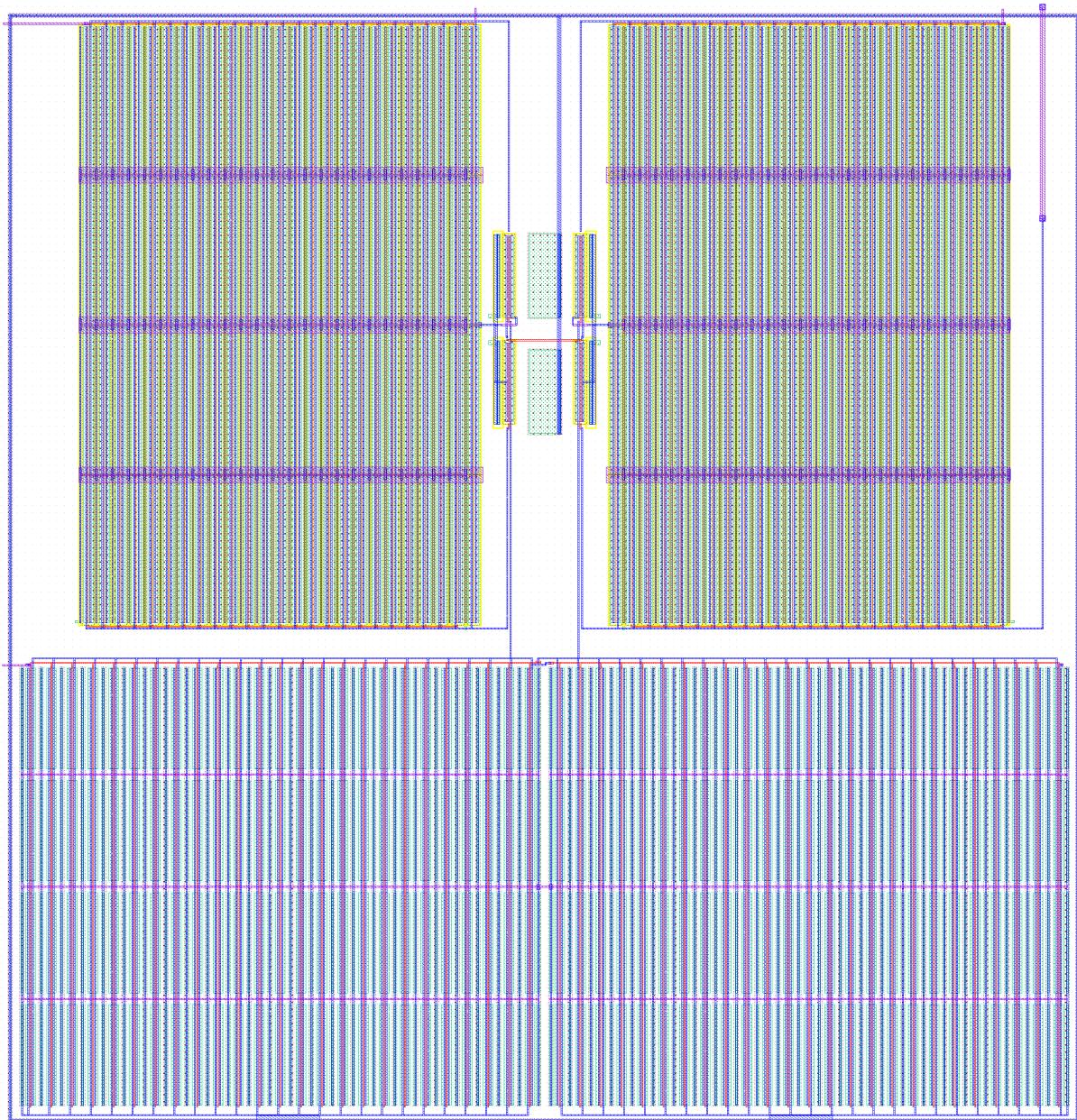

| Figura 58 – Retificador. . . . .                                                                                                                                                                                                                                                                                                                                                         | 91 |

| Figura 59 – Comparador acompanhado de comparador auxiliar. . . . .                                                                                                                                                                                                                                                                                                                       | 92 |

# Lista de tabelas

|                                                                                                   |    |

|---------------------------------------------------------------------------------------------------|----|

| Tabela 1 – Menor sinal de operação. . . . .                                                       | 25 |

| Tabela 2 – Profundidade da penetração de sinais de RF em tecidos e músculos. . . . .              | 27 |

| Tabela 3 – Quantidade de radiação eletromagnética segura a exposição humana. . . . .              | 29 |

| Tabela 4 – Diferença entre funcionamento dos transistores PMOS e NMOS. . . . .                    | 34 |

| Tabela 5 – Atraso percentual de operação do comparador de acordo com a frequênci-<br>cia. . . . . | 78 |

| Tabela 6 – Comparação com outros trabalhos. . . . .                                               | 79 |

# Lista de abreviaturas e siglas

|        |                                                                                                                  |

|--------|------------------------------------------------------------------------------------------------------------------|

| PCE    | Eficiência na Conversão de Potência ( <i>Power Conversion Efficiency</i> )                                       |

| FCC    | Comissão de Comunicação dos Estados Unidos ( <i>Federal Communications Commission</i> )                          |

| ANATEL | Agência Nacional de Telecomunicações                                                                             |

| ETSI   | Instituto de Telecomunicações da Europa ( <i>European Telecommunications Standards Institute</i> )               |

| EIRP   | Equivalente Isotrópico de Potência de Radiação ( <i>Equivalent isotropically radiated power</i> )                |

| CMOS   | Semicondutor de Metal-Óxido Complementar ( <i>Complementary Metal Oxide Semiconductor</i> )                      |

| RF     | Rádio Frequência ( <i>Radio-Frequency</i> )                                                                      |

| EVC    | Cancelamento Externo de V <sub>th</sub> ( <i>External-V<sub>th</sub>-cancellation</i> )                          |

| SVC    | Auto Cancelamento de V <sub>th</sub> ( <i>Self-V<sub>th</sub>-cancellation</i> )                                 |

| RFID   | Identificação por Rádio Frequência ( <i>Radio-Frequency IDentification</i> )                                     |

| UHF    | Ultra Alta Frequência ( <i>Ultra High Frequency</i> )                                                            |

| ISM    | Banda Industrial, Científica e Médica ( <i>Industrial, Scientific and Medical Radio Bands</i> )                  |

| MICS   | Serviço de Rádio de Comunicação de Dispositivos Médicos ( <i>Medical Device Radiocommunications Service</i> )    |

| SAR    | Taxa de Absorção Específica ( <i>Specific Absorption Rate</i> )                                                  |

| RMS    | Valor Eficaz ( <i>Root Mean Square</i> )                                                                         |

| IEEE   | Instituto de Engenheiros Eletricistas e Eletrônicos ( <i>Institute of Electrical and Electronics Engineers</i> ) |

| FET    | Transistor de Efeito de Campo ( <i>Field Effect Transistor</i> )                                                 |

| TEG    | Gerador Termoelétrico ( <i>Thermoelectric Generator</i> )                                                        |

| TEM    | Módulo Termoelétrico ( <i>Thermoelectric Module</i> )                                                            |

# Lista de símbolos

|          |                                          |

|----------|------------------------------------------|

| $L$      | Comprimento de Canal                     |

| $W$      | Largura de Canal                         |

| $V_{DS}$ | Tensão entre Dreno e Fonte               |

| $V_{GS}$ | Tensão entre <i>Gate</i> e Fonte         |

| $V_{Th}$ | Tensão de Limiar                         |

| $\eta$   | Eficiência Parcial                       |

| $\tau$   | Constante de Tempo de Carga do Capacitor |

# Sumário

|            |                                                                |           |

|------------|----------------------------------------------------------------|-----------|

| <b>1</b>   | <b>INTRODUÇÃO</b>                                              | <b>16</b> |

| <b>1.1</b> | <b>Justificativas</b>                                          | <b>16</b> |

| <b>1.2</b> | <b>Objetivos</b>                                               | <b>17</b> |

| <b>1.3</b> | <b>Organização do trabalho</b>                                 | <b>17</b> |

| <b>2</b>   | <b>REVISÃO TEÓRICA</b>                                         | <b>19</b> |

| <b>2.1</b> | <b>Métodos de Transferência de Energia</b>                     | <b>19</b> |

| 2.1.1      | Ondas de Ultrassom                                             | 20        |

| 2.1.2      | Método Térmico                                                 | 20        |

| 2.1.3      | Eletromagnetismo                                               | 21        |

| 2.1.3.1    | Acoplamento Indutivo                                           | 22        |

| 2.1.3.2    | Acoplamento Capacitivo                                         | 23        |

| 2.1.3.3    | Radiofrequência - Campo Distante                               | 24        |

| <b>2.2</b> | <b>Frequências de Operação</b>                                 | <b>26</b> |

| 2.2.1      | EIRP da banda MICS                                             | 27        |

| <b>2.3</b> | <b>Níveis de Radiação Eletromagnética Considerados Seguros</b> | <b>28</b> |

| 2.3.1      | Threshold e Mínimo Sinal Necessário                            | 29        |

| 2.3.2      | Potência Requerida por Circuitos Implantados                   | 29        |

| 2.3.3      | Eficiência                                                     | 30        |

| <b>2.4</b> | <b>Especificação do Sistema</b>                                | <b>31</b> |

| <b>3</b>   | <b>RETIFICADORES</b>                                           | <b>32</b> |

| <b>3.1</b> | <b>Tipos de Diodo (PN, Schottky e MOS)</b>                     | <b>32</b> |

| <b>3.2</b> | <b>Funcionamento transistores MOS</b>                          | <b>33</b> |

| <b>3.3</b> | <b>Tipos de Retificadores</b>                                  | <b>35</b> |

| 3.3.1      | Retificadores Passivos                                         | 35        |

| 3.3.1.1    | <i>External-V<sub>th</sub>-cancellation</i> (EVC)              | 36        |

| 3.3.1.2    | <i>Self-V<sub>th</sub>-cancellation</i> (SVC)                  | 36        |

| 3.3.1.3    | Retificador <i>Cross-Coupled</i>                               | 37        |

| 3.3.1.4    | <i>Dickson Charge Pump</i>                                     | 37        |

| 3.3.2      | Retificadores Ativos                                           | 39        |

| 3.3.2.1    | Retificador Ativo com Comparadores                             | 39        |

| 3.3.2.2    | Retificador 1X/2X Reconfigurável                               | 41        |

| <b>4</b>   | <b>COMPARADORES</b>                                            | <b>43</b> |

| <b>4.1</b> | <b>Comparador <i>Two-input Common-gate</i></b>                 | <b>43</b> |

|     |                                                                                                                     |           |

|-----|---------------------------------------------------------------------------------------------------------------------|-----------|

| 4.2 | Comparador Principal Acompanhado de Comparador Auxiliar. . . . .                                                    | 44        |

| 4.3 | Comparador Proposto . . . . .                                                                                       | 47        |

| 5   | PROJETO DO RETIFICADOR . . . . .                                                                                    | 52        |

| 5.1 | Análise Preliminar e Topologia Escolhida . . . . .                                                                  | 52        |

| 5.2 | Caracterização dos Transistores . . . . .                                                                           | 53        |

| 5.3 | Polarização de Corpo Dinâmica . . . . .                                                                             | 55        |

| 5.4 | Dimensionamento dos Transistores do Retificador . . . . .                                                           | 56        |

| 5.5 | Dimensionamento dos Transistores do Comparador Proposto . . . . .                                                   | 57        |

| 6   | SIMULAÇÕES E RESULTADOS . . . . .                                                                                   | 67        |

| 6.1 | Simulação do Comparador Proposto . . . . .                                                                          | 67        |

| 6.2 | Simulação do Retificador Projetado utilizando o comparador proposto. . . . .                                        | 69        |

| 6.3 | Simulação do Retificador utilizando Comparador Com Comparador Auxiliar . . . . .                                    | 71        |

| 6.4 | Testes Em Bancada do Comparador Com Comparador Auxiliar . . . . .                                                   | 73        |

| 6.5 | Discussão dos Resultados . . . . .                                                                                  | 79        |

| 7   | CONCLUSÃO . . . . .                                                                                                 | 81        |

| 7.1 | Conclusão . . . . .                                                                                                 | 81        |

| 7.2 | Trabalhos Futuros . . . . .                                                                                         | 81        |

|     | REFERÊNCIAS . . . . .                                                                                               | 82        |

|     | <b>APÊNDICES</b> . . . . .                                                                                          | <b>86</b> |

|     | APÊNDICE A – ARTIGO PUBLICADO EM CONGRESSO . . . . .                                                                | 87        |

|     | APÊNDICE B – <i>LAYOUT</i> RETIFICADOR PROPOSTO . . . . .                                                           | 88        |

|     | APÊNDICE C – <i>LAYOUT</i> RETIFICADOR UTILIZANDO COMPARADOR PRINCIPAL ACOMPANHADO DE COMPARADOR AUXILIAR . . . . . | 90        |

# 1 Introdução

Segundo Xin (1), o conceito de transferência de energia sem fio foi proposto primeiramente por Tesla (2). Durante o século XX algumas experiências que tentavam transferir grandes quantidades de energia utilizando lasers e micro-ondas foram realizadas mas foi com o advento da identificação por radiofrequência (RFID, *Radio-Frequency Identification*) que a transferência de energia sem fio se tornou popular.

Paralelamente a este desenvolvimento, dispositivos médicos implantáveis como marca passo, sensores de glicose, pressão e temperatura foram desenvolvidos. A utilização de baterias para alimentar estes dispositivos gera o incomodo de ter que realizar cirurgias para a substituição ou utilizar fios de alimentação transcutâneos que expõe o indivíduo tanto a infecções como a desconforto (3).

Devido aos problemas descritos anteriormente formas de transferir energia sem fios para implantes médicos são alternativas interessantes, por permitir uma vida útil mais longa para implantes, reduzir o risco de infecções e proporcionar uma melhor qualidade de vida.

## 1.1 Justificativas

A utilização de conversores de energia em radiofrequência para energia em corrente contínua permite que diversos dispositivos, entre eles implantes biomédicos, trabalhem sem a presença de uma bateria. Para o caso dos dispositivos médicos implantados o aumento da eficiência na conversão desta energia permite que estes dispositivos sejam menores, causando menos desconforto ao paciente e proporcionando facilidade na implantação, permitindo que aplicações mais sofisticadas, que consomem mais energia, sejam desenvolvidas e possibilitando em alguns casos que a fonte de energia externa esteja um pouco mais afastada do paciente.

O desenvolvimento de uma nova proposta de retificador, destinado ao uso em implantes médicos, permite a incorporação de novas tecnologias CMOS ainda não reportadas na literatura dentro deste contexto. Estas abordagens, aliadas a um novo projeto de circuito, criam um retificador com ótima eficiência PCE e maior simplicidade em relação a outros circuitos.

## 1.2 Objetivos

O objetivo deste trabalho é o desenvolvimento de uma alternativa de retificador para a conversão de sinais de radiofrequência em sinal de tensão contínua. Este retificador alimentará implantes médicos que não estejam implantados em profundidades maiores que 4mm em relação a superfície da pele, ou seja, o limite da ultima camada da pele, a derme (4).

Pensando nesse contexto é muito interessante que o retificador final tenha a máxima eficiência de conversão de energia PCE possível, trabalhe dentro de uma frequência adequada, cumpra os critérios de segurança e que esteja de acordo com as legislações do Brasil e outros países. Além disso, seja simples para facilitar a integração em projetos de implantes biomédicos, ocupando uma pequena área de silício.

## 1.3 Organização do trabalho

Esse trabalho se distribui ao longo de seis capítulos. O capítulo 2 faz uma revisão teórica a respeito de alguns métodos de transferência de energia que já foram utilizados para alimentar implantes biomédicos. Discute as diferentes bandas de frequência que estão disponíveis para trabalho no contexto desta dissertação e as dificuldades e benefícios dessas bandas. Mostra também sobre como considerar se determinado nível de sinal eletromagnético é ou não seguro à exposição humana. Por fim, discuti sobre eficiência e mínimo sinal necessário para o funcionamento deste tipo de aplicação.

O capítulo 3 foca nas principais técnicas de retificadores presentes na literatura. Inicia com uma análise de qual tipo de diodo é mais adequado para um retificador fabricado em tecnologia CMOS. Faz uma rápida consideração sobre o funcionamento dos transistores MOS e a diferença na utilização dos transistores PMOS e NMOS, discutindo os principais pontos dos retificadores passivos e dos retificadores ativos.

O capítulo 4 aborda os comparadores utilizados nos retificadores ativos. Faz uma explicação a respeito do funcionamento do comparador *Two-input Common-gate*, do Comparador Principal Acompanhado de Comparador Auxiliar e do Comparador Proposto neste trabalho.

No capítulo 5 é feita a análise preliminar sobre o escopo deste trabalho. É realizada a caracterização dos transistores FET da tecnologia IBM 130nm que foi utilizada na implementação dos circuitos, a descrição de projeto e o dimensionamento dos elementos do retificador e Comparador Proposto.

O capítulo 6 apresenta as simulações dos circuitos projetados e faz a análise dos resultados obtidos. Neste capítulo, além das simulações e análises a respeito do retificador e Comparador Proposto também são realizadas simulações do Comparador Principal

Acompanhado de Comparador Auxiliar que foi fabricado pelo convênio MOSIS e serviu de matéria de estudo sobre o comportamento de comparadores e retificadores ativos na fase anterior a da elaboração do Comparador Proposto.

Na conclusão são retomados os principais pontos e também são discutidos possíveis trabalhos futuros.

## 2 Revisão Teórica

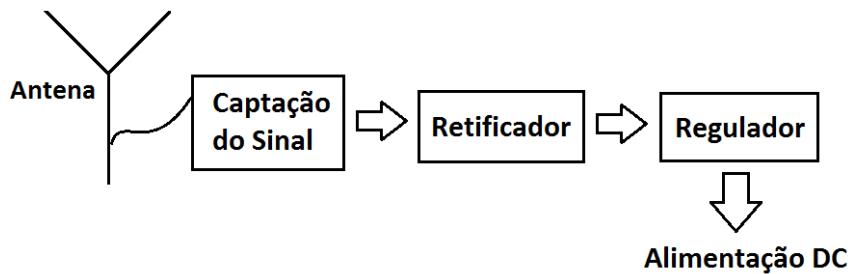

Sistemas de captação de energia por RF podem utilizar campos distantes ou próximos. Independente do tipo de campo utilizado, a maior parte dos blocos que compõem o sistema de captação de energia serão os mesmos.

Exemplificado pela figura 1, o bloco de captação de sinal depende do tipo de sinal, do tipo de antena e principalmente da frequência de trabalho. Contudo, os blocos de retificação e do regulador do sinal, mesmo podendo ser mais otimizados para uma função ou outra, em geral podem ser os mesmos.

Figura 1 – Esquemático do sistema de captação de energia RF e conversão para DC.

O foco deste trabalho é o retificador implementado para circuitos envolvendo captação de energia de RF. Contudo, inicialmente serão comentadas diferentes formas de captação de energia e posteriormente serão feitas considerações sobre frequências de operação, potência de irradiação, níveis de radiação considerados seguros, mínimo sinal de RF necessário, potência consumida por circuitos implantados e eficiência de conversão de energia.

### 2.1 Métodos de Transferência de Energia

Apesar dos métodos de transferência de energia permitirem que baterias recarregáveis sejam mantidas implantadas junto com dispositivos médicos, estas possuem um limitado ciclo de carga e descarga (3), podem vazar, e cedo ou tarde devem ser substituídas. Este problema de limitado número de ciclos de cargas/descargas e o considerável aumento de tamanho do implante que contém uma bateria faz com que opções de alimentação totalmente independente de baterias sejam muito mais interessantes por permitirem um tempo de vida quase indefinido para os dispositivos médicos implantados.

Serão discutidos agora possíveis métodos de transferência de energia sem a utilização de baterias, esses métodos são ondas de ultrassom, método térmico e eletromagnético.

netismo. O método eletromagnético se divide em três vertentes: Acoplamento indutivo, acoplamento capacitivo e radiofrequência de campo distante

### 2.1.1 Ondas de Ultrassom

Muito conhecido devido ao exame comumente realizado durante a gravidez o ultrassom é uma onda mecânica que tem sido utilizada para propósitos médicos desde 1960 (3). Com frequência que varia entre 2MHz e 18MHz o ultrassom sofre menor atenuação ao atravessar tecidos da pele do que ondas eletromagnéticas e pode ser utilizado como fonte de energia para implantes médicos (3). Para converter a energia mecânica das ondas sonoras em energia elétrica é utilizado um dispositivo piezoelétrico que converte energia mecânica em elétrica ou elétrica em mecânica (5). A transferência de potência utilizando ultrassom deve ser limitada a no máximo algumas centenas de  $\text{mW}/\text{cm}^2$  pois a exposição à ondas de ultrassom de frequências muito elevadas, e durante muito tempo, pode provocar danos ao tecido (3).

### 2.1.2 Método Térmico

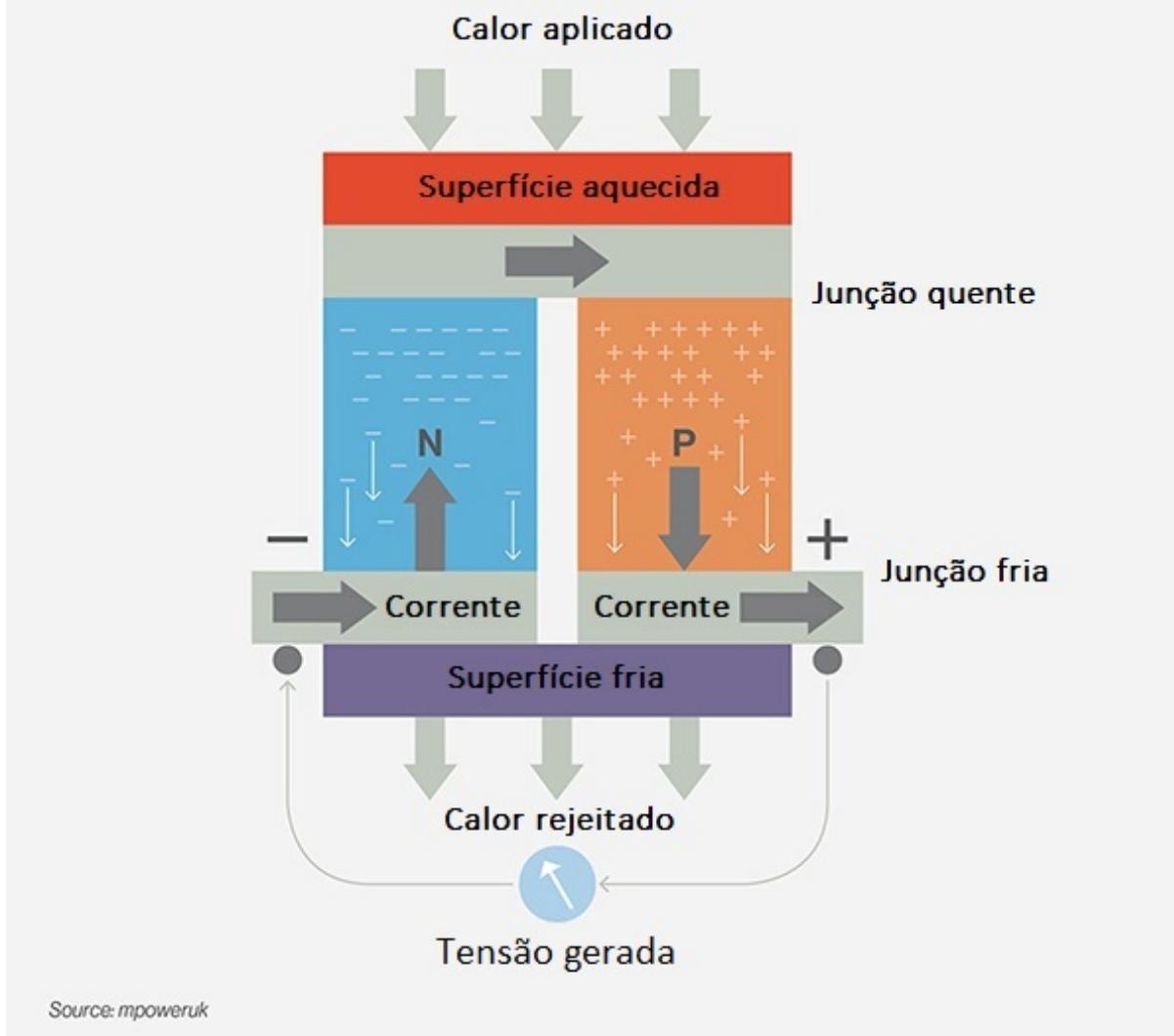

Em 1821 Thomas Johann Seebeck descobriu que um circuito feito por dois tipos de materiais diferentes, com junções em temperaturas diferentes fazia com que a agulha de uma bussola se mexesse (6). Esse efeito, que foi mais tarde nomeado como Efeito Seebeck em homenagem a Thomas Johann Seebeck, consiste na geração de uma pequena corrente elétrica entre dois terminais de um dispositivo que está exposto à diferentes temperaturas em suas faces.

Para gerar energia elétrica através de fonte térmica dentro do corpo humano, ou de outro animal, é utilizado o gradiente de temperatura existente entre o corpo e o ambiente externo. O dispositivo responsável por isso é o *Thermoelectric Module - TEM*, Módulo termoelétrico. O TEM é um conversor de energia em estado sólido que a princípio pode resfriar, aquecer ou gerar energia elétrica (7). Quando este dispositivo é utilizado para gerar energia ele é conhecido como *Thermoelectric Generator - TEG*, Gerador Termoelétrico (7).

Como exemplificado pela figura 2, um dispositivo TEG tradicional consiste de duas placas de cerâmicas com dois ou mais dispositivos semicondutores internos conectados eletricamente em série e termicamente em paralelo (8). A energia térmica que atravessa o dispositivo indo da fonte quente para a fonte fria gera uma pequena diferença de potencial entre as extremidades elétricas através do efeito Seebeck.

A principal desvantagem da utilização de TEGs como fonte de alimentação é que em geral a diferença de potencial gerada é muito pequena. Essa diferença depende do gradiente de temperatura e do tamanho do dispositivo mas para um caso típico são gerados

## Termopar Semicondutor - Efeito Seebeck

Figura 2 – Esquema de funcionamento de um dispositivo TEG. Imagem traduzida de (9).

entre 20mV e 250mV (10).

### 2.1.3 Eletromagnetismo

A transferência de energia por meio eletromagnético se divide em duas categorias. Métodos que exploram o campo próximo, onde efeitos indutivos são considerados, e método que explora o campo distante (11).

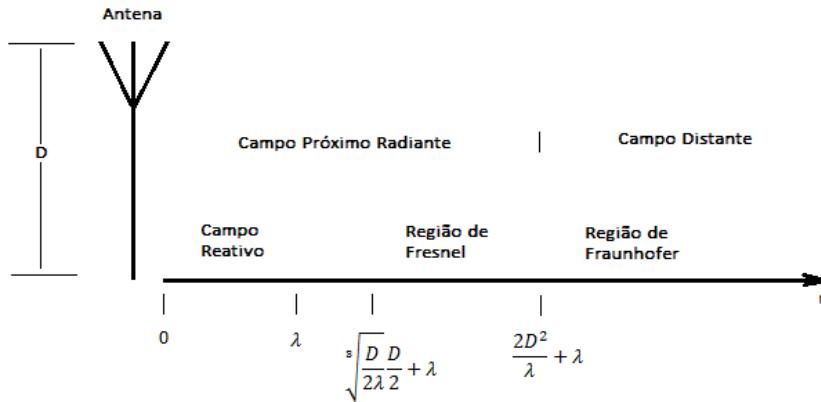

A figura 3 exemplifica a relação entre o tamanho “D” da antena e o comprimento de onda “ $\lambda$ ”. A região de Fraunhofer representa um campo distante da fonte, região de irradiação, onde efeitos indutivos são ignorados. Na região de Fresnel considera-se que o campo é próximo da fonte e todos efeitos eletromagnéticos devem ser considerados. Para a região de zero metro até o comprimento de onda o campo é considerado reativo (11).

Figura 3 – Regiões de Fresnel e Fraunhofer em uma antena radiante. (11).

#### 2.1.3.1 Acoplamento Indutivo

Quando duas bobinas usadas como antenas estão próximas o suficiente uma da outra dizemos que existe um acoplamento indutivo (3). Esta forma de transferência de energia para implantes médicos tem sido muito usada nos últimos 50 anos devido a possibilidade de ambas antenas estarem afastadas, pela pele, apenas alguns centímetros uma da outra.

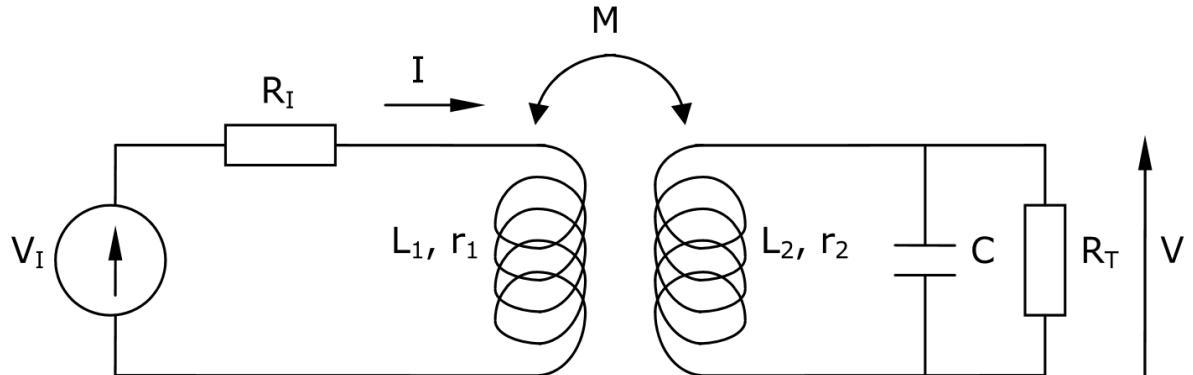

Segundo Aubert (12) o circuito equivalente baseado no acoplamento indutivo utilizado em sistemas de RFID pode ser observado na figura 4.

Figura 4 – Circuito equivalente de um sistema RFID utilizando acoplamento indutivo (12).

Neste circuito  $L_1$  e  $L_2$  representam as bobinas que trabalham como antenas,  $r_1$  e  $r_2$  representam as resistências em série. O capacitor  $C$  e a bobina  $L_2$  conectados em paralelo formam um resonador que seleciona a frequência de transmissão (12).

Deste modelo é obtida a equação 2.1 (12) que representa a magnitude  $V$  (Tensão

aplicada sobre a carga).

$$V = \frac{\omega k \sqrt{L_1 L_2}}{\sqrt{(\frac{L_2 \omega}{R_T} + r_2 C \omega)^2 + (1 - L_2 C \omega^2 + \frac{r_2}{R_T})^2}} I \quad (2.1)$$

$k$  é conhecido como *Coupling Coefficient*, seu valor é  $k = M/\sqrt{L_1 L_2}$ , onde  $M$  é a indutância mútua entre as duas bobinas  $L_1$  e  $L_2$  (Equação 2.2 (13)) e  $\omega = 2\pi f$ .

$$M = \frac{\mu_0 N_1 N_2 a^2 (\pi b^2)}{2(a^2 + r^2)^{\frac{3}{2}}} \quad (2.2)$$

Onde:

- \*  $N_1$  = Número de voltas na bobina 1,

- \*  $N_2$  = Número de voltas na bobina 2,

- \*  $a$  = raio da bobina 1,

- \*  $b$  = raio da bobina 2,

- \*  $r$  = distância entre as bobinas.

### 2.1.3.2 Acoplamento Capacitivo

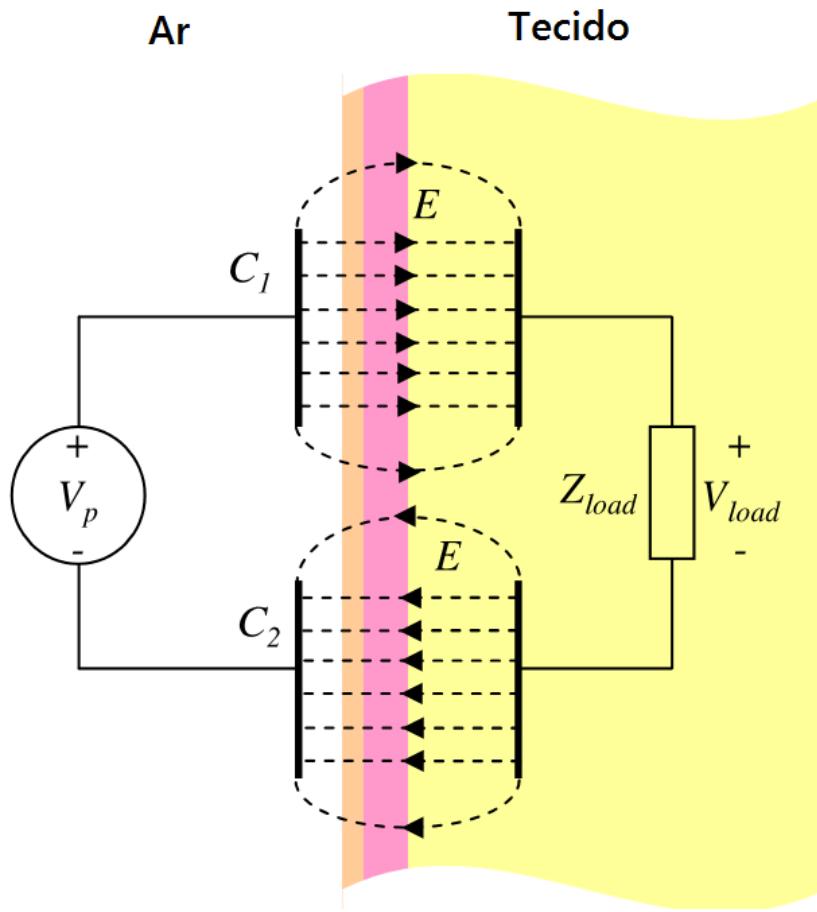

Assim como os *links* indutivos, o acoplamento capacitivo funciona para pequenas distâncias. O sistema é um capacitor que utiliza o tecido humano como meio dielétrico. Os problemas da utilização deste tipo de transmissão de energia é que o acoplamento capacitivo é mais eficiente para grandes áreas de antenas que formam o capacitor e para altas frequências. Contudo, por razões óbvias, é esperado que implantes médicos tenham o menor tamanho possível e quanto maiores as frequências utilizadas maior será a dissipação de energia pelos tecidos, o que pode causar queimaduras (3). A figura 5 exemplifica este tipo de acoplamento. Os capacitores  $C_1$  e  $C_2$  são formados entre as antenas dos dispositivos externo e do implante, enquanto o meio dielétrico é constituído pelo tecido da pele.

Figura 5 – Diagrama conceitual de um link de potência capacitivo implantado (3).

#### 2.1.3.3 Radiofrequência - Campo Distante

Radiofrequência (RF) de campo distante é um meio popular de transmissão de informação e potência através da mesma onda eletromagnética. Este sistema é utilizado principalmente pelas implementações RFID UHF que funcionam até distâncias de 10m. A diferença desta técnica para o acoplamento indutivo se dá pela substituição das antenas de bobinas por estruturas mais eficientes (3). Uma das vantagens sobre a técnica utilizando indutores é que a potência do sinal diminui à proporção de  $1/d^2$  enquanto no acoplamento indutivo a diminuição de potência é  $1/d^6$ , onde  $d$  representa a distância entre as antenas.(3).

A eficiência de um sinal de RF transmitido, e consequentemente a potência transmitida, está relacionada com a proporção entre o tamanho da antena e a frequência utilizada. Deste modo, para construir implantes pequenos é interessante a utilização de altas frequências (GHz). No entanto, altas frequências têm dificuldade para penetrar em tecidos da pele (3). Segundo Theilmann, (3) para transmitir 1uW a 1GHz para uma antena de tamanho 0,1mm a uma profundidade de aproximadamente 1cm no interior da pele é necessário aproximadamente 30kW. Se a antena medir 1mm a potência necessária

passa a ser de 3W.

Na literatura foram encontradas implementações diversas de transmissão de energia por RF. Entre as aplicações voltadas para implantes médicos os menores sinais recebidos são da ordem de -24dBm a -12dBm dependendo da técnica utilizada, antena on-chip ou off-chip, e da frequência escolhida. A tabela 1 mostra o menor sinal de operação de algumas implementações selecionadas.

Tabela 1 – Menor sinal de operação.

| Artigo | Menor sinal     | Frequência  | Técnica                                  |

|--------|-----------------|-------------|------------------------------------------|

| (14)   | -14dBm          | 950MHz      | Retificador com polarização gate-dreno.  |

| (15)   | -22,6dBm        | 902–928 MHz | Gate flutuante.                          |

| (16)   | -14,7dBm        | 900-MHz     | Transistores MOS conectados como diodos. |

| (17)   | -24 ou -18,8dBm | 915-MHz     | Auto compensação de tensão de limiar.    |

| (18)   | -14 ou -12dBm   | 868MHz      | Circuito ativo de carga.                 |

A potência recebida por sistemas RF na região de irradiação (de campo distante) segue a equação 2.3 (19).

$$Potencia\_Recebida[dBM] = Potencia\_Transmitida[dBm] + Ganhos[dB] - Perdas[dB] \quad (2.3)$$

Quando esse sistema opera em meio livre, e não existe nenhum corpo entre as antenas que influencia sobre a propagação, podemos dizer que toda perda se dá pelo quadrado da distância entre as antenas transmissora e receptora (20). Essa consideração se traduz na equação 2.4 que é conhecida como equação das telecomunicações ou fórmula de transmissão de Friis (20).

$$P_R = \frac{G_T G_R P_T \lambda^2}{(4\pi r)^2} \quad (2.4)$$

Na equação 2.4  $P_T$  e  $P_R$  são as potências transmitida e recebida,  $G_T$  e  $G_R$  são, respectivamente, os ganhos das antenas de transmissão e recepção,  $\lambda$  é o comprimento de onda e  $r$  é a distância entre as antenas.

É importante destacar que a equação 2.4 só é válida para a região de irradiação, região de Fraunhofer. Segundo Ribeiro (20) essa fórmula é válida para quando  $r >> \frac{\lambda}{4\pi} \sqrt{G_R G_T}$ . Isso acontece porque para esta região a interferência indutiva entre as antenas é próxima de zero.

## 2.2 Frequências de Operação

O espaço do espectro eletromagnético é um meio comum e limitado. Para evitar que diversas pessoas, com objetivos diferentes, tentem utilizar uma mesma frequência do espectro eletromagnético, existem agências reguladoras espalhadas pelo mundo que decidem como, e por quem, o espectro pode ser utilizado. Exemplos destas agências são a Agência Nacional de Telecomunicações - Anatel do Brasil, a *Federal Communications Commission* - FCC dos Estados Unidos e a *European Telecommunications Standards Institute* - ETSI da Europa. Na maior parte dos casos o espectro eletromagnético é fatiado e cada fatia destinada a apenas um tipo de aplicação. Por exemplo, o espaço de espectro destinado a transmissão de rádios FM no Brasil vai de 87,8 a 108 MHz de acordo com a resolução nº 67 de 12 de novembro de 1998 da Anatel (21).

Muitas das decisões tomadas pelas agências consideram não apenas o interesse do país ao qual elas pertencem mas levam em consideração os padrões já existentes ao redor do mundo. Esses padrões são desejáveis para que seja possível utilizar um mesmo equipamento em diferentes países sem que legislações sejam descumpridas.

Dentro do escopo deste trabalho uma das bandas regulamentadas de possível utilização é a banda de frequências para aplicações industriais, científicas e médicas (*bands of industrial, scientific, and medical frequencies* - ISM). Segundo Mahammad (22), as frequências ISM de 125 kHz até 135 kHz, 6,78 MHz, 13,56 MHz, 27,125 MHz e 40.68 MHz, como também 433,92 MHz, 869 MHz e 2,4 GHz são segmentos de frequências de possível utilização, com foco especial para frequências entre 3 kHz e 30 MHz que são largamente utilizadas para comunicações transcutâneas devido a facilidade de penetração e baixo aquecimento de tecidos. Segundo Theilmann (3) as frequências ISM mais utilizadas para comunicação/alimentação RF de campo distante em implantes médicos são as frequências de 13,56MHz, 434MHz, 915MHz e 2,45GHz. No trabalho de Johansson (23) a frequência ISM de 2,45GHz também é citada como uma frequência de possível utilização, contudo é feita a ressalva que instrumentos que operam nesta frequência podem sofrer interferências de outros dispositivos como redes de computadores e fornos de micro-ondas.

Em 1999 o órgão de regulamentação de telecomunicações dos Estados Unidos, o FCC, disponibilizou as frequências de 402 até 405 MHz para serem utilizadas na comunicação de dispositivos médicos implantados (24), *Medical Implant Communications Service* - MICS. Sendo esta a primeira banda específica para comunicação de dispositivos médicos implantáveis, foram estabelecidas regras para utilização. O documento que estabelece os padrões para utilização da banda MICS é o *Federal Communications Commission* FCC 99-363 (24). Entre estas regras estão a *effective isotropic radiated power* - EIRP máxima de 25 microwatts e largura de banda limite de 300kHz que possibilita a transmissão de aproximadamente 10kb/s para um link entre 2 e 10m de distância (25). Estas especificações, entre outros objetivos, buscam possibilitar a coexistência da banda

MICS juntamente com a atividade utilizadora original da faixa de frequência entre 402 até 405 MHz, comunicação entre a terra e o espaço de satélites meteorológicos (24).

Tanto a Anatel como a ETSI regulamentaram a banda MICS seguindo os padrões dos Estados Unidos. Na Europa a regulamentação é encontrada no documento ETSI EN 301 839-1 (26) e no Brasil, a resolução nº 506, de 1º de julho de 2008 (27) apresenta no capítulo III, Seção III, Art. 19 o seguinte texto:

*Art. 19. Sistemas de Comunicações de Implantes Médicos (MICS) podem operar na faixa 402 - 405 MHz, desde que a potência (e.i.r.p) esteja limitada a 25 microwatts em uma largura de faixa de referência de 300 kHz.*

Uma importante preocupação sobre a frequência a ser utilizada em implantes médicos é a respeito de quão profundo determinada frequência consegue penetrar na pele. No texto de Johansson (23), este estabelece que a profundidade que determinada frequência penetra na pele é definida pela medida onde o campo elétrico é atenuado por um fator de  $e^{-1}$  ou 0,368. Essa profundidade calculada para frequências de 170kHz, 403,5MHz e 2,45GHz é apresentada na tabela 2.

Tabela 2 – Profundidade da penetração de sinais de RF em tecidos e músculos (23).

| Frequência   | 170kHz | 403,5MHz | 2,45GHz |

|--------------|--------|----------|---------|

| Profundidade | 2,2m   | 0,052m   | 0,022m  |

### 2.2.1 EIRP da banda MICS

Como já mencionado a *effective isotropic radiated power* máxima na banda MICS é limitadas em 25 microwatts. Isso significa que a potência de transmissão final, sendo esta definida como a potência do transmissor acrescida do ganho da antena de transmissão, não deve exceder 25 microwatts, equivalentes a -16dBm.

Como exemplo que ajuda a dimensionar esse sinal podemos aplicar à equação 2.5 uma EIRP de 25 microwatts e um sinal de 403Mhz ( $\lambda = 0,74441$ ), distante 1 metro de uma antena de recepção em espaço livre.

$$P_R = \frac{(EIRP)G_R\lambda^2}{(4\pi r)^2} \quad (2.5)$$

$$P_R = \frac{(25 * 10^{-6})G_R(0,74441)^2}{(4\pi)^2} \quad (2.6)$$

$$P_R = 87,736 * 10^{-9}G_R \quad (2.7)$$

Considerando-se que a antena receptora seja isotrópica, ganho unitário, a potência recebida por irradiação a um metro do transmissor é de aproximadamente 88 nW. Esse sinal convertido para dBm corresponde a -40dBm sem que as perdas por dissipação de potência por tecidos orgânicos sejam adicionados a conta.

Essa dimensão de sinal, comparada com a tabela 1, exibe como é difícil produzir um sistema de transferência de energia por RF utilizando-se apenas irradiação pela banda MICS. De fato, as pesquisas encontradas que utilizam transferência de energia para alimentar circuitos que se comunicam pela banda MICS, como por exemplo (28), implementam técnicas paralelas para auxiliar a alimentação do circuito. Em geral essas pesquisas tem um sistema que explora outras formas de captação de energia, *TEG* térmica ou captação de energia RF na frequência da 2,4Ghz, para alimentar o circuito que apenas se comunica pela banda MICS.

## 2.3 Níveis de Radiação Eletromagnética Considerados Seguros

Antes que um circuito com finalidades médicas seja implantado é imprescindível que este seja seguro. Para implantes que utilizam radiofrequência, a principal preocupação é em relação a potência dissipada. O aquecimento de tecidos pode ser causado por dissipação de potência vinda diretamente do implante, aquecimento do corpo do implante, ou pela incidência de potência eletromagnética dissipada em tecidos e músculos.

Para mensurar a quantidade de radiação eletromagnética absorvida é utilizada a *Specific Absorption Rate* (SAR) que segundo Crepaldi (29) é a *medida do campo elétrico e da densidade de corrente no ponto do tecido sobre investigação*. Matematicamente a SAR é expressa pela equação 2.8 exibida nos trabalhos de Crepaldi (29) e Pradier (30).

$$SAR = \frac{\sigma|E|^2}{\rho} \left[ \frac{W}{Kg} \right] \quad (2.8)$$

Na equação 2.8  $\sigma$  é a condutividade do tecido expressa em [S/m],  $\rho$  é a densidade de massa do tecido medida em  $[Kg/m^2]$  e  $E$  é o valor RMS do campo elétrico medido em  $[V/m]$  (29).

Segundo Crepaldi, a partir da SAR é possível obter o aquecimento local de determinado tecido pela ação eletromagnética ao fazer a derivada da temperatura em relação ao tempo (na equação 2.9,  $c$  é o calor latente e é medido em J/Kg) (29). Como ordem de grandeza, 1W/Kg de SAR é uma taxa de transferência de calor de 0,0003°C/s e seria necessário 1 hora para ampliar a temperatura de um tecido em 1°C (29).

$$\frac{dT}{dt} = \frac{SAR}{c} \left[ \frac{^{\circ}C}{s} \right] \quad (2.9)$$

A quantidade de radiação eletromagnética segura é objeto de estudo em todo o mundo. Em 2005 o *Institute of Electrical and Electronics Engineers - IEEE* publicou o documento IEEE std C95.1-2005 *Standard for Safety Levels with Respect to Human Exposure* (31) como referência para a intensidade de radiação segura para exposições ao corpo. Para frequências entre 100kHz e 3GHz este documento exibe em sua seção 4.2.1 uma tabela estabelecendo os limites SAR (Tabela 3).

Tabela 3 – Quantidade de radiação eletromagnética segura a exposição humana (31).

|                                      | <b>Público Geral</b> | <b>Ambiente Controlado</b> |

|--------------------------------------|----------------------|----------------------------|

| <b>Corpo inteiro</b>                 | 0,08 W/kg            | 0,4 W/kg                   |

| <b>Picos de radiação localizados</b> | 2 W/kg               | 10 W/kg                    |

| <b>Braços e Pernas</b>               | 4 W/kg               | 20 W/kg                    |

Considerando-se que implantes médicos estão relacionados a procedimentos médicos controlados por um médico em ambiente restrito (32) e que a comunicação com estes implantes aconteça em espaços de tempo bastante espaçados, em geral uma taxa SAR de 10 W/Kg é a referência, uma vez que na maioria dos casos será adotado um ambiente controlado.

### 2.3.1 Threshold e Mínimo Sinal Necessário

Na tecnologia CMOS a tensão mínima para ligar o transistor, tensão de limiar (*threshold*), varia entre 0,2 e 0,6V (19). Segundo Ribeiro (20) e Khalifa (19) a equação que relaciona a tensão RMS necessária para ligar o transistor com a potência de entrada é exibida na equação 2.10, onde  $P$  é a potência de entrada,  $V_{rms}^2$  é a tensão RMS e  $R$  é impedância de entrada.

$$P = \frac{V_{rms}^2}{R} \quad (2.10)$$

Considerando uma impedância de entrada de 50 ohms aplicada a equação 2.10 encontramos que a potência necessária para ligar um transistor varia entre 0.4 mW e 3,6 mW (19). Para situações onde a tensão de entrada é menor que a tensão de limiar existem técnicas de diminuição da tensão de limiar do transistor como por exemplo a técnica de *gate flutuante* (19).

### 2.3.2 Potência Requerida por Circuitos Implantados

A quantidade de potência requerida por um implante depende diretamente da aplicação deste dispositivo. Circuitos que realizam envio e recepção de grandes quantidades de informação sem fio tendem a consumir maior quantidade de energia (3). Segundo (3) existem aplicações de circuitos implantados que consomem potência na ordem de  $100\mu\text{W}$

e em média os circuitos típicos costumam dissipar 1mW ou mais, o que geralmente exige transistores com dimensões de centímetros. Isso obriga que futuros projetos que sejam tecnicamente mais complexos consumam menos potência.

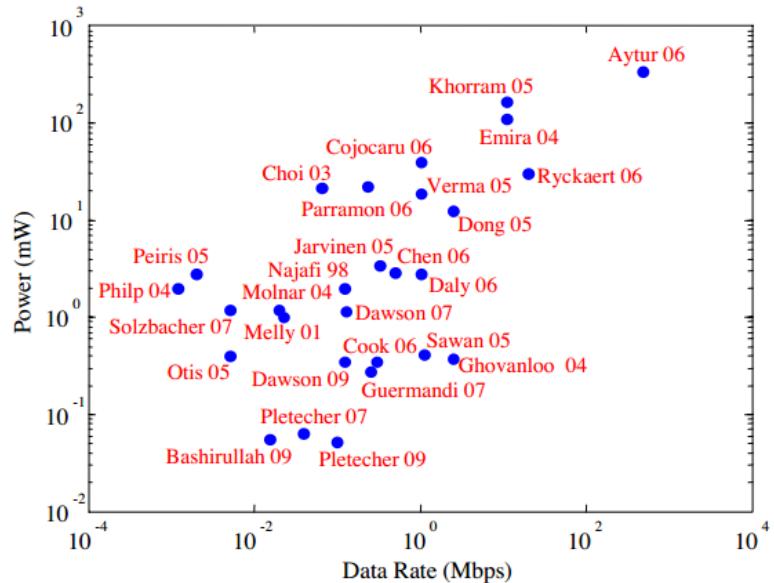

Figura 6 – Consumo de potência de implantes vs velocidade de transmissão de dados relatados em trabalhos prévios (3).

A figura 6 retirada de (3) correlaciona consumo de potência pela velocidade de transmissão de dados de implantes relatados em outros trabalhos. Nela é possível observar que a grande maioria dos trabalhos tem consumo ao redor de 1mW, com apenas três trabalhos consumindo perto de 100 $\mu$ W e poucos trabalhos consumindo próximo a 100mW.

### 2.3.3 Eficiência

Eficiência na conversão de potência (*PCE Power Conversion Efficiency*) é a taxa que relaciona a energia dissipada pela carga com a energia consumida pelo circuito inteiro, equação 2.11. A PCE também pode ser definida como a taxa que relaciona a potência DC de saída com a potência RF de entrada (19), sendo composta pelas eficiências parciais  $\eta$  de todo o projeto onde  $\eta_{pa}$ ,  $\eta_{link}$ ,  $\eta_{rectifier}$ ,  $\eta_{regulator}$  representam respectivamente a eficiência do amplificador de potência, do link indutivo, do retificador e do regulador de tensão (equação 2.12).

$$PCE = \frac{P_{out}}{P_{in}} * 100 \quad (2.11)$$

$$PCE = \eta_{pa} * \eta_{link} * \eta_{rectifier} * \eta_{regulator} \quad (2.12)$$

O fator  $\eta_{rectifier}$  representa a quantidade de potência que sai do retificador dividida pela quantidade de potência que entra no retificador, equação 2.13. Para uma PCE de 30% é esperada uma eficiência  $\eta_{rectifier}$  do retificador da ordem de 80% (33).

$$\eta_{rectifier} = \frac{P_{out\_DC}}{P_{out\_AC}} \quad (2.13)$$

## 2.4 Especificação do Sistema

Deste modo, como foi mostrado até aqui, o sistema que se deseja projetar deverá ter as seguintes características:

- \* Funcionar por acoplamento indutivo,

- \* Utilizar Frequência de 13,56MHz,

- \* Prover potência de saída maior que 1mW,

- \* Respeitar SAR máxima de 10W/Kg,

- \* Ter eficiência PCE igual ou maior a 80%.

No próximo capítulo serão comentadas as características dos diferentes tipos de retificadores existentes, como também as dificuldades encontradas já reportadas no uso da tecnologia CMOS para a criação destes tipos de estruturas.

### 3 Retificadores

Conforme mencionado no início do capítulo 2, um dos elementos necessários na captação de energia adquirida de sinais de RF é o retificador.

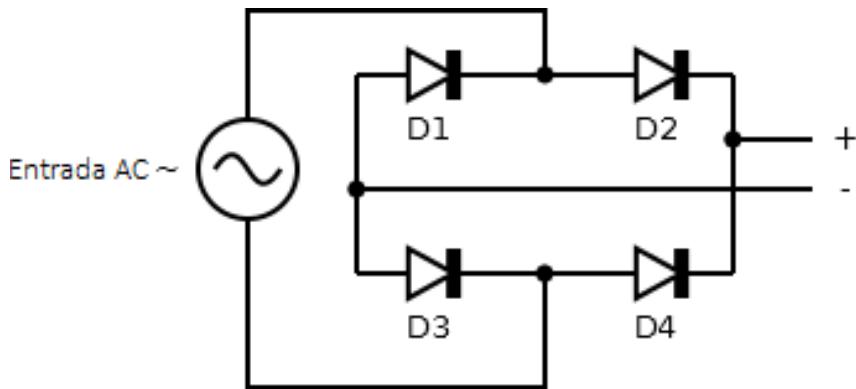

Tradicionalmente retificadores são construídos utilizando pontes de diodos que realizam a retificação do sinal AC.

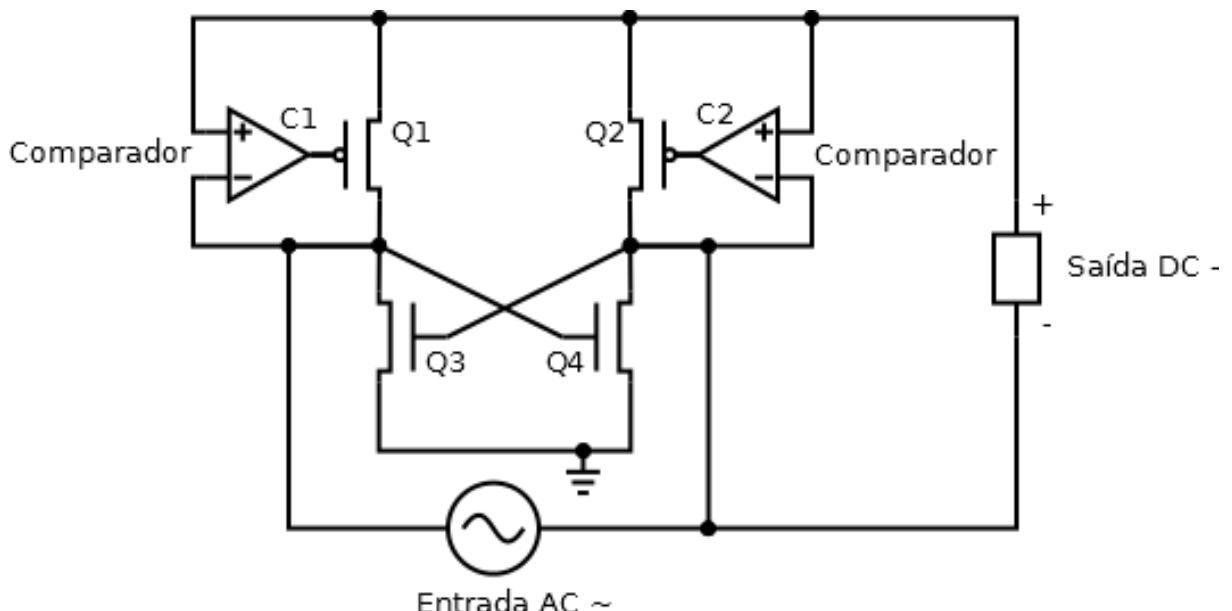

A figura 7 representa um circuito de retificação tradicional de onda completa utilizando 4 transistores de junção PN. O funcionamento deste retificador é simples. Quando a fonte fornece tensão positiva aos diodos D1 e D2 os diodos D3 e D4 ficam aterrados e apenas os diodos D2 e D3 operam. Quando o ciclo se inverte os diodos D4 e D1 operam enquanto os diodos D2 e D3 permanecem em corte.

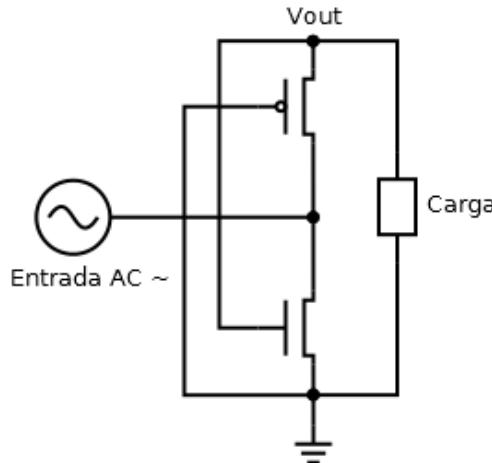

Figura 7 – Tradicional retificador de onda completa construído com ponte de diodos.

Os princípios de retificação para transformar sinais de RF em sinal retificado são os mesmos. Mas devido a baixa potência algumas particularidades devem ser consideradas e serão tratadas nas próximas seções.

#### 3.1 Tipos de Diodo (PN, Schottky e MOS)

Embora diodos convencionais sejam amplamente utilizados em retificadores, o emprego destes em microeletrônica de baixa potência pode se tornar impraticável devido a tensão de corte normalmente perto de 0,7V (19), o que inviabiliza sistemas que trabalham perto de 1V. Uma das soluções para contornar este problema é utilizar diodos Schottky que possuem menor tensão de limiar e baixa resistência (19). Contudo, a utilização de diodos Schottky em microeletrônica pode exigir etapas de produção extras que não estão disponíveis normalmente nos processos de fabricação tradicionais. Esses processos extras costumam ser mais caros que os processos comuns (34).

Outra solução largamente utilizada são transistores CMOS conectados e operando como diodos (35).

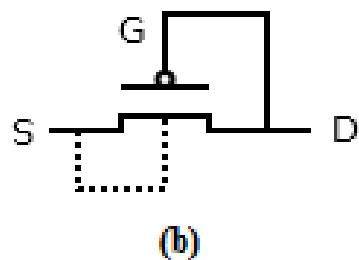

Um diodo ideal teria uma tensão de limiar inexistente, responderia a qualquer faixa de frequência e teria uma corrente reversa muito pequena. A configuração da figura 8 permite o diodo trabalhar em altas frequências (MHz) e ter uma pequena tensão de limiar, mas proporciona a existência de uma corrente reversa (35).

Figura 8 – Transistores CMOS conectados para trabalhar como diodos (35). (a) NMOS, (b) PMOS.

### 3.2 Funcionamento transistores MOS

A figura 9 apresenta dois circuitos com o objetivo de comparar o modo de funcionamento do transistor PMOS e NMOS. Antes que seja feita qualquer análise é importante lembrar que o transistor NMOS conduz (Liga) sempre que  $V_{gs}$  for maior que  $V_{th}$  e o transistor PMOS conduz sempre que  $V_{sg}$  for maior que  $V_{th}$  (36). Também importante é a informação que a fonte e o dreno dos transistores MOS não são fixos por dependerem dos níveis de tensão de cada terminal (36).

Na figura 9 (a) o transistor NMOS encontra-se conectado em um capacitor inicialmente descarregado. Para qualquer situação em que  $G = "0"$  o transistor está sempre em zona de corte (desligado) pois  $V_{gs}$  nunca será maior que  $V_{th}$  neste exemplo. Quando  $G = "1"$  e  $V_{in} = "1"$  o ponto A se torna o dreno (D) e o ponto B se torna a fonte (S). Assim surge uma corrente dreno-fonte que começa a carregar o capacitor até que  $V_{out}$  (S) assuma valor de tensão que torne  $V_{gs}$  menor ou igual a  $V_{th}$ . Nesse momento o transistor desliga, o capacitor para de carregar e permanece com tensão igual a  $V_{in} - V_{th}$ . Ainda na figura 9 (a), se o capacitor estiver totalmente carregado  $V_{out} = "1"$ ,  $G = "1"$  e  $V_{in} =$

Figura 9 – Circuitos esquemáticos de funcionamento dos transistores NMOS (a) e PMOS (b).

“0” o ponto A se torna a fonte (S) e o ponto B se torna o dreno (D). Assim, o capacitor começará a descarregar até que sua tensão se torne zero pois  $V_{gs}$  nunca será menor que  $V_{th}$  uma vez que a tensão de S é sempre zero.

Na figura 9 (b) o transistor PMOS encontra-se conectado em um capacitor inicialmente descarregado. Para qualquer situação em que  $G = 1$  o transistor está sempre em zona de corte (desligado) pois  $V_{sg}$  nunca será maior que  $V_{th}$  neste exemplo. Quando  $G = 0$  e  $V_{in} = 1$  o ponto A se torna a fonte (S) e o ponto B se torna o dreno (D). Assim, surge uma corrente fonte-dreno que carrega o capacitor completamente até que  $V_{out} = V_{in}$  pois  $V_{sg}$  é a todo momento maior que  $V_{th}$ . Quando o capacitor está completamente carregado,  $V_{out} = 1$ ,  $G = 0$  e  $V_{in} = 0$ , o ponto A se torna o dreno (D) e o ponto B se torna a fonte (S). Uma corrente fonte-dreno começa a descarregar o capacitor e a diminuir o potencial da fonte ( $V_s = V_{out}$ ). Quando  $V_s$  é suficientemente pequeno para que  $V_{sg}$  seja menor ou igual a  $V_{th}$  o transistor PMOS entra em corte (desliga). No equilíbrio o capacitor mantém uma pequena carga e uma tensão igual a  $V_{th}$ .

É possível concluir por esta análise que o transistor MOS tipo N liga com nível lógico alto “1” e desliga com nível lógico baixo “0” e ao mesmo tempo o transistor NMOS transmite bem níveis lógicos baixos “0” mas transmite mal níveis lógicos altos “1”. Por sua vez, transistores PMOS ligam com níveis lógicos baixos “0” e desligam com níveis lógicos altos “1” enquanto transmitem bem níveis lógicos altos “1” e transmite mal níveis lógicos baixos “0”.

A tabela 4 resume a relação abordada no trecho anterior:

Tabela 4 – Diferença entre funcionamento dos transistores PMOS e NMOS.

| Transistor MOS | Liga | Desliga | Transmite Bem | Transmite Mal |

|----------------|------|---------|---------------|---------------|

| N              | 1    | 0       | 0             | 1             |

| P              | 0    | 1       | 1             | 0             |

Toda a análise realizada até aqui é trivial e amplamente conhecida, mas esta seção em forma de “lembrete” se faz necessária pois todos esses conceitos serão implicitamente utilizados no decorrer da explicação de funcionamento dos tipos de retificadores.

### 3.3 Tipos de Retificadores

#### 3.3.1 Retificadores Passivos

Retificadores passivos são aqueles que não geram nenhum tipo de sinal secundário como auxílio para chavear o circuito.

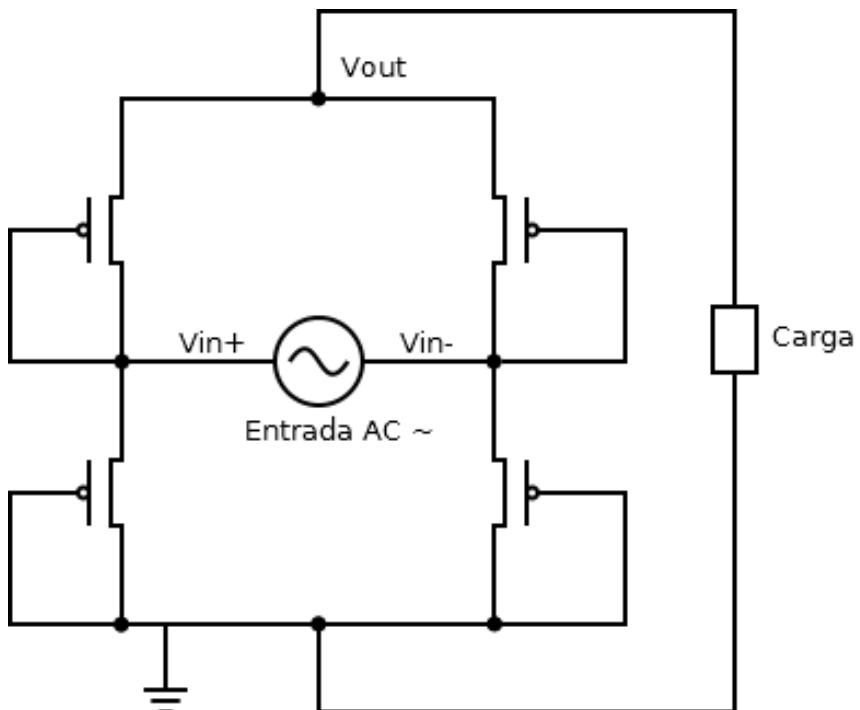

O retificador de onda completa utilizando transistores MOS conectados como diodos, figura 10, funciona exatamente como o tradicional retificador de ponte de diodos. Quatro transistores MOS são ligados em ponte e a condução acontece em pares alternando os ciclos de funcionamento. Essa configuração apesar de ter um rendimento maior do que o retificador de meia onda tem uma queda de tensão de  $2V_{th}$  em cada ciclo devido a utilização de dois transistores por ciclo (19). A tensão máxima de saída desse retificador é exibida na equação 3.1 (19).

$$V_{out} = 2V_{in} - 2V_{th} \quad (3.1)$$

Figura 10 – Esquema de retificador em ponte utilizando transistores CMOS como diodos (19).

A perda de potência nesse circuito ocorre principalmente pela resistência interna dos transistores que é diretamente relacionada as dimensões do transistor. O PCE deste

retificador é afetado principalmente pela resistência interna e pela corrente reversa que surge durante o chaveamento dos transistores. Essa corrente reversa pode ser minimizada ampliando a velocidade de chaveamento.

Existem algumas técnicas de configurações que podem otimizar o PCE e diminuir o valor da tensão de limiar  $V_{th}$  dos transistores. Essas técnicas estão comentadas nas próximas seções.

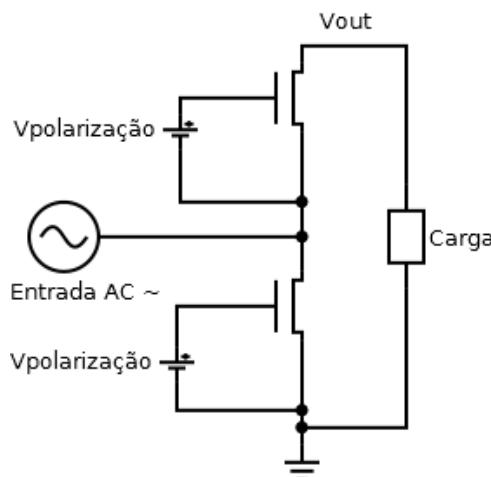

### 3.3.1.1 *External-V<sub>th</sub>-cancellation (EVC)*

A técnica de cancelamento de tensão de corte  $V_{th}$  por alimentação externa, *External-V<sub>th</sub>-cancellation (EVC)*, adiciona uma tensão de polarização entre o *gate* e o dreno de transistor MOS conforme figura 11. Enquanto a ponte de diodos construída com transistores MOS proporciona uma tensão máxima de saída de  $V_{out} = 2(V_{in} - V_{th})$ , a *EVC* substitui a tensão de limiar do transistor por  $V_{th}' = V_{th} - V_{polarização}$ . Essa nova tensão de corte  $V_{th}'$  faz com que a equação 3.1 mude conforme a equação 3.2 (19) e faz que a tensão de saída seja um pouco maior.

Figura 11 – Retificador com cancelamento de  $V_{th}$  por fonte externa (19).

$$V_{out} = 2 * (V_{in} - V_{th} + V_{polarização}) \quad (3.2)$$

### 3.3.1.2 *Self-V<sub>th</sub>-cancellation (SVC)*

Conforme esquematizado na figura 12, a técnica de auto cancelamento da tensão de corte, *Self-V<sub>th</sub>-cancellation (SVC)*, conecta os *gates* dos transistores NMOS e PMOS de maneira cruzada. Ao conectar o *gate* do transistor PMOS no referencial de terra e o *gate* do transistor NMOS em  $V_{out}$  se amplia a tensão entre *gate* e fonte, o que tem o mesmo efeito de se cancelar  $V_{th}$  (19).

A SVC é simples por polarizar estaticamente os transistores NMOS e PMOS. Está técnica reduz a tensão de corte  $V_{th}$ , o que aumenta a PCE do retificador, contudo, se

Figura 12 – Retificador com auto cancelamento de  $V_{th}$  (19).

a tensão  $V_{th}$  é muito pequena amplia-se a corrente reversa que reduz o PCE. Devido a essa característica é impossível ter baixa resistência interna e baixa corrente reversa utilizando-se SVC (19).

### 3.3.1.3 Retificador *Cross-Coupled*

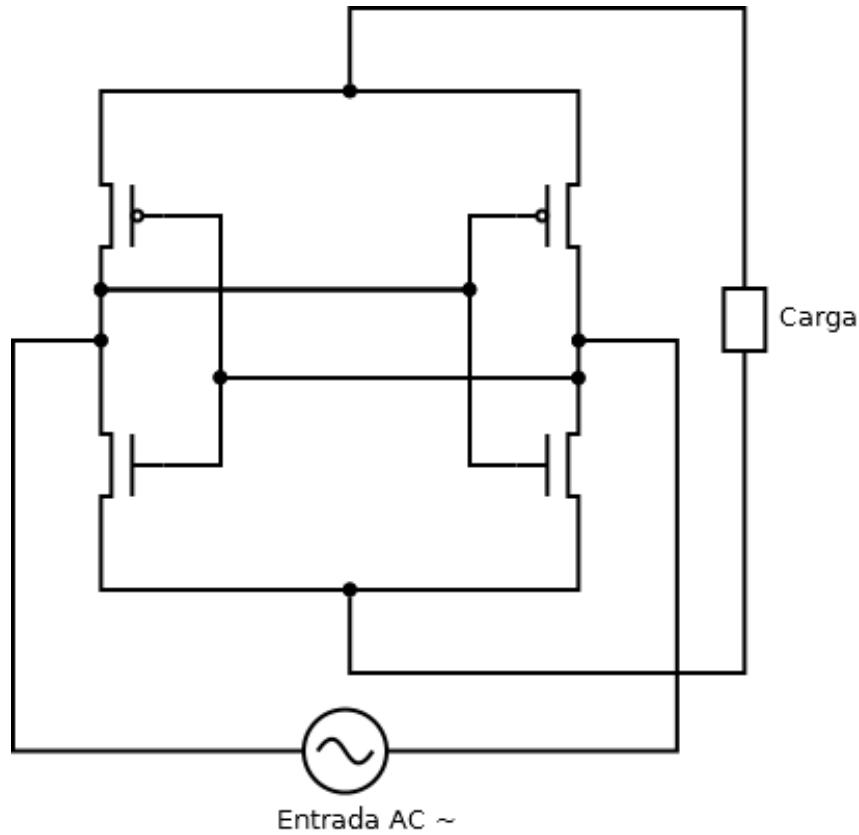

O retificador *Cross-Coupled*, figura 13, é uma montagem em ponte que liga os *gates* dos transistores também de forma cruzada. Contudo, ao invés dos *gates* dos transistores estarem polarizados pelo mesmo ciclo de tensão, eles são polarizados pelo ciclo de tensão oposto. Isto é, um transistor que conduz uma corrente derivada do ciclo positivo da fonte tem seu *gate* polarizado pelo ciclo negativo da fonte.

Esta configuração permite uma menor corrente reversa se comparado ao retificador em ponte utilizando transistores MOS conectados como diodos.

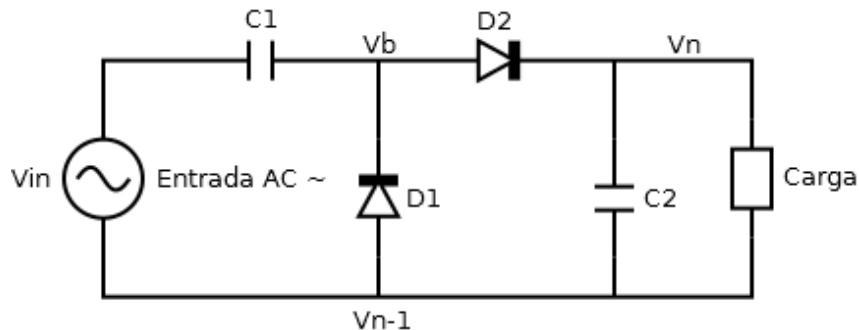

### 3.3.1.4 *Dickson Charge Pump*

O Dickson Charge Pump não é na essência um retificador por não separar um ciclo positivo de um ciclo negativo. Ele é um dobrador de tensão por ampliar todo o sinal sem manipular a forma de onda básica.

Uma variação do Dickson Charge Pump é o multiplicador de tensão. Ele coloca em sequência múltiplos estágios Charge Pump para elevar ainda mais a tensão. A figura 14 representa um único estágio do multiplicador de tensão.

Durante o ciclo negativo da fonte  $V_{n-1} > V_b$ , então o diodo D1 conduz e carrega C1 enquanto o diodo D2 está em corte. No final deste ciclo  $V_b = V_{in} + V_{n-1} - V_{th}$ . Quando o ciclo positivo se inicia  $V_b > V_{n-1}$  então o diodo D1 entra em corte e D2 começa a conduzir e a carregar C2. Nesse momento  $V_n = V_b + V_{in} - V_{th}$  (19), contudo,

Figura 13 – Esquema de retificador Cross-Coupled (37).

Figura 14 – Esquemático de um único estágio do multiplicador de tensão Dickson Charge Pump (19).

substituindo  $V_b$  teremos:

$$V_n = V_{in} + V_{n-1} - V_{th} + V_{in} - V_{th} \quad (3.3)$$

$$V_n = V_{n-1} + 2V_{in} - 2V_{th}. \quad (3.4)$$

Para  $N$  estágios cascateados a tensão de saída do multiplicador de tensão será dada

pela equação 3.5.

$$V_n = 2N(V_{in} - V_{th}) \quad (3.5)$$

Pela equação 3.5 o principal limitador da tensão gerada pelo multiplicador *Charge Pump* é a tensão de corte  $V_{th}$ .

### 3.3.2 Retificadores Ativos

Ao contrário dos retificadores passivos, os ativos utilizam mecanismos de controle de sinais que interferem no processo de retificação com o objetivo de ampliar a eficiência. Os principais tipos de retificadores ativos disponíveis atualmente na literatura para utilização em circuitos integrados de baixa potência são os retificadores ativos que utilizam comparadores e os retificadores 1X/2X reconfiguráveis. Nesta seção abordaremos as principais características destes retificadores.

#### 3.3.2.1 Retificador Ativo com Comparadores

O retificador ativo com comparadores vem sendo frequentemente estudado em diversos trabalhos (33), (38), (39). O que sugere que atualmente são uma boa opção para retificação de sinais de rádio frequência.

O funcionamento deste tipo de retificador é baseado no retificador Cross-Coupled (3.3.1.3). Alguns de seus transistores, podem ser todos ou apenas um par, ao invés de terem seus *gates* ligados de forma cruzada tem a tensão de *gate* controlada pela ação de comparadores que ligam e desligam os transistores, minimizando assim a corrente reversa que surge durante a mudança de ciclos. Como já mencionado em 3.3.1.3 a corrente reversa é uma das principais razões pela diminuição do PCE do retificador.

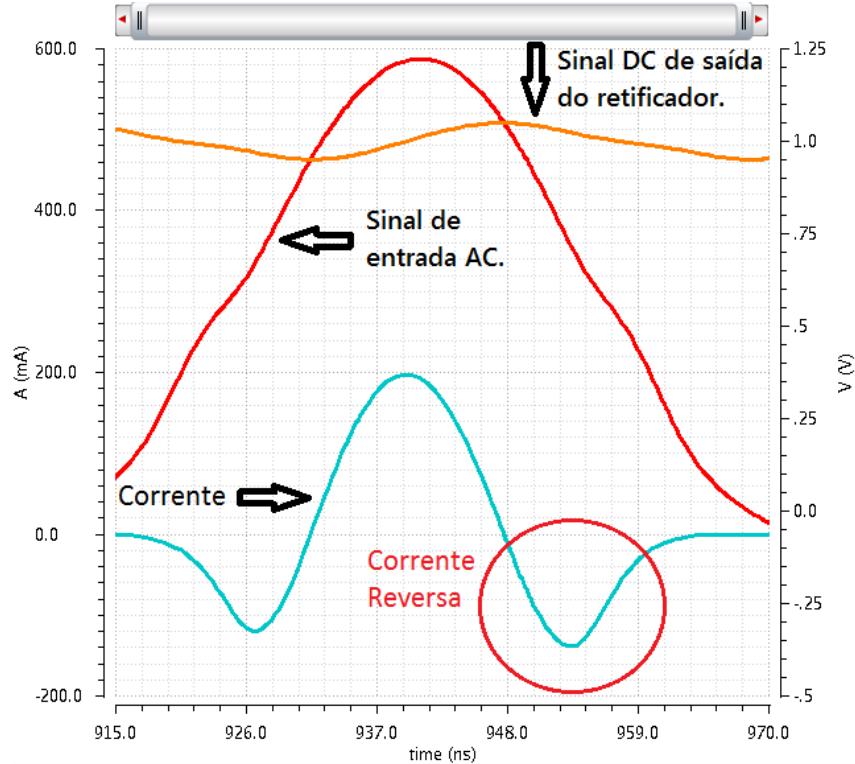

Na figura 15 são apresentadas três curvas extraídas de um retificador Cross-Coupled. Em destaque dentro do círculo é exibida, de forma exagerada, a corrente reversa que diminui a eficiência deste tipo de retificador. O objetivo do retificador utilizando comparadores é acelerar o processo de chaveamento dos transistores e eliminar essa corrente.

Um dos problemas da implementação deste tipo de retificador ativo está no projeto dos comparadores. Para este circuito é desejado que os comparadores sejam os mais rápidos possível, para diminuir ao máximo a corrente reversa, consumam pouca potência, ocupem pouca área de silício, e, preferencialmente, sejam auto polarizáveis sem a necessidade de alimentação externa.

Apesar de diferentes estudos alterarem algumas características básicas do corpo do retificador a figura 16 exibe uma configuração que tem se tornado popular entre os trabalhos mais recentes nessa área (33), (40), (41). Nesta configuração duas características

Figura 15 – Forma de onda do funcionamento de um retificador Cross-Coupled com destaque para a corrente reversa.

principais devem ser observadas: Apenas um par de comparadores atua no circuito, o que gera um resultado muito próximo ao resultado de quando se usam 4 comparadores mas com a metade do consumo, e geralmente estes comparadores controlam os transistores tipo P pois ligar um transistor colocando-o em referencial de terra é mais fácil do que prover uma tensão estável VDD para um circuito sem alimentação auxiliar.

Figura 16 – Esquema de retificador ativo utilizando comparadores.

Mesmo que o projeto do comparador não seja trivial, sua forma de funcionamento ideal é simples de ser explicada. O comparador deve monitorar os sinais de tensão de saída e de entrada. Pela figura 15, quando a tensão de entrada se torna maior que a tensão de saída o comparador deve ligar o transistor e quando a tensão de entrada se torna menor que a tensão de saída o comparador deve desligar imediatamente o transistor. Esse funcionamento ideal, apesar de simples, é comprometido devido ao atraso do comparador entre monitorar os sinais de tensão e ligar e desligar o transistor. Quanto menor for o atraso nesse processo menor será a corrente reversa.

Como já mencionado em 3.2, o dreno e a fonte dos transistores MOS não são fixos por dependerem dos níveis de tensão dos terminais. A corrente reversa surge quando o comparador atrasa em desligar o transistor e a tensão de saída fica maior que a tensão de entrada por algum tempo. Esse pequeno tempo em que isso ocorre provoca a troca no transistor das posições de dreno e fonte, o que cria a corrente reversa. Se o comparador muda a tensão do *gate* do transistor imediatamente quando as tensões de entrada e saída se tornam iguais, mesmo que fonte e dreno se alternem não existem condições para o surgimento da corrente reversa.

### 3.3.2.2 Retificador 1X/2X Reconfigurável

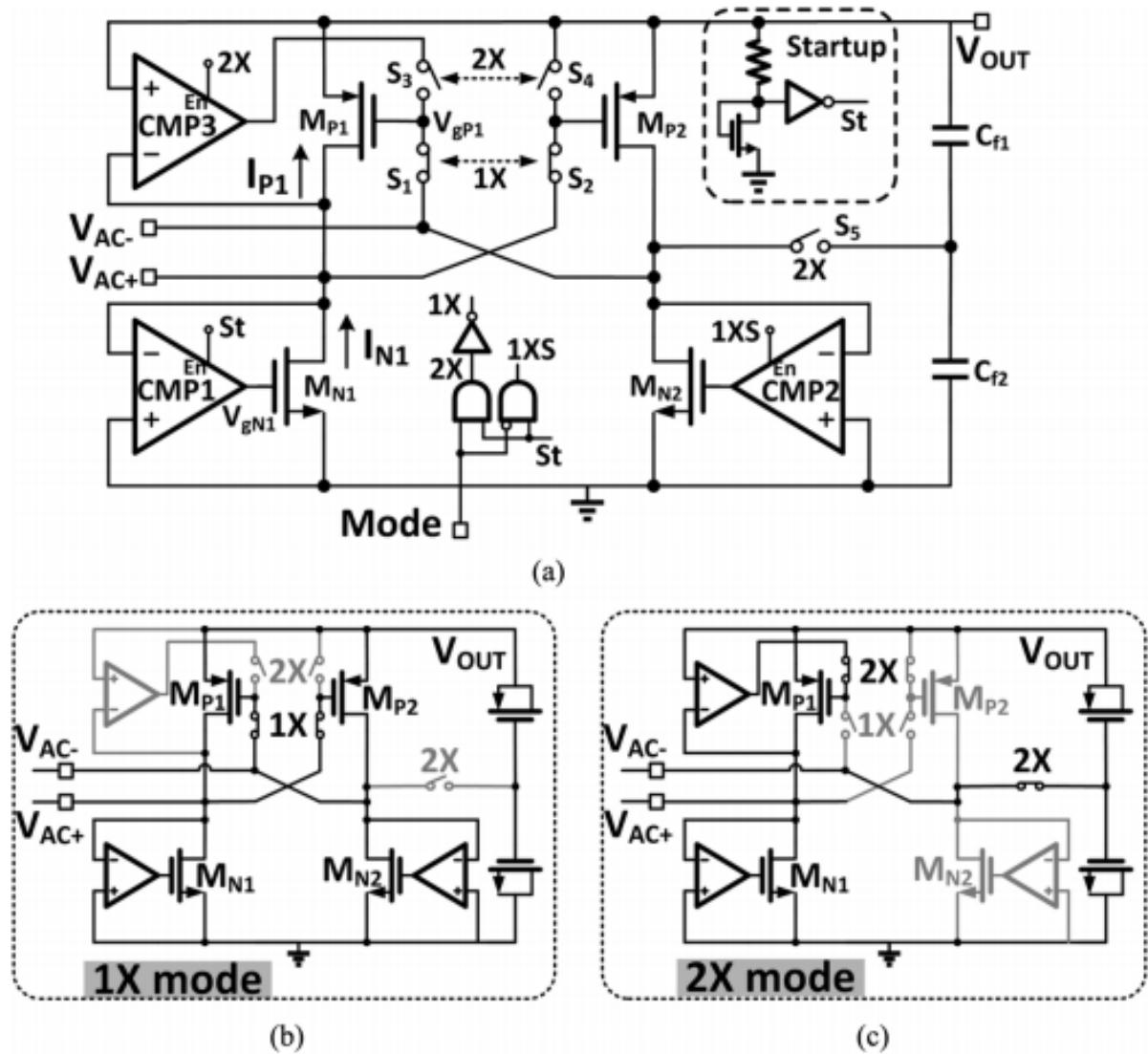

A transferência de energia por rádio frequência enfrenta alguns desafios de estabilidade. No pior caso, a fonte de energia estará localizada na distância máxima de funcionamento provendo o mínimo necessário de energia para alimentar os circuitos do chip receptor. Contudo, situações onde a fonte de energia está localizada próxima ao receptor podem prover energia em excesso que se captada pelo receptor, e posteriormente dissipada pelo circuito de limitação, podem gerar aquecimento e queima de tecidos. Outras situações adversas seriam a variação intermitente da distância entre fonte e receptor, o que deixaria instável o sinal, e a mudança de ângulo entre o chip fonte e o chip receptor, o que mudaria o acoplamento e também deixaria instável o sinal.

Retificadores 1X/2X reconfiguráveis dispõem de dois modos de operação (Modo 1X e Modo 2X) que podem ser chaveados para adaptar o retificador às condições de sinal recebidas. Geralmente o modo de operação 1X cobre sinais de grande amplitude e o modo de operação 2X sinais de baixa amplitude. Assim, quando a fonte de energia está localizada próximo do circuito receptor, e o ângulo entre receptor e fonte é ideal, o circuito opera em modo 1X e desliga sub-circuitos de operação do modo 2X. Quando a situação é diferente, e a amplitude do sinal é baixa, o circuito chaveia, liga sub-circuitos do modo de operação 2X e consegue operar nessa faixa de amplitude. Em situações intermediárias também é possível que o retificador funcione como uma espécie de PWM chaveando entre os modos de operações 1X e 2X para modular o sinal recebido adequando-o as necessidades do projeto.

A figura 17 (a) exibe o retificador reconfigurável 1X/2X proposto em (42). Quando em modo 1X, o retificador funciona como um retificador ativo com comparadores, figura 17 (b), em modo 2X, figura 17 (c), este chaveia o circuito para trabalhar como um dobrador de tensão através de dois retificadores de meia onda (42).

Figura 17 – (a) Retificador 1X/2X Reconfigurável, (b) Modo 1X, (c) Modo 2X (42).

# 4 Comparadores

Como abordado em 3.3.2.1 comparadores são muitas vezes utilizados em retificadores ativos. O tipo de comparador utilizado na retificação de sinais de rádio frequência exige que o consumo seja baixo, a velocidade de operação seja alta e a polarização seja feita preferencialmente sem o uso de fontes externas.

O funcionamento macro de todos os comparadores para este tipo específico de aplicação é sempre o mesmo. Os sinais de tensão de entrada e saída do retificador são monitorados. Quando o sinal de entrada é maior do que o sinal de saída o comparador chaveia e quando o sinal de entrada se torna menor que o sinal de saída o comparador chaveia novamente.

Neste capítulo abordaremos alguns exemplos e implementação deste tipo de comparador.

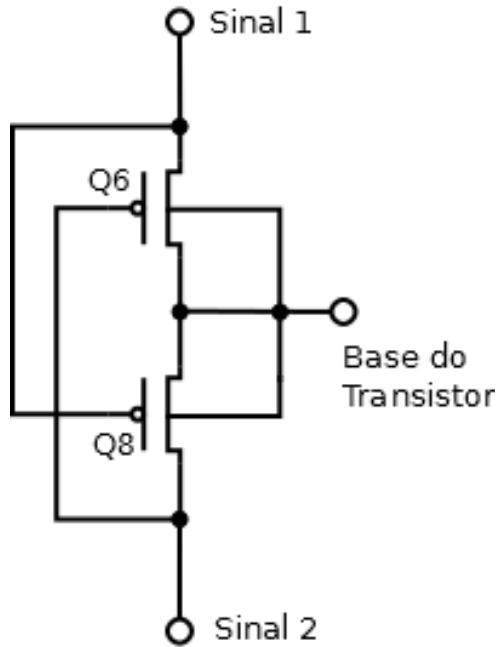

## 4.1 Comparador *Two-input Common-gate*

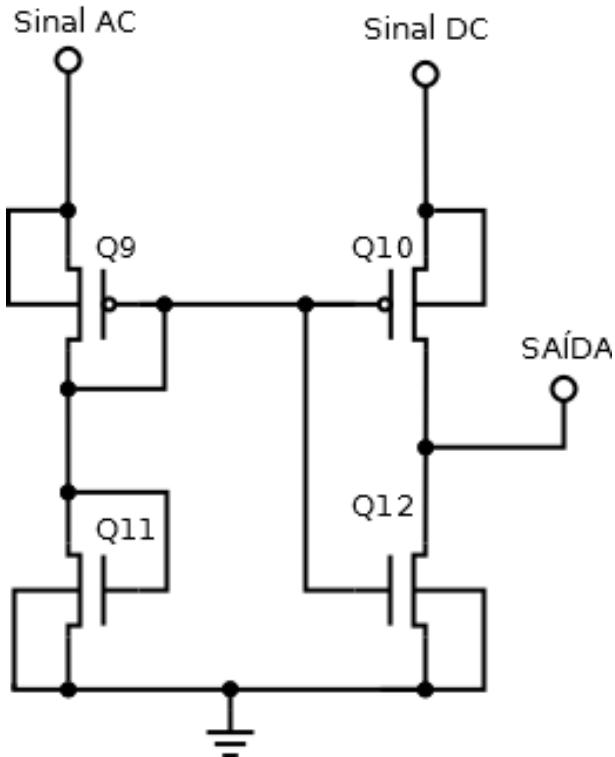

O Comparador *Two-input Common-gate* (Comparador de duas entradas e *gate* comum) é o comparador base utilizado em vários trabalhos, algumas vezes adicionando-se pequenos circuitos ou realizando-se pequenas modificações (34), (41), (40) e (33). O nome do comparador *Two-input Common-gate* (figura 18) é originado pelas duas entradas que monitoram a tensões de entrada e saída do retificador (Sinal AC e Sinal DC) e pelos *gates* dos quatro transistores MOS que estão todos curto circuitados.

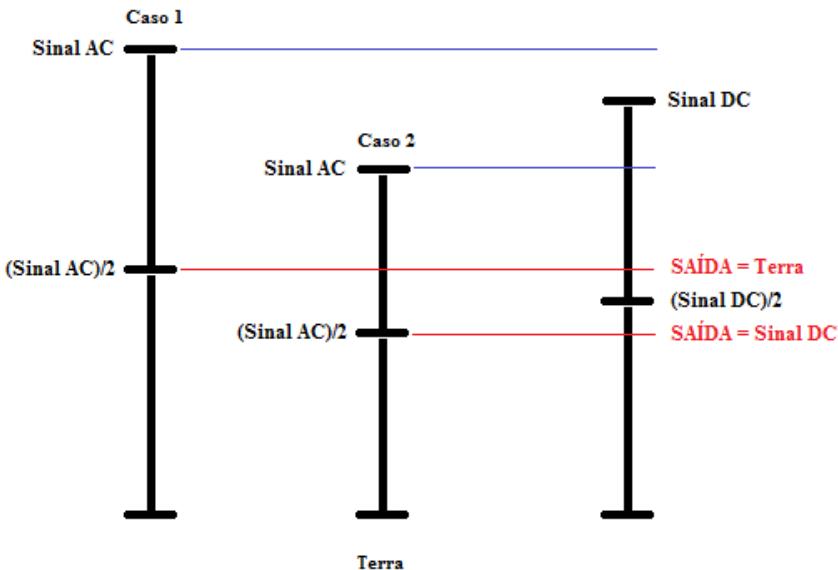

Os transistores Q10 e Q12 formam um inversor que disponibiliza sinal de terra ou Sinal DC na SAÍDA. Sempre que a tensão do *gate* dos transistores Q10 e Q12 é maior do que  $(\text{Sinal DC})/2$  a SAÍDA estará em nível de terra e sempre que a tensão no *gate* dos transistores Q10 e Q12 for menor do que  $(\text{Sinal DC})/2$  a SAÍDA terá tensão igual a Sinal DC. Os transistores Q9 e Q11 formam um divisor de tensão projetado para gerar uma tensão próxima de  $(\text{Sinal AC})/2$  no *gate* de todos os transistores. Deste modo, sempre que a tensão Sinal AC é maior do que a tensão Sinal DC a tensão derivada do divisor de tensão aplicada no *gate* de todos os transistores é maior do que a metade de Sinal DC. Ou seja, sempre que Sinal AC se tornar maior ou menor do que Sinal DC a tensão gerada pelo divisor de tensão Q9-Q11 fará o inversor Q10-Q12 chavear.

A figura 19 esquematiza o funcionamento do comparador. No caso 1 a tensão Sinal AC é maior do que a tensão Sinal DC e a SAÍDA tem tensão de terra. No caso 2 a tensão Sinal AC é menor do que Sinal DC e a SAÍDA tem tensão igual a Sinal DC.

Figura 18 – Comparador *Two-input Common-gate* (33).Figura 19 – Esquemático de funcionamento do comparador *Two-input Common-gate*.

## 4.2 Comparador Principal Acompanhado de Comparador Auxiliar.

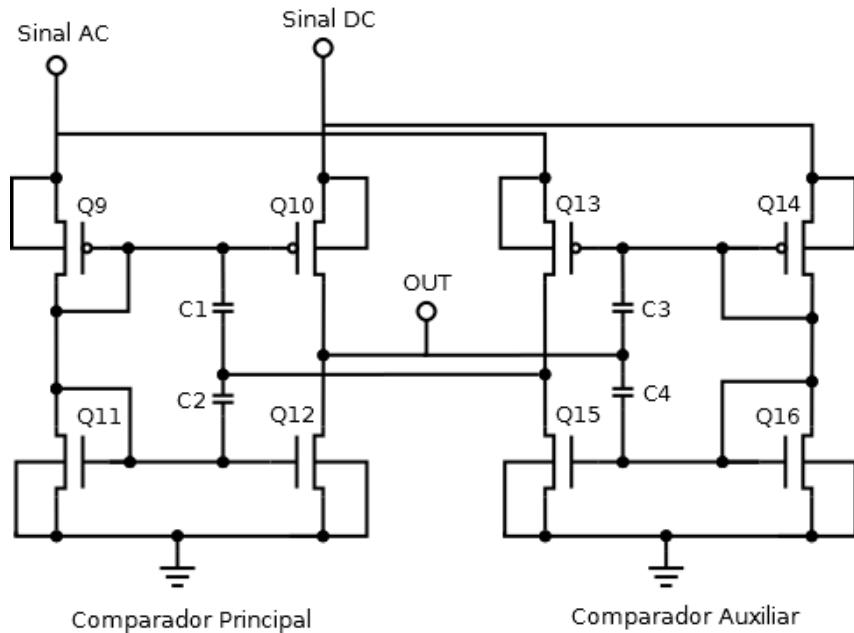

O comparador da figura 20 foi proposto em (33). Este comparador é baseado no comparador *Two-input Common-gate*.

Um dos problemas apresentados pelo Comparador *Two-input Common-gate* é que o tempo de ação para “ativar” o comparador é menor do que o tempo de ação para “desativar”. Isto faz que o atraso para o comparador “desativar” seja maior do que o atraso

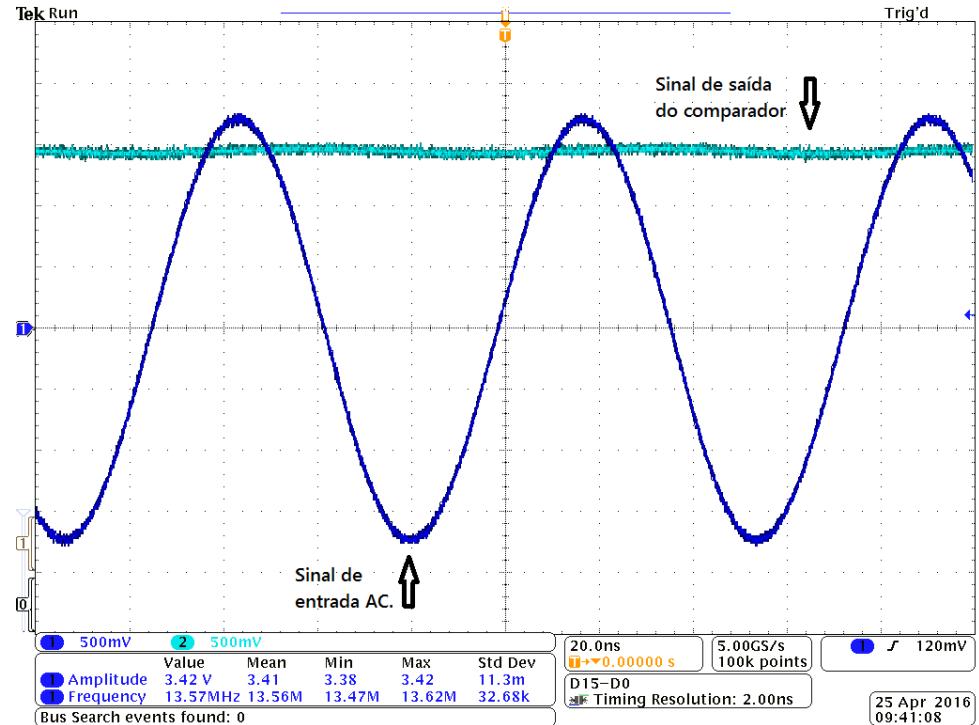

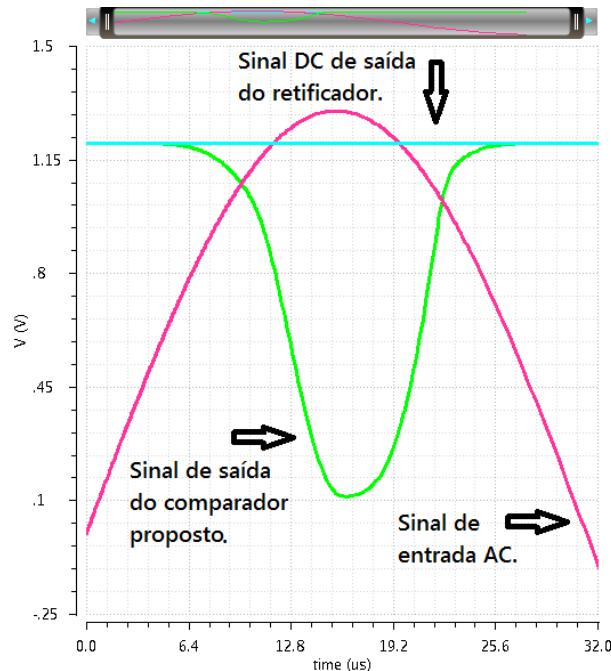

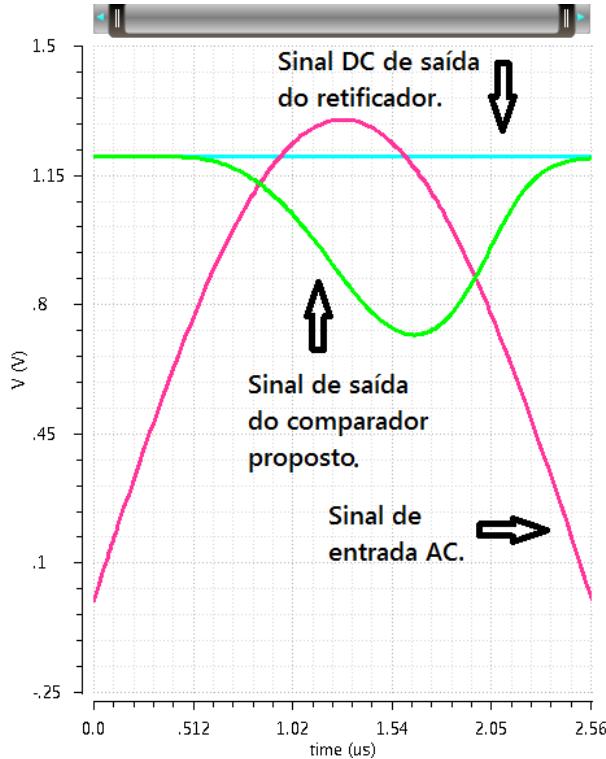

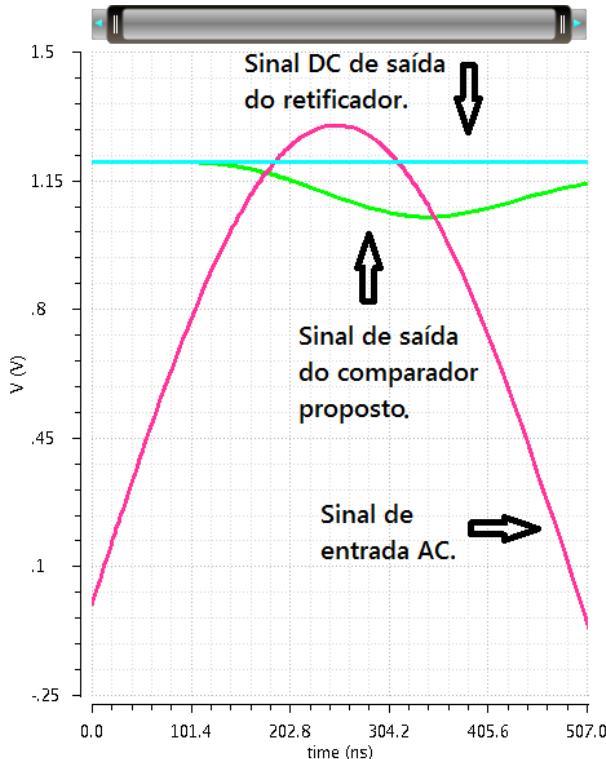

Figura 20 – Comparador apresentado em (33)