#### UNIVERSIDADE FEDERAL DE ITAJUBÁ

## PROGRAMA DE PÓS-GRADUAÇÃO EM ENGENHARIA ELÉTRICA

**Paola Karelys Lioy Matute**

# Uma metodologia de projeto de conversor A/D SAR-PWM híbrido

Novembro de 2017

#### UNIVERSIDADE FEDERAL DE ITAJUBÁ

## PROGRAMA DE PÓS-GRADUAÇÃO EM ENGENHARIA ELÉTRICA

**Paola Karelys Lioy Matute**

# Uma metodologia de projeto de conversor A/D SAR-PWM híbrido

Dissertação submetida ao Programa de Pós-Graduação em Engenharia Elétrica como parte dos requisitos para obtenção do Título de Mestre em Ciências em Engenharia Elétrica.

Área de Concentração: Microeletrônica

Orientador: Prof. Dr. Robson Luiz Moreno

Co-orientador: Prof. Dr. Gustavo Della Colletta

Novembro de 2017

Itajubá – MG

#### Resumo

Este trabalho propõe uma metodologia de projeto para o desenho de uma nova arquitetura de conversão analógico digital A/D por aproximação sucessiva, com o uso de um circuito modulador de pulso (PWM) híbrido baseado em contadores e linhas de atrasos no estágio de conversão D/A. Esta técnica de conversão consegue aumentar a resolução do circuito e diminuir a necessidade de um ciclo de relógio muito alto, em comparação com a técnica de conversão A/D, a qual utiliza um PWM baseado em contadores como conversor A/D. A metodologia de projeto proposta considera o erro de propagação da rede de atrasos gerado pela tolerância dos componentes que o formam, a fim de definir uma quantidade máxima de resolução do circuito que garanta que este seja monotônico, sem perda de códigos, e assegurando o seu correto funcionamento.

#### Summary

This work proposes a project methodology for the design of a new digital analog A/D conversion architecture by successive approximation with the use of a hybrid pulse modulator (PWM) circuit based on counters and delay lines in the conversion stage D/A. This technique of conversion can increase the circuit resolution and decrease the need for a very high clock cycle, compared to the A / D conversion technique, which uses a PWM based on counters as an A / D converter [1]. The proposed design methodology considers the propagation error of the delay network generated by the tolerance of the components that form it, in order to define a maximum amount of resolution of the circuit that guarantees that it is monotonic and without loss of codes, and assuring its correct operation.

#### Sumário

| 1. | Intr  | odução                                                         | 1  |

|----|-------|----------------------------------------------------------------|----|

|    | 1.1.  | Visão Geral                                                    | 1  |

|    | 1.2.  | Organização do trabalho                                        | 3  |

| 2  | . Rev | visão bibliográfica                                            | 4  |

| 2  | 1.Cor | nversor A/D                                                    | 4  |

|    | 2.2.  | Conversor A/D SAR                                              | 4  |

|    | 2.3.  | Conversor A/D SAR PWM                                          | 5  |

|    | 2.3   | .1. Filtro passa baixa                                         | 6  |

|    | 2.4.  | Especiações de conversores D/A                                 | 7  |

|    | 2.4   | .1. Resolução                                                  | 7  |

|    | 2.4   | .2. Tempo de estabelecimento                                   | 8  |

|    | 2.4   | .3. Monoticidade                                               | 11 |

|    | 2.4   | .4. Perda de código                                            | 11 |

|    | 2.5.  | Arquitetura PWM linhas de atrasos                              | 11 |

|    | 2.6.  | Arquitetura PWM com linha de atraso segmentada                 | 12 |

|    | 2.7.  | Arquitetura PWM híbrida                                        | 12 |

|    | 2.8.  | Erro padrão                                                    | 13 |

|    | 2.9.  | Propagação de incertezas                                       | 14 |

| 3  | Arq   | uitetura proposta                                              | 15 |

|    | 3.1.  | Arquitetura de conversão A/D SAR                               | 16 |

|    | 3.2.  | Técnica PWM híbrida                                            | 16 |

| 4  | Me    | todologia proposta                                             | 21 |

|    | 4.1.  | Resolução da rede de atrasos                                   | 21 |

|    | 4.2.  | Cálculo da propagação de erros e incertezas da rede de atrasos | 23 |

|    | 4.3.  | Resolução máxima da rede de atrasos                            | 24 |

|    | 4.4.  | Resolução DAC PWM                                              | 25 |

|    | 4.5.  | Número de portas nos elementos de atrasos                      | 25 |

|    | 4.6.  | Frequência PWM                                                 | 26 |

|    | 4.7.  | Frequência SAR                                                 | 26 |

|    | 4.8.  | Taxa de amostragem                                             | 28 |

|    | 4.9.  | Diagrama de fluxo da metodologia de projeto proposta           | 28 |

| 5. Re | esulta | ados                                       | 29 |

|-------|--------|--------------------------------------------|----|

|       |        | lidação da metodologia de projeto proposta |    |

| 5.2.  | Val    | lidação da arquitetura proposta            | 46 |

| 5     | 2.1.   | Validação do circuito PWM DAC híbrido      | 46 |

| 5     | 2.2.   | Validação do circuito SAR ADC PWM          | 54 |

| 6. Co | onclu  | são e trabalhos futuros                    | 59 |

| 6.1.  | Co     | nclusão                                    | 59 |

| 6.2.  | Tra    | abalhos futuros                            | 60 |

## Lista de figuras

| Figura (2. 1). Conversão analógico-digital                                      | 4     |

|---------------------------------------------------------------------------------|-------|

| Figura (2. 2). Blocos básicos do SAR                                            | 5     |

| Figura (2. 3). Conversor A/D SAR DAC PWM [1]                                    | 5     |

| Figura (2. 4). Lógica do circuito modulador PWM [7]                             | 6     |

| Figura (2. 5). Forma de onde de um sinal PWM típico                             | 6     |

| Figura (2. 6). Filtro passa baixas para um sinal PWM                            | 7     |

| Figura (2. 7). Resolução da conversão D/A                                       | 8     |

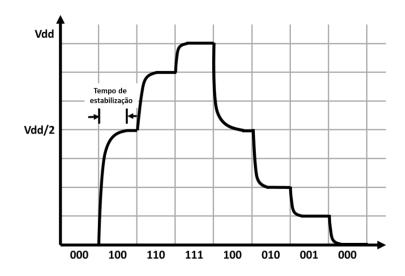

| Figura (2. 8). Tempo de estabelecimento do conversor A/D                        | 9     |

| Figura (2. 9). Tempo de estabelecimento do conversor D/A com entrada SAR.       | 9     |

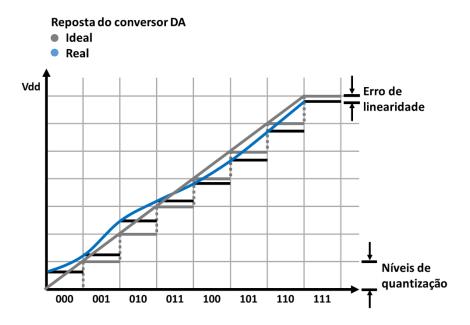

| Figura (2. 10). Erro de linearidade em um conversor D/A                         | 10    |

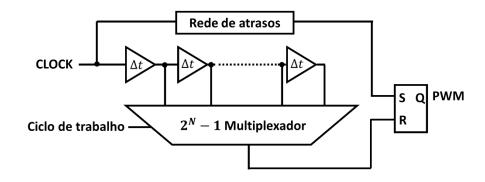

| Figura (2. 11). Arquitetura PWM linhas de atrasos [14]                          | 11    |

| Figura (2. 12). Arquitetura PWM linha de atraso segmentada [15]                 | 12    |

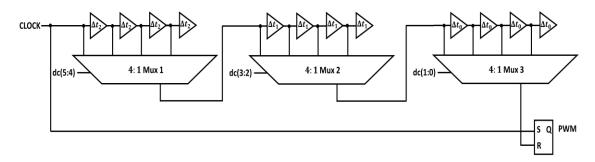

| Figura (2. 13). Arquitetura PWM híbrida baseada em contadores e linhas de at    | rasos |

| [16]                                                                            | 13    |

|                                                                                 |       |

| Figura (3. 1). Conversor A/D SAR PWM híbrido                                    | 15    |

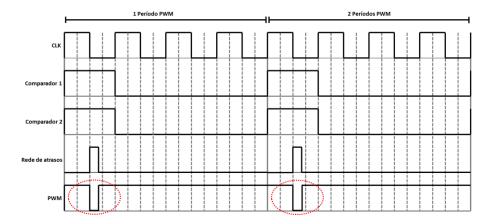

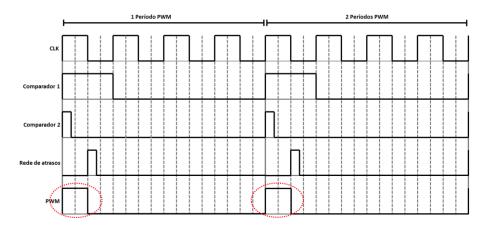

| Figura (3. 2).Formas das ondas do sinal PWM                                     | 17    |

| Figura (3. 3). Comportamento dos sinais dos blocos contador e comparador 1.     | 17    |

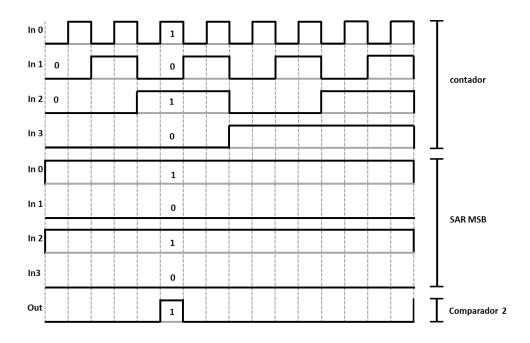

| Figura (3. 4). Comportamento dos sinais no bloco comparador MSB                 | 18    |

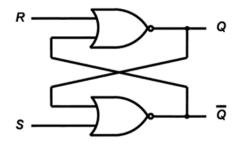

| Figura (3. 5). Rede de habilitação                                              | 18    |

| Figura (3. 6). Comportamento dos sinais ao longo do tempo na rede de habilita   | ıção. |

|                                                                                 | 19    |

| Figura (3. 7). Funcionamento da rede de atrasos                                 | 20    |

| Figura (3. 8). Incremento de ajuste fino no ciclo de trabalho do sinal PWM base | ado   |

| na sequência de entrada da rede de atrasos                                      | 20    |

|                                                                                 |       |

| Figura (4. 1). Erro de propagação na rede de atrasos                            | 21    |

| Figura (4. 2). Saída do flip flop SR gerador do sinal PWM com erro              | 22    |

| Figura (4. 3). Saída do flip flop SR gerador do sinal PWM                       | 22    |

| Figura (4. 4). Amplitude da ondulação                                           | 26    |

| Figura (4. 5). Diagrama de bode em função da frequência e a atenuação           | 27    |

| Figura (4. 6). Acomodação do sinal PWM dentro da faixa de tensão correspondente.      |

|---------------------------------------------------------------------------------------|

| 2                                                                                     |

| Figura (4. 7). Voltagem de um capacitor em relação ao tempo3                          |

| Figura (5. 1). Rede de atrasos sem erro de propagação3                                |

| Figura (5. 2). Rede de atrasos sem erro de propagação3                                |

| Figura (5. 3). Rede de atrasos com erro de propagação com aumento do valor de         |

| atraso do pulso de um erro padrão3                                                    |

| Figura (5. 4). Rede de atrasos com erro de propagação com diminuição do valor de      |

| atraso do pulso de um erro padrão3                                                    |

| Figura (5. 5). Circuito RC3                                                           |

| Figura (5. 6). Tempo de acomodação no sinal de saída do filtro RC3                    |

| Figura (5. 7).constantes de tempo necessárias para as diferentes resoluções a         |

| valores da variável $a$ 4                                                             |

| Figura (5. 8). Tempo de acomodação do sinal para diferentes valores da variável $a$ . |

| 4                                                                                     |

| Figura (5. 9). Circuito DAC PWM4                                                      |

| Figura (5. 10). Flip Flop SR4                                                         |

| Figura (5. 11). Elementos de atrasos com implementações de portas OR4                 |

| Figura (5. 12). Comportamento dos sinais PWM com um incremento máximo de              |

| ajuste grosso e fino no ciclo de trabalho4                                            |

| Figura (5. 13). Comportamento dos sinais PWM com um incremento máximo de              |

| ajuste grosso e fino no ciclo de trabalho com redução no tamanho do pulso do sinal    |

| RESET4                                                                                |

| Figura (5. 14). Comportamento dos sinais PWM sem incremento de ajuste grosso e        |

| incremento no ajuste fino no ciclo de trabalho4                                       |

| Figura (5. 15). Comportamento dos sinais PWM sem incremento de ajuste grosso e        |

| incremento no ajuste fino no ciclo de trabalho, com diminuição no tamanho do pulso    |

| no sinal SET4                                                                         |

| Figura (5. 16). Circuito redutor de ciclo de trabalho                                 |

| Figura (5. 17). Comportamento do sinal ao longo do tempo do circuito redutor de       |

| ciclo de trabalho4                                                                    |

| Figura (5. 18). Comportamento do circuito DAC PWM híbrido para um código de    |   |

|--------------------------------------------------------------------------------|---|

| entrada 00000015                                                               | 1 |

| Figura (5. 19). Comportamento do circuito DAC PWM híbrido para um código de    |   |

| entrada 000100052                                                              | 2 |

| Figura (5. 20). Comportamento do circuito DAC PWM híbrido para um código de    |   |

| entrada 100000052                                                              | 2 |

| Figura (5. 21). Comportamento do circuito DAC PWM híbrido para um código de    |   |

| entrada 111111153                                                              | 3 |

| Figura (5. 22). Resposta do conversor DAC PWM híbrido para um código de ajuste |   |

| grosso de 000053                                                               | 3 |

| Figura (5. 23). Resposta do conversor DAC PWM híbrido para um código de ajuste |   |

| grosso de 100054                                                               | 4 |

| Figura (5. 24). Resposta do conversor DAC PWM híbrido para um código de ajuste |   |

| grosso de 111154                                                               | 4 |

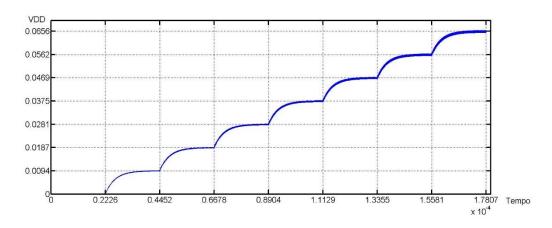

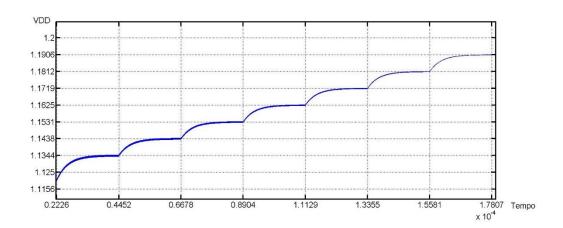

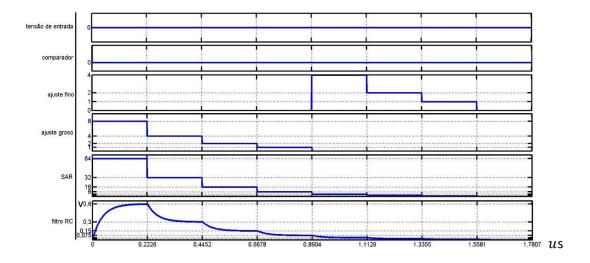

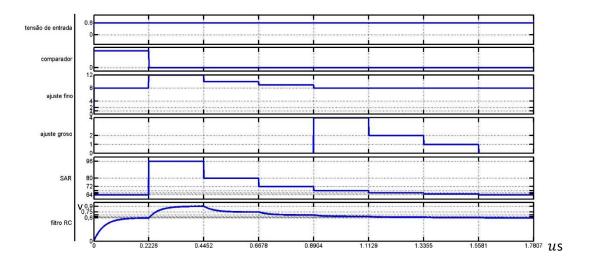

| Figura (5. 25). Funcionamento do conversor A/D com tensão de entrada 0 V5      | 5 |

| Figura (5. 26). Funcionamento do conversor A/D com tensão de entrada 0.6 V50   | 6 |

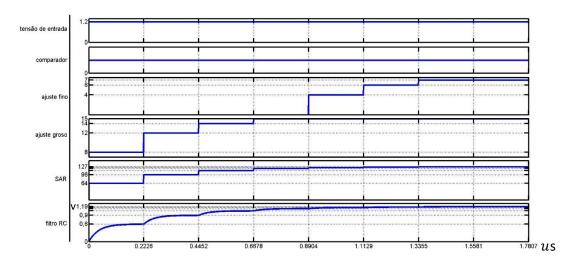

| Figura (5. 27). Funcionamento do conversor A/D com tensão de entrada 1.2 V50   | 6 |

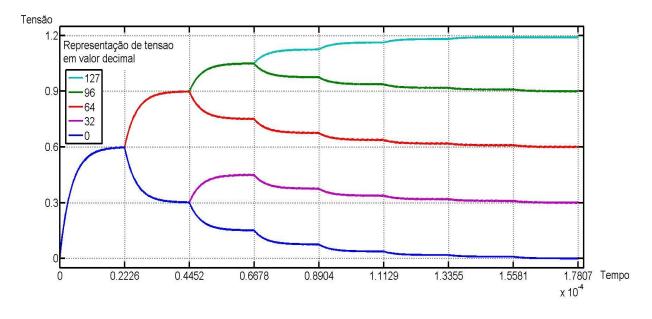

| Figura (5. 28). Resposta transiente da saída do DAC58                          | 8 |

|                                                                                |   |

#### Lista de tabelas

| Tabela (3. 1) Sequência da memória de acordo com o código de entrada19          |

|---------------------------------------------------------------------------------|

| Tabela (5. 1). Amplitude da ondulação de acordo com a variável a35              |

| Tabela (5. 2). Calculo da Resolução máxima da rede de atrasos41                 |

| Tabela (5. 3). Calculo da resolução DAC PWM42                                   |

| Tabela (5. 4). Calculo do número de portas logicas no elemento de atraso42      |

| Tabela (5. 5). Calculo da frequência DAC PWM43                                  |

| Tabela (5. 6). Calculo da constante de tempo do filtro passa baixas RC43        |

| Tabela (5. 7). Calculo do percentual de acomodação do filtro passa baixas RC43  |

| Tabela (5. 8). Calculo do tempo de acomodação do filtro passa baixas RC44       |

| Tabela (5. 9). Calculo do número de constantes de tempo44                       |

| Tabela (5. 10). Calculo da frequência SAR45                                     |

| Tabela (5. 11). Calculo da frequência de amostragem45                           |

| Tabela (5. 12). Tabela da verdade do flip flop D47                              |

| Tabela (5. 13). Tabela da verdade da porta AND com a entrada B invertida49      |

| Tabela (5. 14). Etapas de conversão do conversor A/D para uma tensão de entrada |

| de 0 V57                                                                        |

| Tabela (5. 15). Etapas de conversão do conversor A/D para uma tensão de entrada |

| de 0 V57                                                                        |

| Tabela (5. 16). Etapas de conversão do conversor A/D para uma tensão de entrada |

| de 0 V58                                                                        |

## Lista de diagramas

| Diagrama (4. 1 ) Representação gráfica da metodologia de projeto proposta   | 28 |

|-----------------------------------------------------------------------------|----|

|                                                                             |    |

|                                                                             |    |

| Diagrama (5, 1). Comportamentos do sinal PWM de acordo com a variável $a$ , | 37 |

#### 1. Introdução

#### 1.1. Visão Geral

Um conversor análogo digital (ADC) é um circuito eletrônico integrado cuja saída é a palavra digital, resultado de converter o sinal analógico de entrada. Esta conversão é muito importante para qualquer sistema digital, devido a natureza dos sinais que é analógica, e é necessária uma interface que permita a sua interpretação.

Estes circuitos conversores podem ser usados, por exemplo, para converter sinais de sensores de temperatura e movimento para monitoramento de atletas, monitoramento de glicose com sensor e circuito de tratamento de sinal utilizando como base lentes de contato [2] e medição de pressão arterial de forma remota através de dispositivos implantáveis [3].

A maioria dos sinais biomédicos são frequentemente lentos e apresentam uma faixa dinâmica limitada. A digitalização de sinais biomédicos normalmente é realizada com resolução moderada (8-12) bits e uma taxa de amostragem de (1-1000kS/s) [4]. Em vários dispositivos, a eficiência energética e a duração da bateria são metas primordiais [5]. Particularmente, ADCs para dispositivos médicos implantados precisam de operação de microwatt para funcionar em uma bateria pequena por décadas [6]. Portanto, a eficiência energética é um desafio crítico para o projeto dos ADCs.

Entre as técnicas de conversão encontra-se a sigma-delta que é constantemente utilizada para baixas taxas de amostragem e altas resoluções (aproximadamente 12-14 bits). Por outro lado, a técnica de conversão pipeline é utilizada para aplicações que necessitam de alta velocidade, na faixa de GHz e resoluções medias de 8 a 16 bits. [6].

A arquitetura de conversão SAR (registro de aproximação sucessiva) tem resoluções variando de 8 bits a 16 bits e taxas de amostragem variando de 50 KHz a 100 MHz [1]. Nos últimos anos a demanda dos SAR ADC tem sido incrementada pela maior demanda de aplicações com necessidade de baixo consumo, taxa de amostragem moderada e simplicidade, sendo muito utilizada em sistemas biomédicos

[6]. Também, a arquitetura SAR é conhecida por sua estrutura simples, menor consumo de energia e de área de silício [7].

A arquitetura SAR é composta de um bloco SAR que representa a lógica e controle da aproximação sucessiva, de um bloco (DAC) que representa um estágio de conversão digital análogo e de um bloco S/H que representa um circuito de samplehold e um bloco comparador [1].

Os conversores SAR convencionais utilizam redes resistivas ou capacitivas em seu estágio D/A, os tornando bastante suscetíveis a descasamentos, o que limita o desempenho global do ADC, além de não apresentar uma boa linearidade e apresentarem um grande consumo de área. O uso da técnica PWM como DAC baseado no uso de comparadores e contadores digitais melhora essas características, e sendo um circuito totalmente digital, melhora a linearidade e o consumo de área. [1].

A arquitetura de conversão baseada na aproximação sucessiva (SAR) de sinais por modulação de largura de pulso (PWM) tem como característica particular as linearidades [1]. No estágio de conversão digital analógica (DAC), o qual é um bloco determinante na resolução deste conversor analógico digital é de acordo com [6] é considerado o bloco com maior consumo energético, o uso da técnica PWM apresenta vantagens em comparação com os DAC convencionais devido a que melhora a linearidade, diminui a área de silício pelo fato de ser um circuito quase totalmente digital.

No entanto, o tipo de modulador PWM utilizado em [1] que é baseado em um contador e comparadores digitais, necessita de uma frequência de relógio (CLK) muito elevada, o que resulta em um consumo de potência muito alto.

Por este motivo surgiu a ideia de gerar uma estratégia que melhore as características desta arquitetura através de uma técnica DAC PWM, que aumente a resolução do conversor mantendo um consumo baixo de potência. Isto pode ser feito através de uma arquitetura PWM híbrida, dado que esta técnica atinge maiores resoluções com frequência de CLK menores.

A técnica PWM híbrida proposta utiliza a arquitetura baseada em contadores como base, aproveitando a sua linearidade. Além disso, utiliza como estrutura complementar uma rede de atrasos baseada em portas lógicas. Uma vez que a técnica PWM híbrida ainda não tem sido utilizada em circuitos ADC se fez necessário o desenvolvimento de uma metodologia de projeto considerando as variações de processos e descasamento dos elementos da rede de atrasos, que será apresentado neste trabalho.

#### 1.2. Organização do trabalho.

Este trabalho se distribui ao longo de 5 capítulos. Sendo o primeiro introdutório.

No segundo capítulo foi feita uma revisão bibliográfica de conversores ADC, para determinar a técnica de conversão mais adequada para aquisição de sinais biológicos, e as diferentes técnicas de conversão DAC aplicadas como um sub-circuito dos conversores ADC que melhoram seu desempenho.

O terceiro capítulo mostra o funcionamento do sistema proposto, e a metodologia de projeto desenvolvida.

O quarto capítulo apresenta a validação do modelo e dos cálculos propostos na metodologia de projeto através de simulações elétricas e funcionais.

Por fim, o capítulo 5 traz conclusões que foram observadas e sugestões para trabalhos futuros a serem desenvolvidos.

#### 2. Revisão bibliográfica

#### 2.1. Conversor A/D

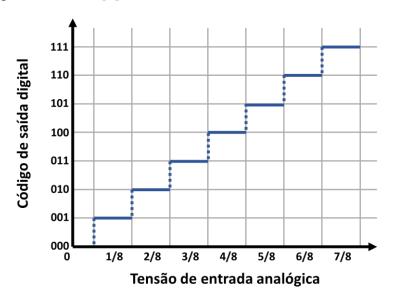

Um conversor analógico para digital, é um circuito eletrônico que converte sinais analógicos contínuos em valores digitais. Um sinal analógico precisa ser quantificado para ser convertido em um digital. Um sinal analógico pode ter valores infinitos; a quantificação consiste na substituição desses valores infinitos em quantidades discretas e finitas de valores. Na Figura (2.1) é mostrado um exemplo de conversão. O sinal de entrada varia entre 0 e FS (escala completa), e é convertido em uma palavra digital de N-bits [8].

Figura (2. 1). Conversão analógico-digital

#### 2.2. Conversor A/D SAR

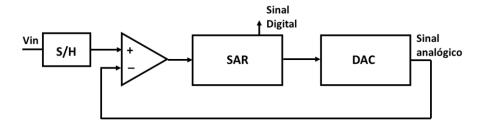

O SAR é feito com blocos básicos, os quais são, um bloco S/H, que mantém o valor da entrada fixo durante a conversão; o DAC que converte um sinal digital composto pelos "bits", que já foram confirmados / comparados, por uma referência analógica, em ciclos anteriores do processo de aproximação sucessiva; "Comparador" que realiza a comparação do sinal de entrada com a referência gerada pelo DAC; e o "Registro" que armazena os "bits" convertidos para serem utilizados pelo DAC e para apresentar o valor digital convertido, como é ilustrado na figura (2.2). O "SAR" precisará de "n+1" ciclos para gerar um sinal de "n" bits e, portando, sua frequência de operação é limitada por "n+1 intervalos" de tempo de conversão para cada bit [9].

Figura (2. 2). Blocos básicos do SAR.

#### 2.3. Conversor A/D SAR PWM

A modulação por largura de pulso (PWM) pode ser empregada na regulação de tensão, onde se consegue o nível desejado de tensão através da variação do ciclo de trabalho do sinal modulado. Foi demonstrado que os controladores digitais para conversores D/A têm muitas vantagens em comparação com as suas homólogas analógicas [10]. Os benefícios do uso dos circuitos DAC PWM incluem alto desempenho, alta capacidade anti-ruído [11], melhoria da eficiência energética e redução da sensibilidade das variações dos componentes [12].

A arquitetura de conversão A/D [1] mostrada na figura (2.3) utiliza a técnica PWM em seu estágio de conversão D/A, o qual minimiza os erros de não linearidade produzidos nos conversores A/D convencionais que usam no estágio de conversão D/A redes resistivas ou capacitivas.

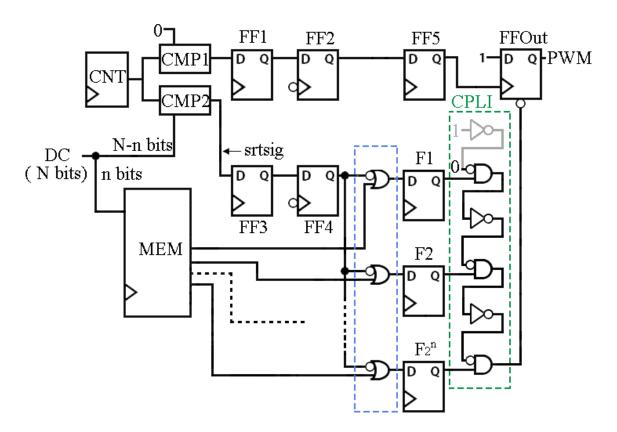

Figura (2. 3). Conversor A/D SAR DAC PWM [1].

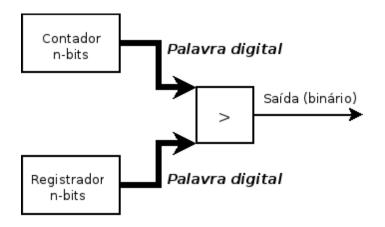

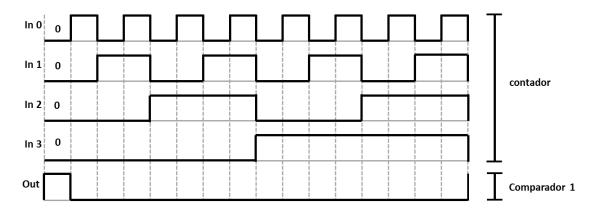

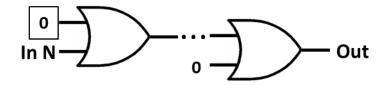

A Figura (2.4) ilustra a lógica utilizada no circuito modulador PWM que é composta de um contador, de um registrador e de um comparador. Enquanto a contagem do contador não alcança o valor presente no registrador, a saída do comparador envia nível lógico alto. Quando a contagem atinge o valor presente no registrador a saída do comparador apresenta nível lógico baixo.

Figura (2. 4). Lógica do circuito modulador PWM [7].

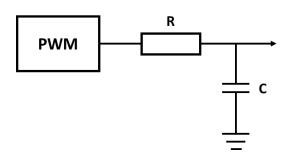

#### 2.3.1. Filtro passa baixa

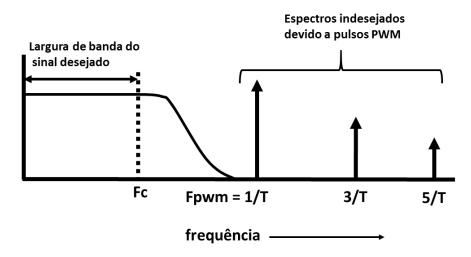

O modulador PWM trabalha em conjunto com um filtro passa baixa a fim de gerar um valor DC na saída do conversor que corresponde ao ciclo de trabalho do sinal PWM. Este filtro tem requerimentos de atenuação dependendo das frequências.

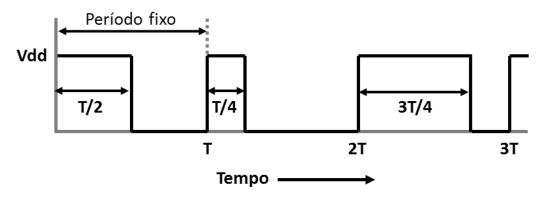

Em um sinal PWM típico, a frequência base é fixa, mas a largura do pulso é uma variável. A largura do pulso é diretamente proporcional à amplitude do sinal original não modulado. Em outras palavras, em um sinal PWM, a frequência da forma de onda é uma constante enquanto o ciclo de trabalho varia (de 0% a 100%) de acordo com a amplitude do sinal original. Um sinal PWM típico é mostrado na Figura (2.5), onde o primeiro, segundo e terceiro período tem a metade um quarto e três quartos do ciclo de trabalho respectivamente.

Figura (2. 5). Forma de onde de um sinal PWM típico.

Uma análise de Fourier de um sinal PWM como o representado na figura (2.5) mostra que há um pico forte para um ciclo de trabalho de T/2, e existem outros harmônicos fortes também. Estes picos são ruídos indesejados e devem ser eliminados. Isso exige que o sinal PWM passe através de um filtro passa baixas, eliminando assim esses componentes de ruído inerentes [13], isto é ilustrado na figura (2.6).

Figura (2. 6). Filtro passa baixas para um sinal PWM.

#### 2.4. Especiações de conversores D/A

Principais parâmetros que definem a qualidade de um conversor.

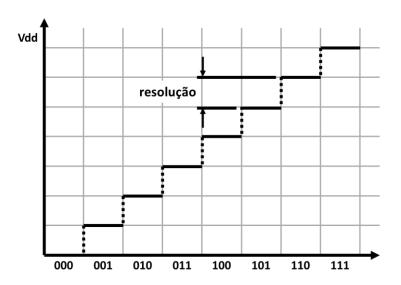

#### 2.4.1. Resolução

A resolução de um conversor depende da quantidade de bits que são utilizados e a precisão que terá o dispositivo para realizar a conversão. Como é ilustrado na figura (2.7) o sinal analógico que ingressa no conversor é dividido numa série de pequenas frações. Maior a resolução significa mais frações. O valor da resolução e dada pela equação (2.1).

Figura (2. 7). Resolução da conversão D/A.

$$resolução = \frac{tensão da fonte}{2^N}$$

(2. 1)

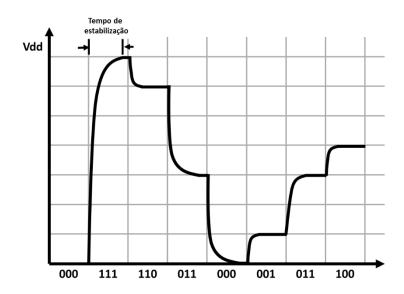

#### 2.4.2. Tempo de estabelecimento

Como ilustra a figura (2.8), o tempo de estabelecimento é o período que leva um conversor D/A para obter o máximo valor de tensão quando a entrada digital passa todos os bits de 0 para todos os bits a 1 ou o contrário. No caso que o sinal digital recebido pelo conversor seja oriundo de um circuito registrador de aproximação sucessiva, o tempo de acomodação será considerado quando o sinal passe de ter todos os códigos em zero até o código com o bit mais significativo em um e o resto em zero ou vice-versa, como mostrado na figura (2.9). Esta parâmetro depende da resolução do conversor ADC, sendo que quanto maior este for, maior é o tempo de estabelecimento do conversor DAC.

Figura (2. 8). Tempo de estabelecimento do conversor A/D.

Figura (2. 9). Tempo de estabelecimento do conversor D/A com entrada SAR.

#### 2.4.3. Erro de linearidade

Em um conversor D/A o ideal é que todos os degraus de tensão sejam iguais ao valor de tensão analógica correspondente. De maneira que o erro de linearidade é a maior diferença que existe entre o valor real e ideal, isto é representado na figura (2.10).

Figura (2. 10). Erro de linearidade em um conversor D/A.

A não linearidade diferencial (DNL) é a medida do quão uniforme são os níveis de quantização da curva de transferência do conversor. Cada nível de quantização é comparado com o nível de quantização ideal e a magnitude da diferença entre eles denota o erro de DNL.

Algumas características importantes do conversor podem ser inferidas a partir de seu DNL. Se o erro de DNL for inferior a 1LSB, o conversor não possuirá códigos perdidos. Se o erro de DNL for inferior a 0,5LSB, o conversor será monotônico [1].

A Equação (2.2) define o erro de DNL para cada nível quantização [1].

$$DNL = 1 - \frac{V(x) - V(x+1)}{LSB}$$

(2. 2)

Onde LSB

$$LSB = \frac{faixa\ de\ escala\ completa}{numero\ de\ bits} \tag{2.3}$$

E V(x) - V(x+1) são dois níveis de quantização adjacentes para o código x [1].

O erro de não linearidade integral (INL) pode ser entendido como a soma dos erros de DNL ao longo da curva de transferência do conversor, uma vez que o erro de DNL ocorre em cada um dos níveis de quantização.

#### 2.4.3. Monoticidade

Essa característica assume que quando ocorrido um aumento na tensão de entrada, o código digital de saída não diminua. Essa característica é crítica em aplicações de controle pois pode resultar em uma operação instável.

#### 2.4.4. Perda de código

Um conversor deve ser capaz de realizar a correspondência para todos os códigos digitais de saída. Se o conversor não é capaz dessa realização, é dito haver códigos perdidos [1].

#### 2.5. Arquitetura PWM linhas de atrasos

Esta arquitetura representada na figura (2.11), utiliza linhas de atraso combinadas com um multiplexador [14]. O sinal de clock ativa o set do flip flop SR iniciando o pulso PWM, e o sinal que reinicializa o flip flop é o próprio sinal de clock com um determinado atraso ( $\Delta t$ ) que determina o incremento no ciclo de trabalho.

Figura (2. 11). Arquitetura PWM linhas de atrasos [14].

Esta arquitetura elimina a necessidade de um clock elevado, reduzindo o consumo de energia. Por outro lado tem um consumo maior de área, necessitando  $2^N$  elementos, no qual, N é o número de bits do conversor. Os atrasos no circuito não são

uniformes devido às  $2^N$  linhas de entrada no multiplexador, o que afeta a linearidade do circuito

#### 2.6. Arquitetura PWM com linha de atraso segmentada

A técnica de Linhas de Atraso Segmentadas [15] foi desenvolvida para diminuir a quantidade de elementos de atraso da arquitetura linhas de atrasos. Ao invés de utilizar um único multiplexador, utilizam-se vários multiplexadores em cascata e cada um deles possui atrasos com pesos diferentes.

Figura (2. 12). Arquitetura PWM linha de atraso segmentada [15].

#### 2.7. Arquitetura PWM híbrida

Uma arquitetura híbrida é a junção de duas arquiteturas com resoluções baixas que dão origem a um circuito de alta resolução. Estas arquiteturas apresentam vantagens em termos de consumo energético e área de chip [11]. A arquitetura PWM híbrida [16] representada na figura (2.13), é baseada em contadores como resolução base para o aproveitamento da boa linearidade desse tipo de estrutura, e como arquitetura complementar uma rede de atrasos, desenvolvida com o objetivo de atingir maior resolução.

Figura (2. 13). Arquitetura PWM híbrida baseada em contadores e linhas de atrasos [16].

#### 2.8. Erro padrão

O erro padrão é uma medida que indica a dispersão dos dados dentro de uma amostra com relação à média [17], no caso de circuitos integrados as dispersões ocorrem durante o processo de fabricação devido à as pequenas variações aleatórias dos dispositivos, exceto para circuitos muito pequenos, é difícil prever de forma analítica o seu comportamento devido à combinação dos erros de incompatibilidade de dispositivos individuais. O impacto dessas variações de parâmetros aleatórios no comportamento do circuito pode ser estudado com a simulação de Monte Carlo analisando um grande conjunto de instâncias de circuito com dispositivos variados aleatoriamente.

#### 2.9. Propagação de incertezas

A propagação de incertezas é definida como os efeitos em uma função pela incerteza de uma variável. Este é um cálculo estatístico derivado do cálculo, projetado para combinar incertezas de múltiplas variáveis, a fim de fornecer uma medida precisa de confiança. Sendo uma ferramenta que cientistas tem usado conveniente e frequentemente em seus trabalhos [18], ela vai ser considerada na metodologia de projeto proposta a fim de garantir que as incertezas dos componentes não prejudiquem o funcionamento e a linearidade do conversor A/D.

#### 3. Arquitetura proposta

Este capítulo propõe o projeto de uma arquitetura de conversão A/D, utilizando a técnica SAR. Esta arquitetura necessita de uma etapa de conversão D/A, o que é determinante na resolução do conversor A/D, dessa maneira, se torna importante utilizar uma técnica que permita atingir altas resoluções e ainda manten um consumo de energia baixo.

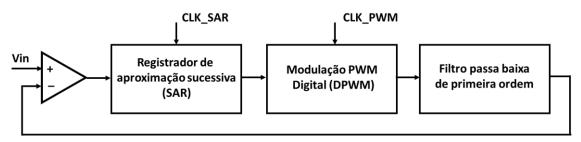

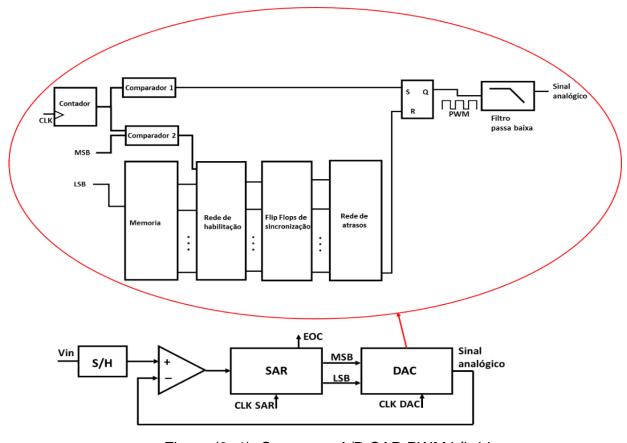

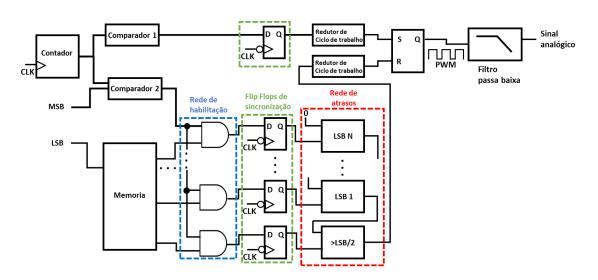

O uso da técnica PWM no estágio de conversão D/A traz melhoras no desempenho do conversor em termos de linearidade, o que influencia diretamente na resolução efetiva, e também reduz a área de silício necessária, uma vez que o circuito proposto é quase completamente digital. Não obstante, para este tipo de arquitetura a resolução está limitada pelo ciclo de relógio. A partir dessa premissa, surgiu a ideia do uso de uma técnica PWM híbrida [16], a qual aproveita as vantagens da técnica PWM já descrita, e ainda consegue resoluções maiores com o mesmo consumo de relógio. A figura (3.1) representa em diagrama de blocos a arquitetura de conversão A/D com o uso da técnica PWM híbrida no estágio de conversão D/A.

Figura (3. 1). Conversor A/D SAR PWM híbrido.

#### 3.1. Arquitetura de conversão A/D SAR

A Figura (3.1) ilustra o diagrama de blocos da conversão por aproximação sucessiva. Essa arquitetura é composta de um bloco SAR que representa a lógica e controle da aproximação sucessiva, de um bloco DAC que representa um estágio de conversão digital analógico e de um bloco S/H que representa um circuito de samplehold. O diagrama também ilustra um circuito comparador que possui sua entrada positiva acoplada ao circuito de sample-hold e sua entrada negativa realimentada com o sinal oriundo do estágio DAC. O processo de conversão por aproximação sucessiva consiste em, iniciando-se pelo bit mais significativo, testar um a um os bits da palavra digital aplicada ao conversor digital-analógico (D/A). Esses testes iniciam-se sempre com o valor do bit em avaliação em nível lógico alto, e a cada passo do procedimento de conversão, o valor da saída do conversor D/A é comparado com o valor do sinal analógico de entrada. Se o valor de saída do conversor D/A for maior que o valor do sinal de entrada, o bit em teste recebe o valor lógico baixo e o procedimento tem continuidade aplicando-se um nível lógico no próximo bit que será avaliado. Se o valor do sinal de entrada for maior, o bit em teste continua em nível lógico alto. Esse procedimento ocorre até que o ultimo bit da palavra digital seja testado e seu valor lógico seja corretamente determinado [1].

#### 3.2. Técnica PWM híbrida

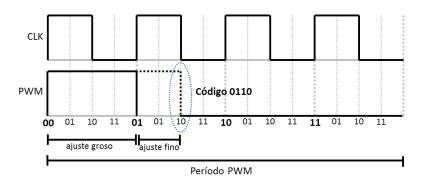

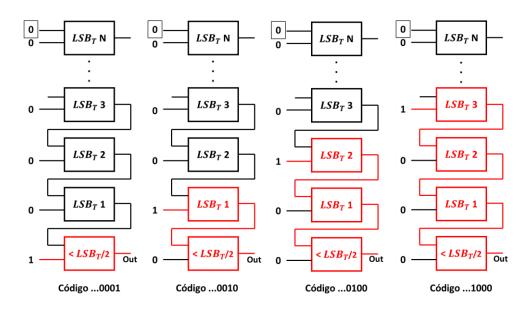

Na técnica PWM híbrida proposta, o ajuste grosso do sinal PWM é realizado por um circuito digital composto por um contador e um comparador. O ajuste fino do sinal PWM é realizado através de uma rede de atrasos, composta de portas lógicas conectadas entre si.

A resolução do sinal PWM determina o passo no incremento no ciclo de trabalho, e é dada por (N + n) bits, onde N representa a resolução do ajuste grosso composto pelos bits mais significativos, e n a resolução do ajuste fino dado pelos bits menos significativos.

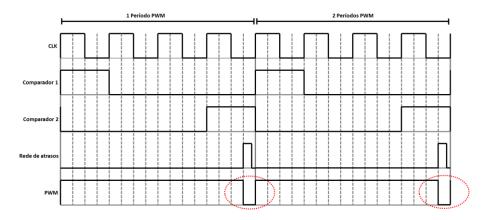

Cada incremento de um bit no ajuste grosso corresponde a um ciclo completo de relógio, e o incremento de um bit de ajuste fino corresponde a um ciclo completo de relógio dividido por n. Como é mostrado na figura (3.2), a qual utiliza como exemplo um circuito PWM híbrido onde o ajuste grosso tem dois incrementos, correspondente ao código 01, e o ajuste fino um incremento correspondente ao código 10, com um código gerado de 0110.

Figura (3. 2). Formas das ondas do sinal PWM.

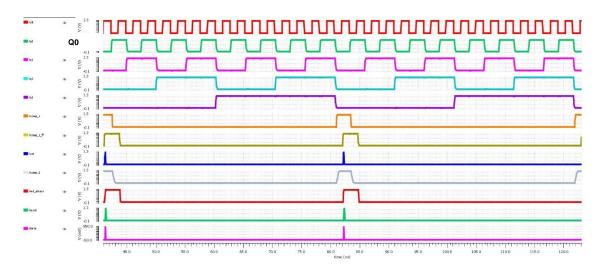

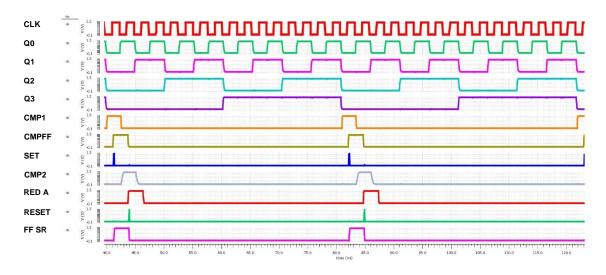

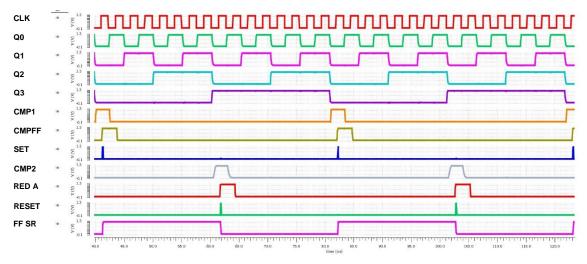

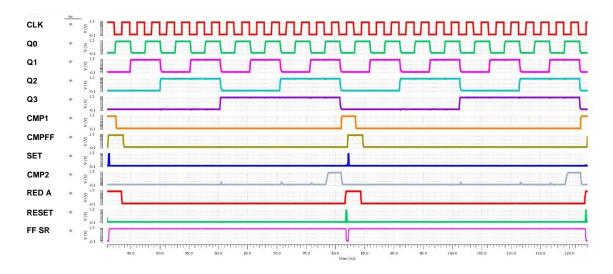

Como é mostrado na figura (3.3), para a definição do ciclo ativo do sinal PWM o comparador 1 gera um pulso na saída quando a contagem do contador está no valor zero, esse pulso ativa o flip flop SR e com a finalidade de estabelecer a duração do ciclo ativo do sinal PWM.

Figura (3. 3). Comportamento dos sinais dos blocos contador e comparador 1.

O comparador 2 recebe os sinais do contador e os sinais provenientes do SAR correspondentes aos bits mais significativos, e gera um pulso em nível lógico alto quando ambas sequências de códigos coincidem. Cada comparação representa um incremento do ciclo de trabalho do sinal PWM equivalente a um ciclo de relógio, como ilustrado na figura (3.4).

Figura (3. 4). Comportamento dos sinais no bloco comparador MSB.

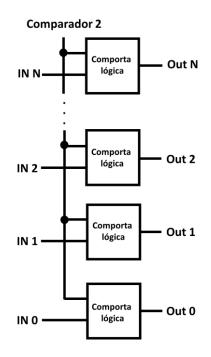

Uma vez que o comparador 2 definiu o incremento no ajuste grosso, o bloco chamado rede de habilitação mostrado na figura (3.5) disponibiliza na sua saída a sequência de códigos gerados pela memória representados na tabela (3.1), cujo endereço é selecionado pelos menos significativos provenientes do registrador de aproximação sucessiva, como ilustrado na figura (3.6).

Figura (3. 5). Rede de habilitação

Tabela (3. 1) Sequência da memória de acordo com o código de entrada.

| Valor   | Código binário | Conteúdo da memória: |

|---------|----------------|----------------------|

| Decimal | [0:3]          | 16 dígitos           |

| 0       | 0000           | 10000000             |

| 1       | 0001           | 01000000             |

| 2       | 0010           | 00100000             |

| :       | :              | ·                    |

| 13      | 1101           | 00000100             |

| 14      | 1110           | 00000010             |

| 15      | 1111           | 00000001             |

Figura (3. 6). Comportamento dos sinais ao longo do tempo na rede de habilitação.

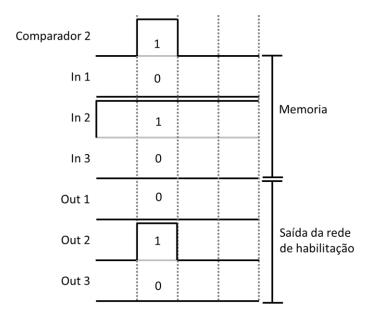

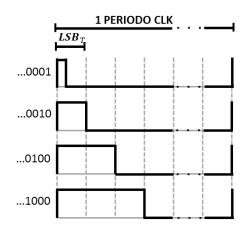

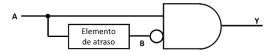

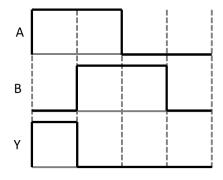

Para a definição do ajuste fino, a sequência de códigos oriunda da rede de habilitação é conectada na rede de atrasos, a qual é composta por elementos formados por implementações de portas lógicas conectadas entre si com atrasos de propagação equivalentes a um  $LSB_T$  (bit menos significativo baseado no tempo), onde cada código da sequência representa uma posição do único pulso em nível lógico alto na rede de atrasos, controlando desta maneira o tempo em que esse único pulso em nível lógico alto vai demorar em se propagar através dela. Para melhor compreensão o percorrido pelo único sinal em nível lógico alto é ilustrado na figura (3.7), esse sinal

é conectado na entrada RESET do flip flop D, interrompendo o ciclo ativo do sinal PWM.

Nota-se que o elemento mais próximo na saída da rede de atrasos tem um peso em termos de tempo menor do que meio  $LSB_T$ . Isto ocorre porque a sequência de código com o bit de menor peso em nível lógico alto (...0001) deve representar zero atrasos.

Figura (3. 7). Funcionamento da rede de atrasos.

A figura (3.8) representa o incremento de ajuste fino no ciclo de trabalho do sinal PWM segundo o código de entrada.

Figura (3. 8). Incremento de ajuste fino no ciclo de trabalho do sinal PWM baseado na sequência de entrada da rede de atrasos.

### 4. Metodologia proposta

Neste capítulo é proposta uma metodologia de projeto para o conversor ADC DAC PWM híbrido, que considera as variações de processos e descasamentos dos elementos que compõem a rede de atrasos.

#### 4.1. Resolução da rede de atrasos

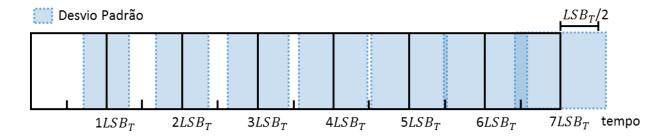

No caso de um circuito onde seja exigida uma alta precisão, os possíveis descasamentos e variações de processos são parâmetros que devem ser considerados e analisados. Na rede de atrasos é feita uma avaliação do erro de propagação a partir das tolerâncias dos componentes que formam os elementos de atraso. Para a verificação das possíveis tolerâncias nesses elementos, ou seja, o desvio padrão, é utilizado o método estatístico Monte Carlo, proporcionado pelo software elétrico CADENCE.

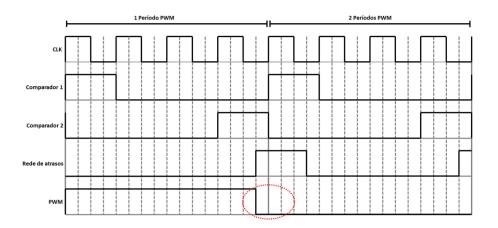

A figura (4.1) ilustra o aumento do atraso e seu desvio padrão com o incremento de portas conectadas. Se o erro de propagação for maior do que meio LSB em termo de tempo ( $LSB_T$ ) ocorre uma sobreposição de código.

Figura (4. 1). Erro de propagação na rede de atrasos.

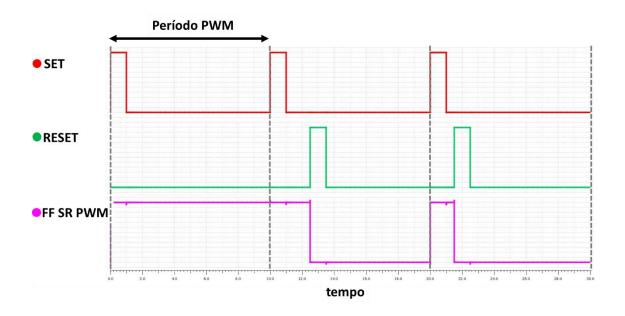

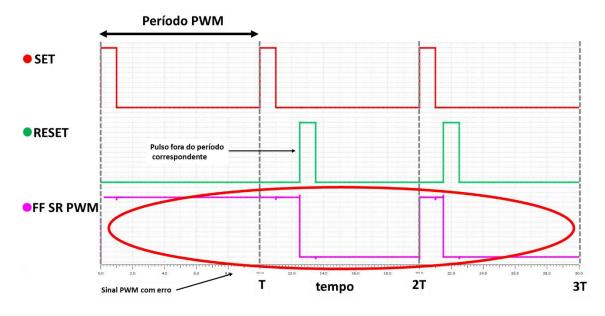

A figura (4.2) mostra o erro provocado quando o valor do elemento de atraso aumenta até gerar o pulso em nível lógico alto fora do período correspondente, gerando um ciclo de trabalho com um valor completamente distante ao projetado, como é exemplificado na figura (4.3).

Figura (4. 2). Saída do flip flop SR gerador do sinal PWM com erro.

Figura (4. 3). Saída do flip flop SR gerador do sinal PWM.

Assim, se faz necessário delimitar uma resolução máxima onde o erro de propagação não prejudique o funcionamento do sistema e permita a operação segura do conversor A/D.

#### 4.2. Cálculo da propagação de erros e incertezas da rede de atrasos

Para encontrar o erro de propagação de uma função w = ax, ou seja valor de  $\sigma_w$ , é usada a equação de incerteza (4.1), definida pelo produto de uma grandeza experimental por uma constante a.

$$\left|\frac{\sigma_w}{w}\right| = \left|\frac{\sigma_x}{x}\right| \tag{4.1}$$

A incerteza do produto por uma constante é simplesmente o produto da constante pela incerteza inicial:  $\sigma_w = |a|\sigma_x$ .

O tempo total da rede de atrasos é representado pela equação (4.2).

$$a_T = \delta_{E_a} P_{\mathsf{t}} \tag{4.2}$$

Em que:

$$\delta_{E_a} = \delta_a P_E \tag{4.3}$$

$\delta_{E_a} = o \ valor \ gerado \ pelo \ elemento \ de \ atraso$

$\delta_a = o \ valor \ gerado \ pelo \ atraso \ da \ porta \ l\u00e9gica$

$P_E$  = quantidade de portas nos elementos de atrasos

$P_t = n$ úmeros de portas necessárias para serem colocadas em série

O número de portas necessárias na rede de atrasos é representado na equação (4.4).

$$P_{t} = (2^{n} - 1) \tag{4.4}$$

Substituindo a equação (4.4) na equação (4.2):

$$a_T = \delta_{E_a}(2^n - 1) \tag{4.5}$$

Para encontrar o erro de propagação da rede de atrasos, mostrado na equação (4.5), é usada a equação (4.1), onde  $\delta_{E_a}$ é uma grandeza experimental, como mostrado na equação (4.6).

$$\left|\frac{\sigma_{a_T}}{a_T}\right| = \left|\frac{\sigma_{\delta_{E_a}}}{\delta_{E_a}}\right| \tag{4.6}$$

Substituindo a equação (4.5) na equação (4.6):

$$\left| \frac{\sigma_{a_T}}{\delta_{E_a}(2^n - 1)} \right| = \left| \frac{\sigma_{\delta_{E_a}}}{\delta_{E_a}} \right| \tag{4.7}$$

O valor de  $\sigma_{a_T}$  da equação (4.7) é isolado para obter a equação baseada na propagação de erro da rede de atrasos (4.8).

$$\sigma_{a_T} = |(2^n - 1)| \ \sigma_{\delta_{E_a}}$$

(4.8)

#### 4.3. Resolução máxima da rede de atrasos

O projeto da rede de atrasos deve respeitar os critérios relacionados à resolução do conversor e ao espalhamento do atraso projetado. Sabe-se que o erro de propagação da cadeia de atrasos tem que ser menor ou igual à metade de um elemento de atraso, a fim de evitar sobreposição e perda de código, conforme mostrado na equação (4.9).

$$\sigma_{a_T} \le \frac{\delta_{E_a}}{2} \tag{4.9}$$

Substituíndo a equação (4.9) na equação (4.7):

$$\frac{\delta_{E_a}}{2} \le \left| \frac{\sigma_{\delta_{E_a}}}{\delta_{E_a}} \delta_{E_a} (2^n - 1) \right| \tag{4.10}$$

Para determinar a resolução máxima permitida é isolado o valor de n.

$$n \le \frac{\log\left(\frac{\delta_{E_a}}{2\sigma_{\delta_{E_a}}} + 1\right)}{\log(2)} \tag{4.11}$$

Dessa maneira existe uma resolução restrita que permite a operação segura do conversor analógico digital.

#### 4.4. Resolução DAC PWM

A resolução total do sinal PWM (Nt) é determinada pela somatória da resolução do ajuste fino (n), correspondente aos bits menos significativos e a resolução de ajuste grossa (N) correspondente aos bits mais significativos [16], conforme mostrado em (4.12).

$$Nt = n + N \tag{4.12}$$

Em que:

Nt = resolução do DAC PMW

N = resolução do ajuste grosso

#### 4.5. Número de portas nos elementos de atrasos

Uma vez definida a resolução de ajuste fino máxima permitida é determinado o  $LSB_t$ , representado na equação (4.13), com a finalidade de achar o número de implementação de portas lógicas necessário que deve compor a cada elemento de atraso, dado pela equação (4.14). Isto fica restrito a frequência de relógio ( $f_{CLK}$ ) disponível. Quando maior a frequência de relógio menor e o número de portas necessárias, isto é dado pela equação (4.15).

$$LSB_t = \frac{1}{2^n f_{CLK}} \tag{4.13}$$

$$N_p = \frac{LSB_t}{\delta_{E_a}} \tag{4.14}$$

$$N_p = \frac{1}{2^n f_{CLK} \delta_{E_a}}$$

(4. 15)

#### 4.6. Frequência PWM

Sendo o incremento do ajuste grosso uma contagem do relógio, a frequência PWM é dada pela frequência do contador dividida entre a resolução dos bits mais significativos, conforme (4.16):

$$f_{PWM} = \frac{f_{CLK}}{2^{Nt}} \tag{4.16}$$

#### 4.7. Frequência SAR

O circuito DAC PWM trabalha em conjunto com o filtro passa baixa a fim de obter na saída um sinal analógico.

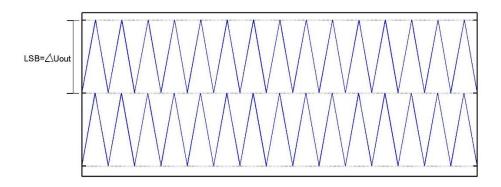

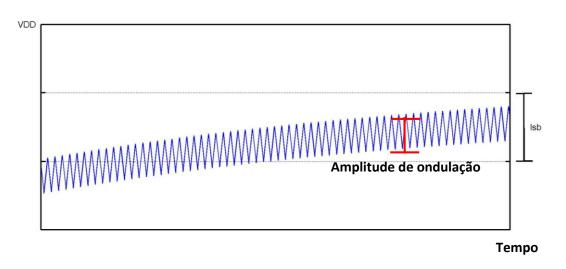

O filtro passa baixa deve filtrar o sinal PWM com uma ondulação de amplitude que não seja maior do que o valor de tensão e a resolução do sinal de PWM, ou seja um LSB em termos de tensão. Isto é ilustrado na figura (4.4).

Figura (4. 4). Amplitude da ondulação.

Assim conforme [7] a equação (4.17) representa a atenuação mínima necessária para satisfazer essa condição.

$$A_{dB} \ge 20 \log \left(\frac{\pi}{2^N + 1}\right) \tag{4.17}$$

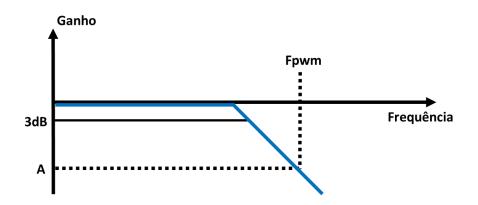

É possível obter as características dos filtros passa baixas para atingir a atenuação com a frequência requerida a partir da sua função de transferência no diagrama de bode, representado na figura (4.5).

Figura (4. 5). Diagrama de bode em função da frequência e a atenuação.

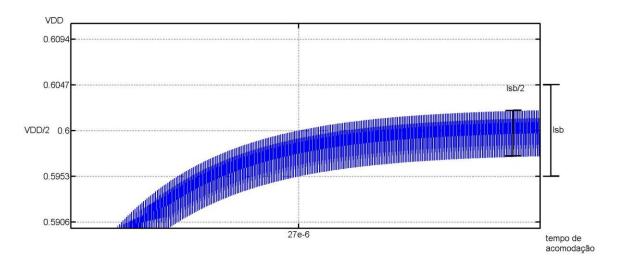

A frequência SAR dada pela equação (4.18) deve ser menor, ou no pior caso, igual ao tempo que demora o filtro passa baixa em responder, ou seja, que já tenha acomodado o sinal dentro da faixa de tensão correspondente, como é ilustrado na figura (4.6).

Figura (4. 6). Acomodação do sinal PWM dentro da faixa de tensão correspondente.

$$f_{SAR} \le \frac{1}{t} \tag{4.18}$$

## 4.8. Taxa de amostragem

De acordo com [7], para o conversor realizar uma nova amostragem, todos os bits do SAR devem estar determinados, isto ocorre quando depois de Nt + 1 períodos de relógio SAR, o que é representado na equação (4.19).

$$f_s \ge \frac{f_{sar}}{Nt + 1} \tag{4.19}$$

## 4.9. Diagrama de fluxo da metodologia de projeto proposta

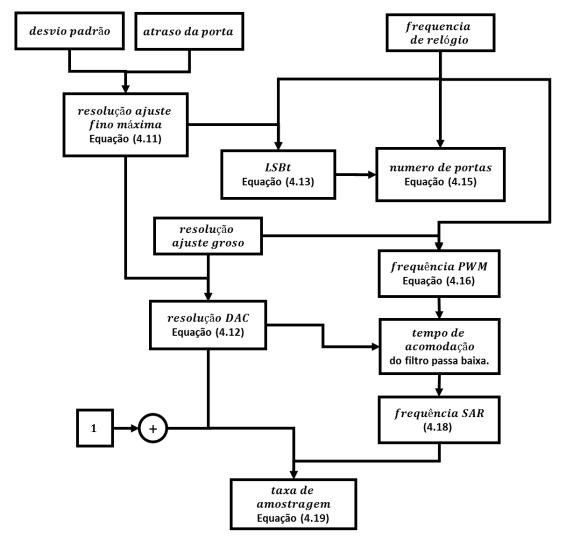

O diagrama de blocos (4.1) representa graficamente a metodologia proposta para a realização dos cálculos que envolvem o conversor ADC SAR PWM híbrido mediante um modelo matemático.

Diagrama (4. 1 ) Representação gráfica da metodologia de projeto proposta.

## 5. Resultados

## 5.1. Validação da metodologia de projeto proposta.

Para a validação do equacionamento proposto na metodologia foi projetado um circuito conversor A/D de 7 bits, no software elétrico CADENCE, processo CMOS IBM130, biblioteca cmrf8sf. O conversor tem uma resolução grosa é de 4 bits a resolução fina de 3 bits, que é a máxima resolução que permite a tecnologia, com uma tensão de alimentação de 1.2V e com portas lógicas com atrasos de 59.5ps em um ciclo de relógio para o conversor ADC de 210 Mhz.

Por meio de simulação funcional usando a ferramenta simulink do software Matlab foi modelada a rede de atrasos com erro de propagação, a fim de comprovar o equacionamento proposto de máxima resolução na rede de atrasos (4.11).

$$n \le \frac{\log\left(\frac{\delta_{E_a}}{2\sigma_{\delta_{E_a}}} + 1\right)}{\log(2)} \tag{4.11}$$

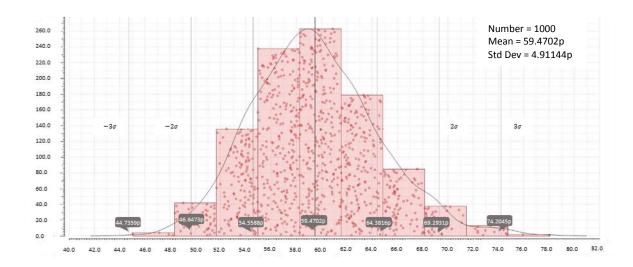

Os elementos de atrasos são formados por implementações de portas lógicas OR a fim de que o único pulso em nível lógico alto proveniente da memória se propague através da rede. Para obter o erro padrão dos mesmos é utilizado a análise estatístico de Monte Carlo proporcionado pelo software CADENCE, com uma quantidade de 1000 rodadas, valor estabelecido pois com o aumento do número de rodadas o valor entregado pelo software de erro padrão não apresentava diferenças significativas, foram obtidos os seguintes valores para a borda de decida da porta lógica OR: 59.47  $\pm$  4.9 figura (5.1). De acordo com [19], em física e engenharia é comum adotar um desvio padrão para o intervalo de confiança.

Figura (5. 1). Rede de atrasos sem erro de propagação.

Independentemente do número de portas lógicas que compõem o elemento de atraso, a proporção do erro padrão será a mesma e por isso se terá o mesmo resultado com base na resolução máxima permitida na rede de atrasos, isto é devido a que, o aumento do erro padrão do elemento de atraso é diretamente proporcional ao aumento do erro de propagação da rede de atrasos. Neste caso é analisado o erro padrão do elemento de atraso com uma porta lógica só. Substituindo esses valores na equação (4.11), é obtido um valor de n = 2.8, o qual é arredondado para 3, um número inteiro, e um valor de resolução válido mais próximo.

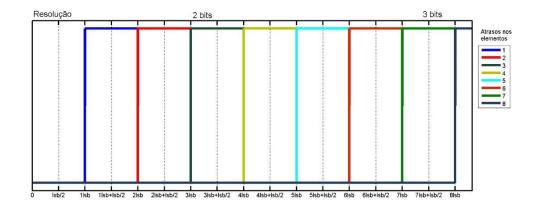

A figura (5.2), representa o comportamento ideal da rede de atrasos, ou seja, sem erro padrão, obtido através da simulação funcional no software simulink, onde cada pulso representa o aumento dos atrasos.

Figura (5. 2). Rede de atrasos sem erro de propagação.

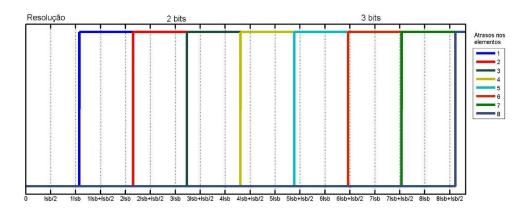

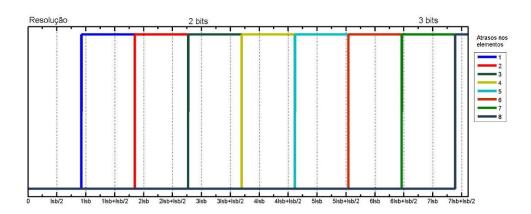

Através dos valores anteriores de erro padrão, são obtidas as figuras (5.3 e 5.4), onde cada pulso representa um atraso com um desvio padrão as quais mostram o comportamento da cadeia de atrasos com erro de propagação, simulando como o erro padrão pode aumentar ou diminuir o valor de atraso do pulso projetado, onde é possível perceber que, para 3 bits de resolução da cadeia de atrasos tem uma sobreposição de código somente de 6%, coincidindo com o resultado obtido através do equacionamento (4.10).

Figura (5. 3). Rede de atrasos com erro de propagação com aumento do valor de atraso do pulso de um erro padrão.

Figura (5. 4). Rede de atrasos com erro de propagação com diminuição do valor de atraso do pulso de um erro padrão.

Para o cálculo da resolução DAC PWM híbrido, o qual foi implementado com uma resolução no ajuste grosso e fino 4 e 3 bits respectivamente, é utilizada a equação (4.12).

$$N_T = n + N$$

$$N_T = 3 + 4$$

$$N_T = 7$$

(4. 12)

Para a realização do cálculo do número de portas necessárias para formar um elemento de atraso é usada a equação (4.15).

$$N_{p} = \frac{1}{2^{n} f_{CLK} \delta_{E_{a}}}$$

$$N_{p} = \frac{1}{2^{n} 210Mhz 59.5ps}$$

$$N_{p} = 10$$

(4. 15)

A frequência DAC PWM híbrido pode ser obtida através da equação (4.16).

$$f_{PWM} = \frac{f_{CLK}}{2^{Nt}}$$

$$f_{PWM} = \frac{210Mhz}{2^4}$$

$$f_{PWM} = 13Mhz$$

$$(4. 16)$$

A frequência do SAR depende do tempo de resposta do filtro passa baixa que for implementado, por outro lado este filtro deve considerar a atenuação necessária para uma determinada resolução, de maneira que o filtro consiga atenuar o sinal para que a amplitude da mesma seja menor que a amplitude dos degraus do conversor, e frequência do sinal PWM. Por esta razão foi desenvolvido um equacionamento que considere esses parâmetros usando como filtro passa baixa um circuito resistivo capacitivo simples, (filtro RC) ilustrado na figura (5.5) e baseando-se nas suas características elétricas.

## Figura (5. 5). Circuito RC.

Em um circuito RC a corrente que flui através da resistência é a mesma que flui através do capacitor.

$$I_C = I_R \tag{5.1}$$

A lei de Ohm pode expressar que a corrente é diretamente proporcional à tensão e inversamente proporcional à resistência. Escrito como uma expressão matemática, a lei de Ohm é:

$$Ic = \frac{V}{R} \tag{5.2}$$

Para a análise deste sistema é avaliado o um ciclo de trabalho de 50%, que de acordo com [1], é o pior caso. Este ciclo de trabalho representa que o valor de tensão total ao longo do tempo é V / 2. Resultando na equação (5.3).

$$Ic = \frac{Vcc}{2R} \tag{5.3}$$

A corrente em um capacitor é, por definição, o produto da sua capacitância pela mudança de voltagem com respeito ao tempo através dos seus terminais. Como mostra a equação (5.4).

$$Ic = C \frac{\Delta v}{\Delta t} \tag{5.4}$$

Devido á o analise ser feita para um ciclo de trabalho no qual o período em ciclo ativo do sinal vai ser a metade, tem-se a seguinte equação.

$$\Delta t = \frac{T}{2} \tag{5.5}$$

É considerado  $\Delta v$  como a carga do capacitor, que é igual a amplitude no ripo do sinal de saída do filtro representado pela variável  $\Delta UOut$ , como é expressado na equação (5.6).

$$\Delta v = \Delta U O u t \tag{5.6}$$

Fazendo a substituição é obtida a relação entre equação (5.4) e a equação (5.5), como mostra a equação (5.7).

$$C \Delta UOut = Ic \frac{T}{2} \tag{5.7}$$

Foi obtida a equação (5.8) a partir de substituição da equação (5.5) em (5.7).

$$\Delta UOut = \frac{Vcc T}{4RC} \tag{5.8}$$

A amplitude da ondulação (ΔU0ut ) deve ser inferior ou igual ao valor de tensão entre a resolução do sinal de PWM, ou seja um LSB.

$$\Delta UOut \ge \frac{Vcc}{2^{Nt}} \tag{5.9}$$

Substituindo (4.24) em (4.23) é obtida a equação (4.25)

$$\frac{Vcc}{2^{Nt}} \ge \frac{Vcc T}{4RC} \tag{5.10}$$

Isolando a variável RC obtém-se a expressão da constante de tempo  $\tau$ .

$$\tau = RC \ge \frac{2^{Nt}T}{4} \tag{5.11}$$

É possível diminuir a amplitude do ripple aumentando o valor que expressa a quantidade de bits que define a resolução do conversor, isto é por que maior resolução representa maiores níveis de quantização com menores valores de amplitude. Isso é representando na seguinte equação, sendo a o aumento em bits.

$$\tau = RC \ge \frac{2^{Nt+a}T}{4} \tag{5.12}$$

A tabela (5.1) representa as variações na amplitude da ondulação do sinal de saída do filtro segundo o valor de a.

Tabela (5. 1). Amplitude da ondulação de acordo com a variável a.

| а   | Tamanho   | da |

|-----|-----------|----|

|     | ondulação |    |

| 0.5 | 3/4LSB    |    |

| 1   | LSB/2     |    |

| 2   | LSB/4     |    |

| 3   | LSB/8     |    |

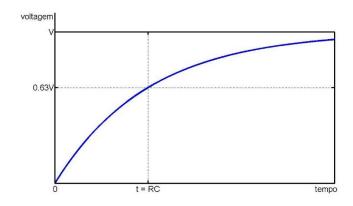

O sinal de um sistema de primeira ordem terá uma acomodação progressiva, com relação à constante de tempo. O tempo de acomodação depende diretamente do tempo de carga de um capacitor através de um resistor, o que pode ser analisado através de um sistema de segunda ordem alimentado com sinal degrau. Por meio da equação (5.13).

$$y(t) = k - e^{-t/\tau}$$

(5. 13)

Utilizando a equação (5.13) é possível mostrar que a voltagem através do capacitor aumenta exponencialmente com o tempo. Onde e tem um valor aproximado de 2.718 (número irracional e é a base do sistema de logaritmos naturais). Alcançando um 63% da sua voltagem máxima V em uma constante de tempo. Isto é apresentado na figura (5.13).

Figura (4. 7). Voltagem de um capacitor em relação ao tempo.

De acordo com a equação (5.13) teoricamente tomaria um tempo infinito para que o capacitor carregasse totalmente. Por isso, é conveniente definir o tempo necessário de estabilização para cada sistema de acordo com os requerimentos da aplicação. Devido ao sinal de entrada PWM deste sistema requerer uma grande precisão, uma maneira de estabelecer o tempo de estabilização do sinal de saída de um filtro RC, é através da resolução, a fim de calcular y(t), que representa o percentual mínimo de acomodação.

O percentual mínimo de acomodação representa a tensão do capacitor carregando-se em um circuito RC, e a resolução do sinal de PWM representa os possíveis níveis de tensão de saída de um filtro. Assim, o sinal deve ser estabilizado dentro de cada um dos níveis correspondentes. Devido ao sinal para um filtro não ideal ter uma amplitude intrínseca, é necessário calcular o percentual de estabilização considerando o tamanho da ondulação, através da variável a. Sendo  $lsb_a$  o bits menos significativo em base no total de acomodação. A seguinte equação (5.14), representa a diferença em LSB permitida na qual o sinal pode se acomodar.

$$y(t) = 1 - lsb_a \frac{2^{a} - 1}{2^{a}}$$

(5. 14)

Em que:

$$lsb_a = \frac{1}{2^{Nt}}$$

(5. 15)

Substituindo na equação (5.14) tem-se a equação do percentual de acomodação em base na amplitude do ripple (5.16) e a resolução.

$$y(t) = 1 - \frac{2^{a} - 1}{2^{Nt + a}}$$

(5. 16)

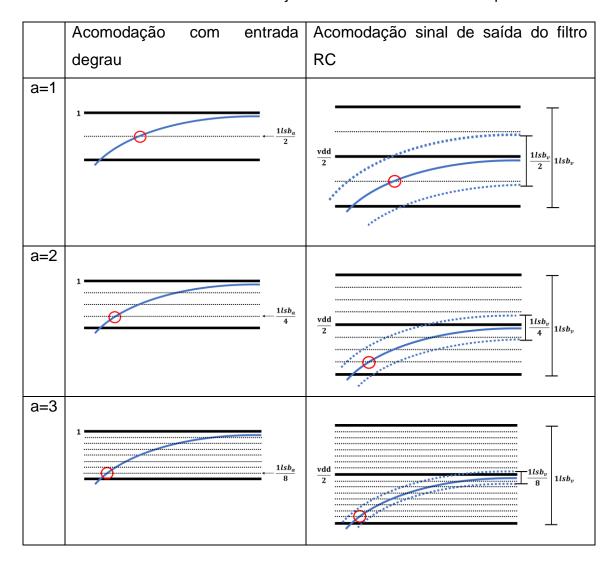

A tabela (5.2) representa os diferentes níveis de acomodação necessários de acordo com o ripo do sinal para vários valores de a. É possível verificar que quanto menor é a amplitude do ripple do sinal menor é o percentual de acomodação necessário para o sinal entrar dentro da faixa de tensão correspondente, por que o nível de estabilização necessário é inferior. Nas figuras da tabela (4.1) a simbologia  $lsb_v$  representa os bits menos significativos em tensão.

c Percentual de acomodação do sinal considerando o ripo.

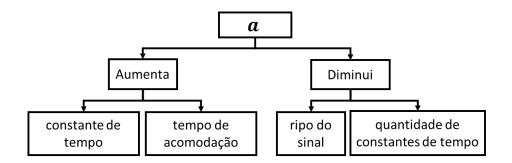

O diagrama de blocos (5.1) representa o comportamento do sinal de saída do filtro, em termos de ondulação e tempo de acomodação quando o valor da variável a aumenta.

Diagrama (5. 1). Comportamentos do sinal PWM de acordo com a variável a.

Uma vez definida a equação para achar o valor y(t), é isolado t com a finalidade de obter a equação que represente o tempo necessário para a estabilização do sinal:

$$t = -\tau \ln(K - y(t))$$

(5. 17)

Através da equação (5.18) é possível calcular as quantidades de constantes de tempo necessárias, sendo  $\tau_n$  número de constantes de tempo.

$$\tau_n = \frac{t}{\tau} \tag{5.18}$$

Substituindo os valores já determinados na equação (5.11) a fim de calcular a constante de tempo do filtro RC.

$$\tau = RC \ge \frac{2^{Nt+\alpha}T}{4}$$

$$\tau = RC \ge \frac{2^{7+1}62ns}{4}$$

$$\tau = RC \ge 4.8\mu s$$

(5. 11)

Para o cálculo do percentual mínimo de acomodação é usado o equacionamento (5.16).

$$y(t) = 1 - \frac{2^{a} - 1}{2^{Nt + a}}$$

$$y(t) = 1 - \frac{2^{1} - 1}{2^{7+1}}$$

$$y(t) = 0.9961$$

(5. 16)

Tempo de acomodação do sinal de saída do filtro RC, equação (5.17).

$$t = -\tau \ln(K - y(t))$$

$$t = 4.8\mu s \ln(1 - 0.961)$$

$$t = 27e - 06$$

(5. 17)

Utilizando a equação (5.18) é possível calcular as quantidades de constantes de tempo necessárias.

$$\tau_n = \frac{t}{\tau}$$

$$\tau_n = \frac{22e - 06}{4\mu s}$$

$$\tau_n = 5.5452$$

(5.18)

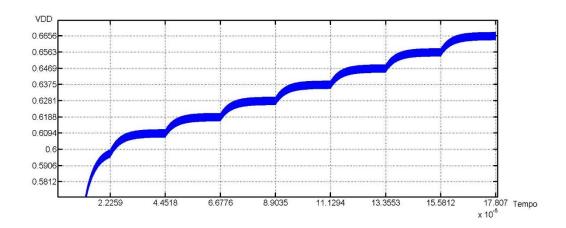

A figura (5.4) ilustra o resultado obtido com os valores usados no equacionamento anterior através de simulação funcional, o qual mostra o comportamento do sinal de saída do filtro RC. Com um valor de a=1 tem-se uma amplitude de ripo de meio LSB para o pior caso do ciclo de trabalho, e o sinal entra na faixa de tensão em um tempo de  $22\mu s$ .

Figura (5. 6). Tempo de acomodação no sinal de saída do filtro RC.

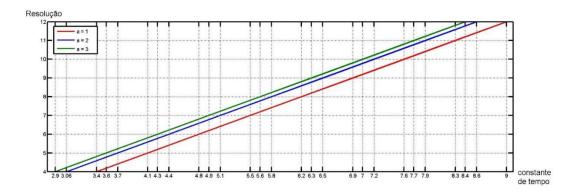

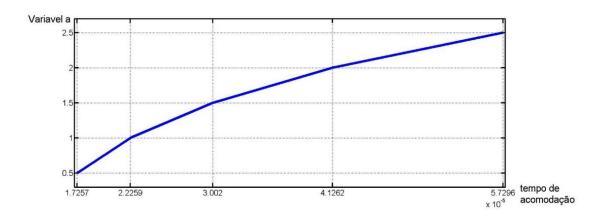

As figuras (5.7) e (5.8) mostram o comportamento do sinal de saída do filtro em termos de acomodação e resolução. A figura (5.7) mostra que quanto maior a resolução do sinal maior é o tempo necessário para o sinal ter-se acomodado na faixa de tensão correspondente. Por outro lado, a figura (5.8). Ilustra que quanto menor o valor da variável a menor é o tempo necessário de acomodação, devido a que o sinal terá menor amplitude e entrara na faixa de tensão correspondente em um tempo menor.

. No entanto valor mínimo do a está amarrado nos valores possíveis de implementação dos componentes do filtro RC.

Figura (5. 7).constantes de tempo necessárias para as diferentes resoluções a valores da variável *a*.

Figura (5. 8). Tempo de acomodação do sinal para diferentes valores da variável a.

Já tendo sido calculado o tempo de resposta do filtro RC, e determinada a frequência do SAR por meio da equação (4.18).

$$f_{SAR} \le \frac{1}{t}$$

$$f_{SAR} \le \frac{1}{27\mu}$$

$$f_{SAR} \le 37Mhz$$

$$(4.20)$$

A frequência de amostragem do circuito A/D é determinada por meio da equação (4.19).

$$f_{s} \ge \frac{f_{sar}}{Nt+1}$$

$$f_{s} \ge \frac{f_{sar}}{Nt+1}$$

$$f_{s} \ge \frac{37Mhz}{8+1}$$

$$f_{s} \ge 4Mhz$$

$$(4. 19)$$

As tabelas (5.2) até (5.11) representam um resumo dos cálculos feitos previamente neste capítulo.

Tabela (5. 2). Calculo da Resolução máxima da rede de atrasos.

| Resolução máxima da rede de atrasos                                                                      |      |                      |

|----------------------------------------------------------------------------------------------------------|------|----------------------|

| Equação                                                                                                  |      | Número da<br>equação |

| $n \le \frac{\log\left(\frac{\delta_{E_a}}{2\sigma_{\delta_{E_a}}} + \log(2)\right)}{\log(2)}$           | + 1) | (4.14)               |

| Dados                                                                                                    |      |                      |

| $\delta_{E_{\alpha}}$ 59.47 ps                                                                           |      | 9.47 ps              |

| $egin{array}{c c} \delta_{E_a} & 59.47 \  ho s \ \hline \sigma_{\delta_{E_a}} & 4.9 \  ho s \end{array}$ |      | 4.9 ps               |

| Resultado                                                                                                |      |                      |

| n                                                                                                        |      | 2.8                  |

Tabela (5. 3). Calculo da resolução DAC PWM

| Resolução DAC PWM |   |                      |

|-------------------|---|----------------------|

| Equação           |   | Número da<br>equação |

| $N_T = n + N$     |   |                      |

| Dados             |   |                      |

| n                 |   | 3                    |

| N                 | 4 |                      |

| Resultado         |   |                      |

| $N_T$             |   | 7                    |

Tabela (5. 4). Calculo do número de portas logicas no elemento de atraso.

| Número de portas logicas no elemento de atraso |                   |        |  |

|------------------------------------------------|-------------------|--------|--|

| Equação Número da equação                      |                   |        |  |

| $N_p = \frac{1}{2^n f_{CLK} \delta}$           | $\frac{1}{16E_a}$ | (4.15) |  |

| Dados                                          |                   |        |  |

| n                                              |                   | 3      |  |

| $f_{CLK}$                                      | 210Mhz            |        |  |

| $\delta_{E_a}$                                 | 59.5 ps           |        |  |

| Resultado                                      |                   |        |  |

| $N_p$                                          |                   | 10     |  |

Tabela (5. 5). Calculo da frequência DAC PWM.

| Frequência DAC PWM                 |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |         |

|------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------|

| Equação                            | the state of the s |         |

|                                    |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | equação |

| $f_{PWM} = \frac{f_{CLK}}{2^{Nt}}$ | $f_{PWM} = \frac{f_{CLK}}{2^{Nt}} \tag{4.16}$                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |         |

| Dados                              |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |         |

| $f_{CLK}$                          | <i>f<sub>CLK</sub></i> 210Mhz                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |         |

| $N_T$                              | 7                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |         |