### UNIVERSIDADE FEDERAL DE ITAJUBÁ PROGRAMA DE PÓS-GRADUAÇÃO EM ENGENHARIA ELÉTRICA

#### THIAGO POUZA MUSSOLINI

### DESENVOLVIMENTO DE UM MICROCONTROLADOR DE 8 BITS EM VHDL BASEADO NO CONJUNTO DE INSTRUÇÕES DO 8051 COM COMUNICAÇÃO SERIAL I<sup>2</sup>C E CRIPTOGRAFIA AES128

Dissertação submetida ao Programa de Pós-Graduação em Engenharia Elétrica da UNIFEI como requisito parcial para a obtenção do título de Mestre em Engenharia Elétrica

Área de Concentração: Microeletrônica

Orientador: Professor Tales Cleber Pimenta Co-orientador: Professor Robson Luiz Moreno

> Julho de 2011 Itajubá – MG

| "Nunca se afaste de seus sonhos, pois se eles se forem,<br>você continuará vivendo, mas terá deixado de existir." |

|-------------------------------------------------------------------------------------------------------------------|

| Charles Chaplin.                                                                                                  |

ii

# Agradecimentos

Aos meus pais, Reinaldo e Maria do Carmo.

À minha namorada Juliana.

Ao meu orientador Tales Cleber Pimenta.

Ao meu co-orientador Robson Luiz Moreno.

À Universidade Federal de Itajubá.

Ao Grupo e aos amigos da Microeletrônica.

Ao pessoal da MINASIC.

## Resumo

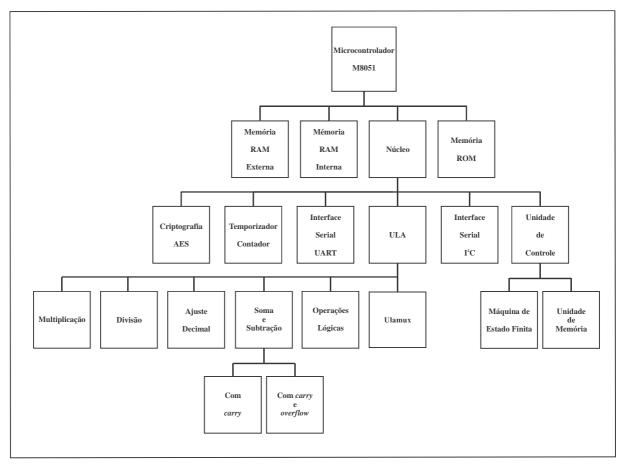

Apresenta-se neste trabalho a estrutura de um microcontrolador de 8 bits em linguagem VHDL. Ele é baseado no conjunto de instruções do popular 8051 e modificações em sua arquitetura original foram realizadas para adequação as necessidades do Grupo de Microeletrônica da UNIFEI.

Com a utilização da linguagem VHDL é possível realizar modificações na arquitetura do microcontrolador para acrescentar novas funcionalidades ou simplesmente retirar as que não sejam necessárias e imediatamente realizar simulações por *softwares* e/ou prototipação para testes de funcionamento em FPGA.

O microcontrolador M8051, desenvolvido foi validado através de simulações de cada hierarquia construída e também seu conjunto. Através dos programas desenvolvidos em linguagem *assembly* foram realizados testes do funcionamento da estrutura em FPGA para garantir a funcionalidade de todos os recursos presentes.

## Abstract

This paper presents the structure of an 8-bit microcontroller in VHDL. It is based on the instruction set of the popular 8051 and modifications on the original architecture were made to meet the demands and needs of the Microelectronics Group.

VHDL allows modifications to be made in the microcontroller architecture such as adding new functionality or just removing those that are not necessary and perform simulation or FPGA implementation.

The microcontroller M8051, was developed and validated through simulations of each hierarchy and the whole set tests were performed in the through assembly programming and FPGA implementation to ensure functionality of all features presented.

# Sumário

| 1 | Introduç  | ção                                                     | 10 |

|---|-----------|---------------------------------------------------------|----|

|   | 1.1 Mot   | tivação e Objetivos                                     | 10 |

|   | 1.2 Org   | anização da dissertação                                 | 11 |

| 2 | FPGA e    | VHDL                                                    | 12 |

|   | 2.1 Intro | odução                                                  | 12 |

|   | 2.2 PLI   | )                                                       | 12 |

|   | 2.2.1     | FPGA                                                    | 12 |

|   | 2.2.2     | Cyclone II EP2C35F672C6                                 | 13 |

|   | 2.2.3     | DE2                                                     |    |

|   | 2.3 VH    | DL                                                      | 14 |

|   | 2.3.1     | História                                                | 15 |

|   | 2.3.2     | Definição                                               | 16 |

|   | 2.3.3     | Vantagens e desvantagens                                | 17 |

| 3 | Microco   | ontrolador 8051                                         | 18 |

|   | 3.1 Intro | odução                                                  | 18 |

|   | 3.2 Arq   | uitetura do microcontrolador 8051                       | 20 |

|   | 3.2.1     | Organização das Memórias                                | 20 |

|   | 3.2.2     | Registro de Funções Especiais                           | 22 |

|   | 3.2.3     | Instruções                                              | 23 |

|   | 3.2.4     | Pinos                                                   | 29 |

| 4 | Estrutur  | a do projeto em VHDL                                    | 31 |

|   | 4.1 Intro | odução                                                  | 31 |

|   | 4.2 Estr  | utura em blocos do microcontrolador                     |    |

|   | 4.2.1     | Bloco de Adição e Subtração com carry/borrow            | 32 |

|   | 4.2.2     | Bloco de Adição e Subtração com carry/borrow e overflow | 33 |

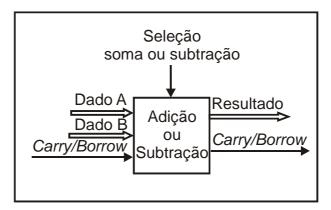

|   | 4.2.3     | Bloco de Adição ou Subtração                            |    |

|   | 4.2.4     | Bloco Multiplicação                                     | 36 |

|   | 4.2.5     | Bloco Divisão                                           | 37 |

|   | 4.2.6     | Bloco Operações Lógicas                                 | 38 |

|   | 4.2.7     | Bloco Ajuste Decimal                                    | 39 |

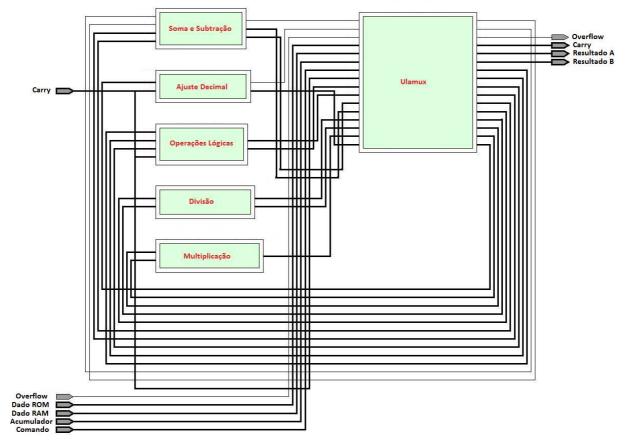

|   | 4.2.8     | Bloco Ulamux                                            | 40 |

|   | 4.2.9     | Bloco ULA                                               | 40 |

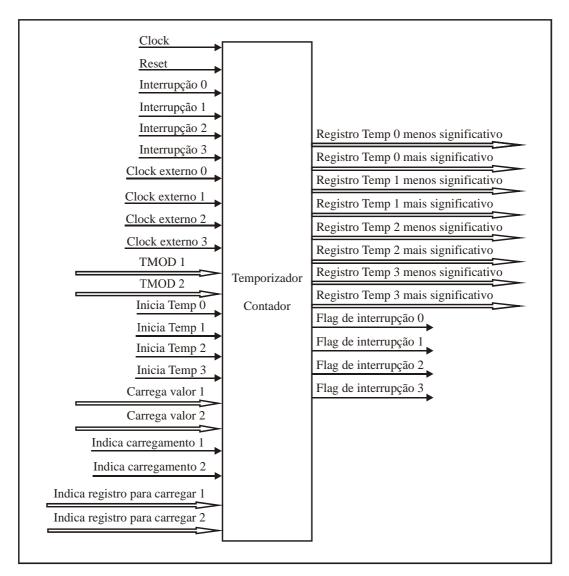

|   | 4.2.10    | Bloco Temporizador/Contador                             |    |

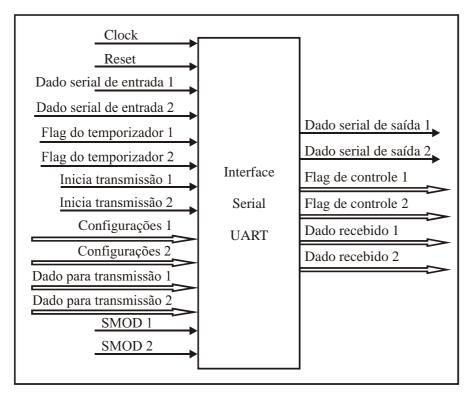

|   | 4.2.11    | Bloco Interface Serial UART                             | 42 |

|   | 4.2.12    | Bloco Unidade de Controle                               | 43 |

|   | 4.2.13    | Bloco Máquina de Estado Finita                          | 44 |

|   | 4.2.14    | Bloco Unidade de Memória                                |    |

|   | 4.2.15    | Bloco Interface Serial I <sup>2</sup> C                 |    |

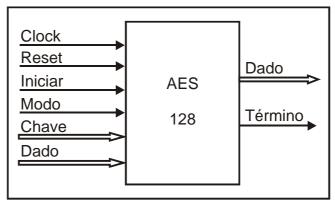

|   | 4.2.16    | Bloco Criptografia AES 128                              |    |

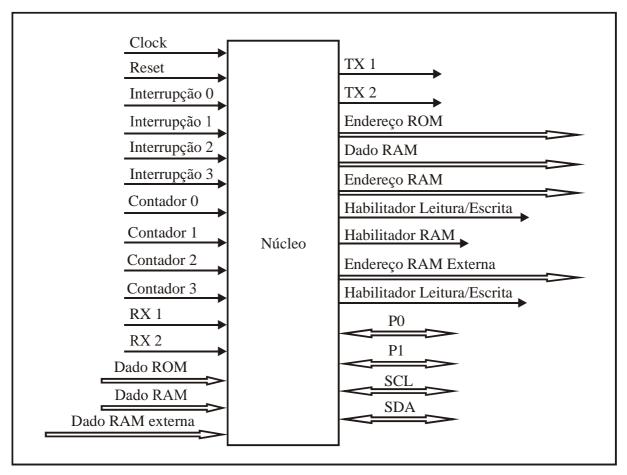

|   | 4.2.17    | Bloco Núcleo                                            |    |

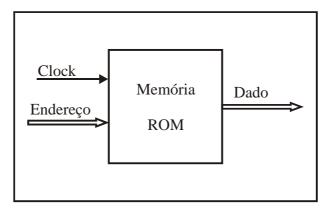

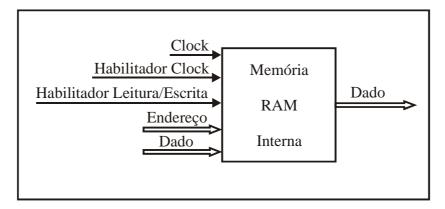

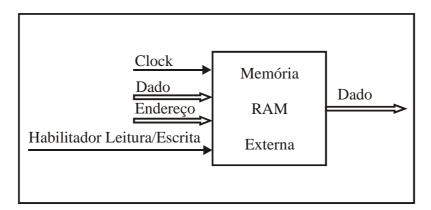

|   | 4.2.18    | Blocos das Memórias ROM, RAM Interna e RAM Externa      |    |

|   | 4.2.19    | Bloco Microcontrolador M8051                            |    |

|   | 4.3 Con   | nclusão                                                 | 49 |

| 5 | Interfac  | e de Comunicação Serial I <sup>2</sup> C                | 50 |

|   | 5.1                 | Introdução                                                                     | 50 |

|---|---------------------|--------------------------------------------------------------------------------|----|

|   | 5.2                 | O Pradrão de Comunicação Serial I <sup>2</sup> C                               | 50 |

|   | 5.2.                |                                                                                | 53 |

|   | 5.2.                |                                                                                | 56 |

|   | 5.3                 | Conclusão.                                                                     |    |

| 6 | Cri                 | ptografia AES 128                                                              | 61 |

|   | 6.1                 | Introdução                                                                     |    |

|   | 6.2                 | Histórico                                                                      |    |

|   | 6.3                 | O algoritmo Rijndael                                                           |    |

|   | 6.4                 | Operação do AES                                                                |    |

|   | 6.5                 | Implementação e Integração no M8051                                            |    |

|   | 6.6                 | Conclusão.                                                                     |    |

| 7 | Cor                 | nclusões                                                                       |    |

| 8 | Apé                 | êndices                                                                        | 75 |

|   | 8.1                 | Apêndice A – Rotina desenvolvida no software μVision4 para utilização do bloco |    |

|   | I <sup>2</sup> C in | tegrado ao M8051.                                                              | 75 |

|   | 8.2                 | Apêndice B – Rotina desenvolvida no software μVision4 para utilização do bloco |    |

|   | AES1                | 28 integrado ao M8051.                                                         | 76 |

| 9 |                     | Perências Bibliográficas                                                       |    |

|   |                     |                                                                                |    |

# Lista de Figuras

| CAPÍTULO 2                                                                                  | 12 |

|---------------------------------------------------------------------------------------------|----|

| Figura 2.1 - Arquitetura do FPGA                                                            | 13 |

| Figura 2.2 - Sistema de Desenvolvimento DE2.                                                |    |

| CAPÍTULO 3                                                                                  | 10 |

|                                                                                             |    |

| Figura 3.1 – Representação da arquitetura da estrutura original do 8051.                    |    |

| Figura 3.2 - Organização da memória de programa.                                            |    |

| Figura 3.3 – Organização da memória de dados.                                               |    |

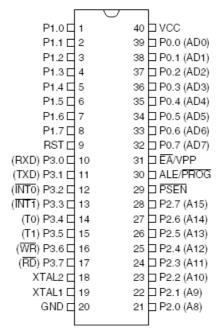

| Figura 3.4 – Pinos do microcontrolador 8051.                                                | 30 |

| CAPÍTULO 4                                                                                  | 31 |

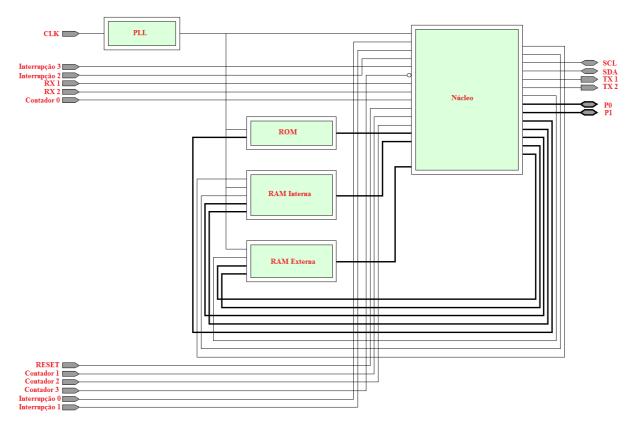

| Figura 4.1 - Estrutura em blocos dos níveis hierárquico do Microcontrolador M8051           | 32 |

| Figura 4.2 – Representação do bloco de adição e subtração com <i>carry/borrow</i>           |    |

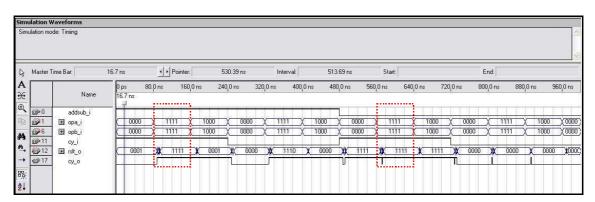

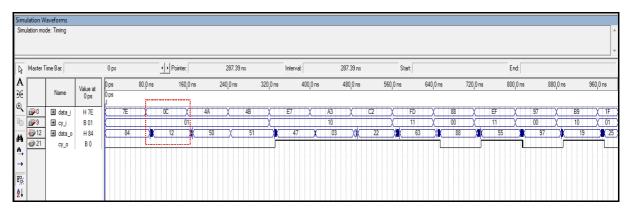

| Figura 4.3 - Resultado das operações de soma e subtração com e sem carry de entrada         |    |

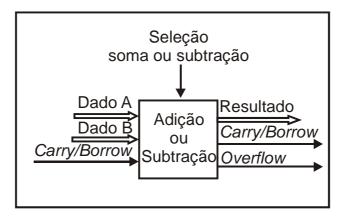

| Figura 4.4 – Representação do bloco de adição e subtração com carry/borrow e overflow       |    |

| Figura 4.5 - Resultado das operações de soma e subtração                                    |    |

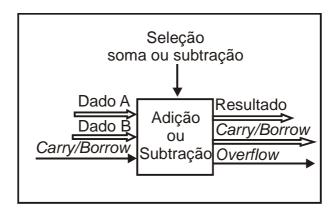

| Figura 4.6 – Representação do bloco de adição e subtração com carry/borrow e overflow       | 35 |

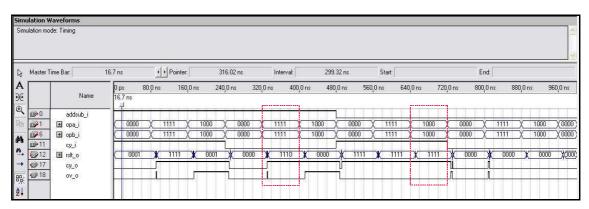

| Figura 4.7- Resultado das operações de soma e subtração com e sem <i>carry</i> de entrada e |    |

| considerando overflow.                                                                      | 36 |

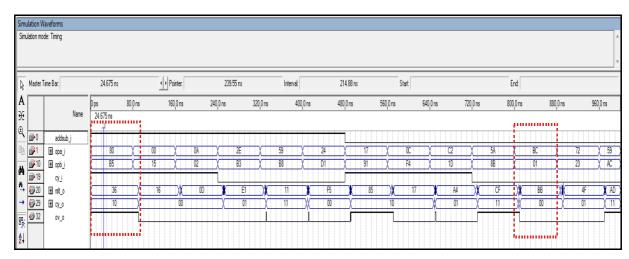

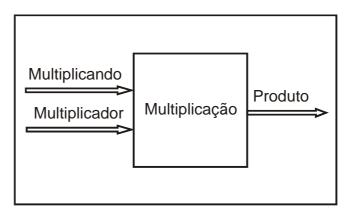

| Figura 4.8 – Representação do bloco de multiplicação.                                       | 36 |

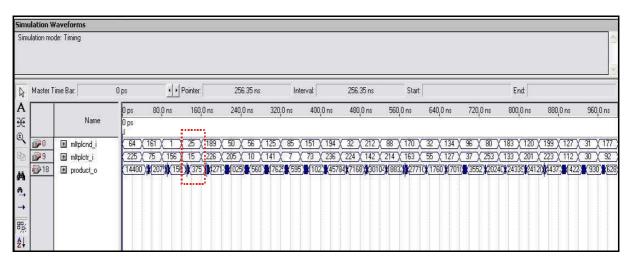

| Figura 4.9 - Resultado da operação multiplicação.                                           | 37 |

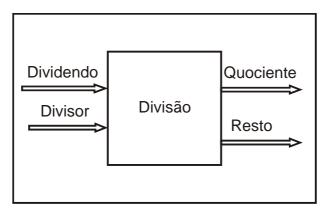

| Figura 4.10 – Representação do bloco de divisão.                                            | 37 |

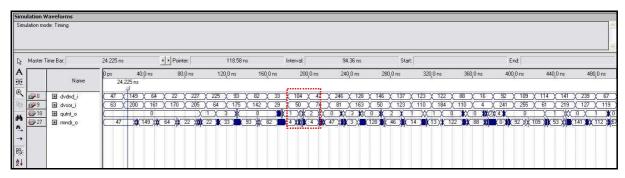

| Figura 4.11 - Resultado da operação divisão                                                 | 38 |

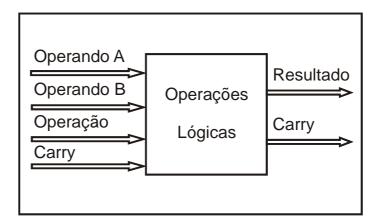

| Figura 4.12 – Representação do bloco de Operações Lógicas.                                  | 38 |

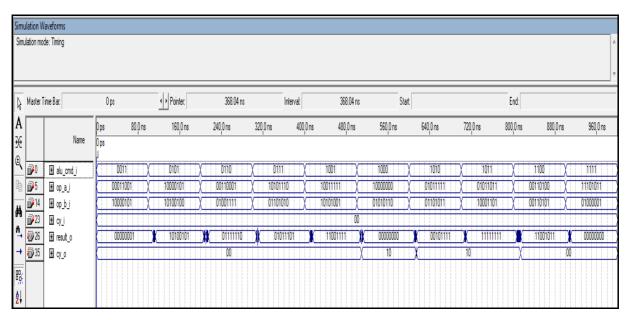

| Figura 4.13 - Resultado das operações lógicas.                                              |    |

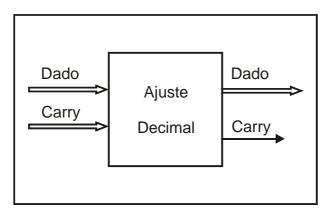

| Figura 4.14 – Representação do bloco de Ajuste Decimal                                      | 39 |

| Figura 4.15 - Resultado do ajuste decimal.                                                  | 40 |

| Figura 4.16 – Representação do Bloco ULA baseado no circuito gerado                         | 41 |

| Figura 4.17 – Representação do Bloco Temporizador/Contador.                                 |    |

| Figura 4.18 – Representação do Bloco Interface Serial UART.                                 |    |

| Figura 4.19 – Representação do bloco núcleo.                                                |    |

| Figura 4.20 - Representação do bloco de memória ROM                                         |    |

| Figura 4.21 - Representação do bloco de memória RAM Interna                                 |    |

| Figura 4.22 - Representação do bloco de memória RAM Externa                                 |    |

| Figura 4.23 – Representação do Bloco M8051 baseado no circuito gerado                       | 48 |

| CAPÍTULO 5                                                                                  | 51 |

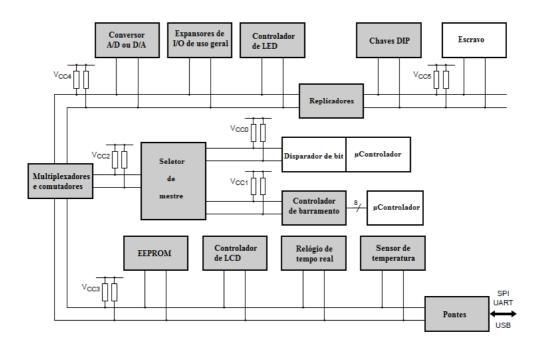

| Figura 5.1 - Exemplo de aplicação do barramento I <sup>2</sup> C                            |    |

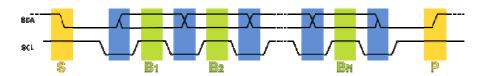

| Figura 5.2 - Diagrama de tempo de uma transferência de dados                                |    |

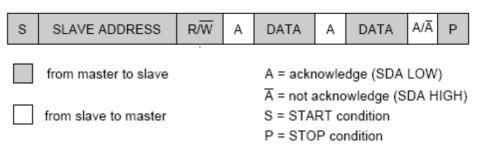

| Figura 5.3 – Protocolo de comunicação I <sup>2</sup> C.                                     |    |

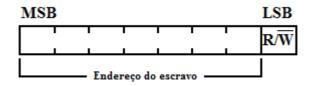

| Figura 5.4 – Orientação do endereço do escravo                                              |    |

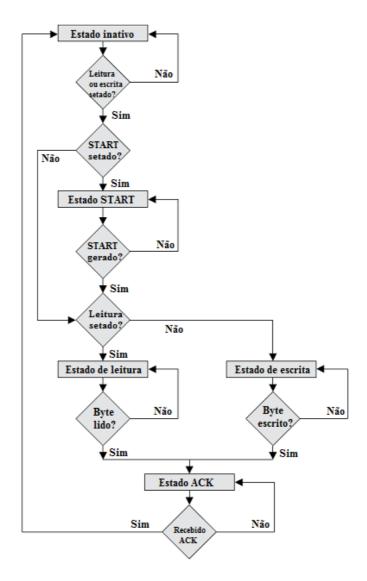

| Figura 5.5 – Fluxograma do processo do sub-bloco <i>Byte Command Controller</i>             |    |

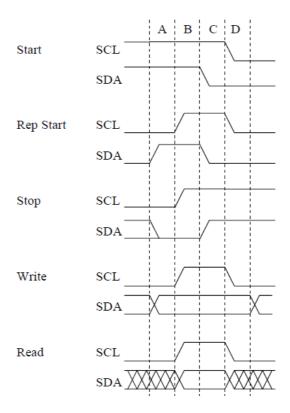

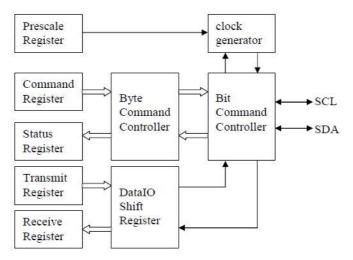

| Figura 5.7 – Representação do fluxo de dados do bloco I <sup>2</sup> C                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | Figura 5.6 – Níveis lógico dos sinais de cada ação em relação ao tempo                       | 55   |

|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------|------|

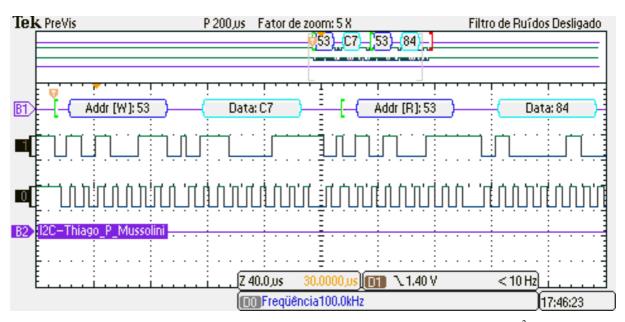

| Figura 5.9 – Processo de leitura de posição de memória através da comunicação I <sup>2</sup> C                                                                                                                                                                                                                                                                                                                                                                                                                                          | Figura 5.7 – Representação do fluxo de dados do bloco I <sup>2</sup> C                       | 55   |

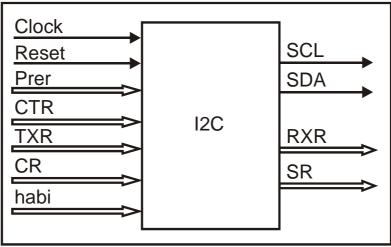

| Figura 5.9 – Processo de leitura de posição de memória através da comunicação I <sup>2</sup> C                                                                                                                                                                                                                                                                                                                                                                                                                                          | Figura 5.8 - Representação do bloco I2C.                                                     | 56   |

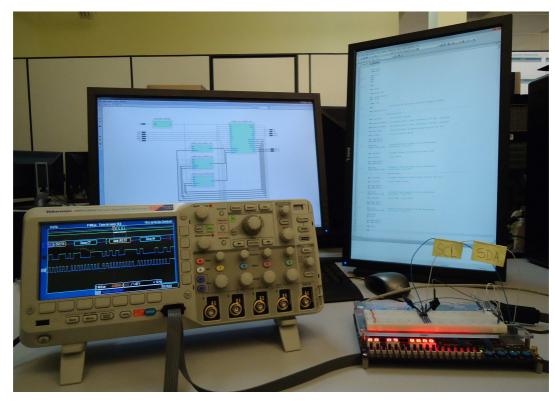

| Figura 5.10 – Estrutura para teste da comunicação serial I <sup>2</sup> C com vista frontal                                                                                                                                                                                                                                                                                                                                                                                                                                             |                                                                                              |      |

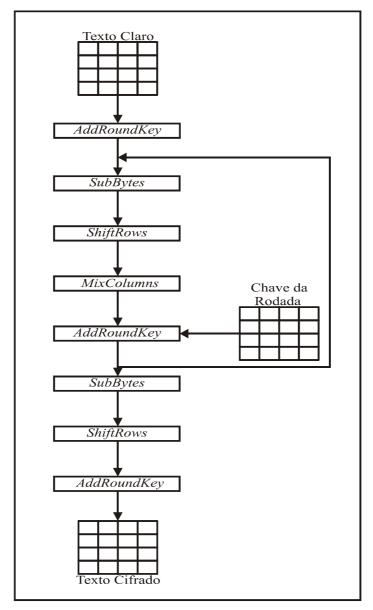

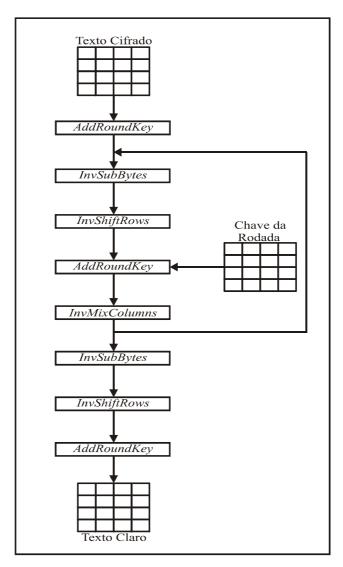

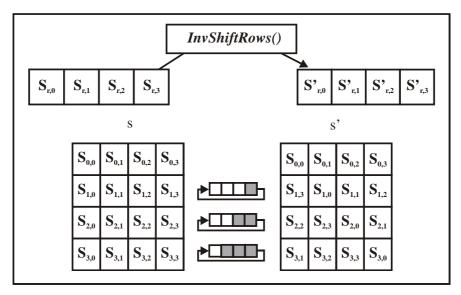

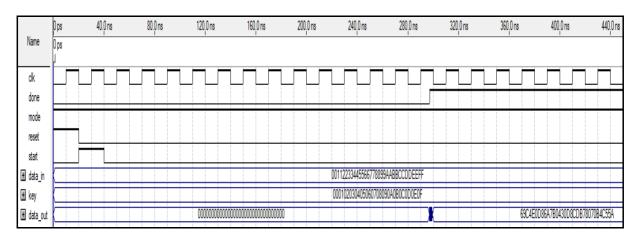

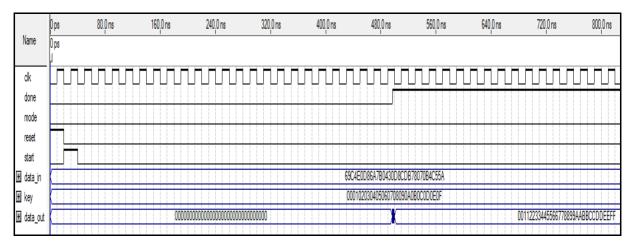

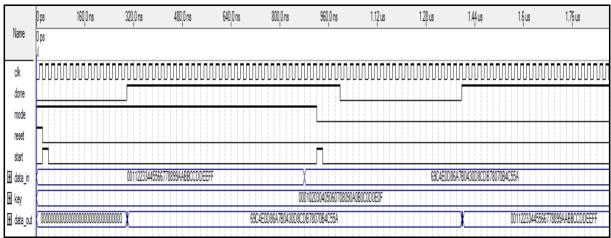

| CAPÍTULO 6Figura 6.1 – Processo de Criptografia.63Figura 6.2 – Etapa AddRoundKey.63Figura 6.3 – Etapa SubBytes.64Figura 6.4 – Etapa ShiftRows.65Figura 6.5 – Processo de Decriptografia.65Figura 6.6 – Etapa InvShiftRows.66Figura 6.7 – Constante para a etapa InvMixColumns.67Figura 6.8 – Constantes das rodadas.67Figura 6.9 – Representação do bloco de criptografia AES128.69Figura 6.10 – Resultado da simulação do bloco AES128 para criptografia.70Figura 6.11 – Resultado da simulação do bloco AES128 para decriptografia.70 |                                                                                              |      |

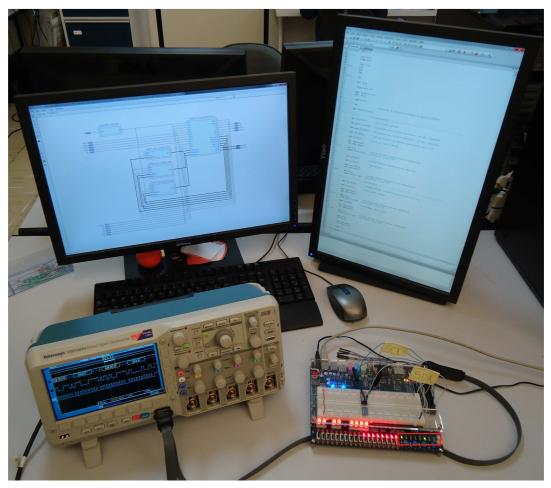

| Figura 6.1 – Processo de Criptografia.63Figura 6.2 – Etapa AddRoundKey.63Figura 6.3 – Etapa SubBytes.64Figura 6.4 – Etapa ShiftRows.65Figura 6.5 – Processo de Decriptografia.65Figura 6.6 – Etapa InvShiftRows.66Figura 6.7 – Constante para a etapa InvMixColumns.67Figura 6.8 – Constantes das rodadas.67Figura 6.9 – Representação do bloco de criptografia AES128.69Figura 6.10 – Resultado da simulação do bloco AES128 para criptografia.70Figura 6.11 – Resultado da simulação do bloco AES128 para decriptografia.70           | Figura 5.11 – Estrutura para teste da comunicação serial I <sup>2</sup> C com vista superior | 59   |

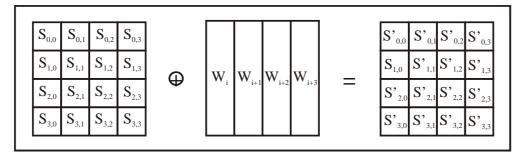

| Figura 6.2 – Etapa AddRoundKey                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | CAPÍTULO 6                                                                                   | 62   |

| Figura 6.2 – Etapa AddRoundKey                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | Figura 6.1 – Processo de Criptografia.                                                       | 63   |

| Figura 6.4 – Etapa ShiftRows                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | Figura 6.2 – Etapa <i>AddRoundKey</i>                                                        | 63   |

| Figura 6.5 – Processo de Decriptografia                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | Figura 6.3 – Etapa SubBytes.                                                                 | 64   |

| Figura 6.6 – Etapa InvShiftRows                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | Figura 6.4 – Etapa ShiftRows.                                                                | 65   |

| Figura 6.7 – Constante para a etapa <i>InvMixColumns</i>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | Figura 6.5 – Processo de Decriptografia.                                                     | 65   |

| Figura 6.8 – Constantes das rodadas                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | Figura 6.6 – Etapa InvShiftRows                                                              | 66   |

| Figura 6.9 – Representação do bloco de criptografia AES128                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | Figura 6.7 – Constante para a etapa <i>InvMixColumns</i> .                                   | 67   |

| Figura 6.10 – Resultado da simulação do bloco AES128 para criptografia70 Figura 6.11 – Resultado da simulação do bloco AES128 para decriptografia70                                                                                                                                                                                                                                                                                                                                                                                     | Figura 6.8 – Constantes das rodadas.                                                         | 67   |

| Figura 6.11 – Resultado da simulação do bloco AES128 para decriptografia70                                                                                                                                                                                                                                                                                                                                                                                                                                                              | Figura 6.9 – Representação do bloco de criptografia AES128                                   | 69   |

| , , , , , , , , , , , , , , , , , , , ,                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | Figura 6.10 – Resultado da simulação do bloco AES128 para criptografia                       | 70   |

| Figura 6.12 – Resultado da simulação do bloco AES128 para criptografia e decriptografia71                                                                                                                                                                                                                                                                                                                                                                                                                                               | Figura 6.11 – Resultado da simulação do bloco AES128 para decriptografia                     | 70   |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | Figura 6.12 – Resultado da simulação do bloco AES128 para criptografia e decriptograf        | ia71 |

## Lista de Tabelas

| CAPÍTULO 3                                                            | 18 |

|-----------------------------------------------------------------------|----|

| Tabela 3.1– Endereço e Ordem de prioridade                            | 19 |

| Tabela 3.2 – Registros de Funções Especiais                           |    |

| Tabela 3.3 – Valores do SFRs após RESET                               |    |

| Tabela 3.4 – Modo de endereçamento                                    |    |

| Tabela 3.5 – Conjunto de instruções do 8051.                          | 24 |

| Tabela 3.6 – Funcionalidades dos pinos do 8051                        | 29 |

| CAPÍTULO 4                                                            | 31 |

| Tabela 4.1 – Endereço e Ordem de prioridade                           | 49 |

| CAPÍTULO 5                                                            | 51 |

| Tabela 5.1 - Posições de memórias e registros referentes ao bloco I2C | 57 |

| CAPÍTULO 6                                                            | 62 |

| Tabela 6.1 – Possibilidades de configurações do AES                   | 62 |

| Tabela 6.2 – S-Box                                                    |    |

| Tabela 6.3 – <i>InvS-Box</i>                                          | 66 |

| Tabela 6.4 – Registros do bloco AES 128.                              | 72 |

## Lista de abreviaturas

PLD Programmable Logic Devices

FPGA Field Programmable Gate Array

IC Integrated Circuit

CLB Configurable Logic Block

LUT Lookup Table

SRAM Static Random Access Memory

ASIC Application Specific Integrated Circuit

VHDL Very High Speed Integrated Circuit Hardware Description Language

DoD Department of Defense

VHSIC Very High Speed Integrated Circuit

IEEE Institute of Electrical and Electronic Engineers

CPU Center Processing Unit

I/O In put/ Out put

UART Universal Asynchronous Receiver Transmitter

CISC Complex Instruction Set Computer

SFR Special Function Register

PSW Program Status Word

POR Power On Reset

ULA Unidade Lógica Aritmética

RAM Random Access Memory

FIFO First-In, First-Out

ROM Read Only Memory

SDA Serial Data

SCL Serial Clock

## Capítulo 1

### 1 Introdução

Com a evolução da tecnologia de semicondutores e consequentemente do mundo digital, os microcontroladores tornaram-se presentes em praticamente todos os produtos digitais, desde um simples controle de portão de garagem até aos mais modernos celulares.

Outra vertente que evoluiu junto com os semicondutores foram os Dispositivos Lógicos Programáveis – PLD (*Programmable Logic Device*), principalmente o Arranjo de Portas Programável em Campo - FPGA (*Field Programmable Gate Arrays*). Eles permitem que um circuito digital seja prototipado e testado pelo usuário em campo, sendo que, caso seja necessário alterações no circuito desenvolvido estas possam ser realizadas rapidamente sem nenhuma perda.

Com isso surge um novo segmento de pesquisa e desenvolvimento que é a implementação de microcontroladores ou microprocessadores em FPGAs. Empresas como Altera e Xilinx possuem suas próprias arquiteturas, o NIOS II e o Microblaze, respectivamente. Outras empresas, como a ARM e a Intel, em parcerias com a Xilinx, também disponibilizam versões de núcleos comerciais para projetos em FPGA.

### 1.1 Motivação e Objetivos

O Grupo de Microeletrônica da Universidade Federal de Itajubá – UNIFEI através de diversos trabalhos realizados com FPGA e com o auxilio das estruturas proprietárias dos microprocessadores adquiriu ao longo dos anos uma vasta experiência. Contudo, para diminuir a dependência dessas arquiteturas auxiliares proprietárias iniciaram-se os trabalhos para que o grupo pudesse adquirir também o conhecimento em desenvolvimento de microcontroladores que, em paralelo, atendesse as demandas dos trabalhos em desenvolvimento e futuros.

O objetivo deste trabalho é desenvolver um circuito flexível, que seja possível realizar alterações em sua estrutura como, por exemplo, a introdução de novos periféricos ou a

exclusão de uma porta para a diminuição da quantidade de pinos, porém, com um conjunto de instruções fixo e altamente difundido.

#### 1.2 Organização da dissertação

Esta dissertação está dividida em sete capítulos e dois apêndices. No Capítulo 2 é feita uma apresentação da tecnologia FPGA e da linguagem VHDL destacando suas principais características. Também é apresentado o sistema de desenvolvimento utilizado para realizar este trabalho.

O Capítulo 3 aborda as características do microcontrolador 8051 da Intel como capacidade de memória, conjunto de instruções, pinos e entre outros para a familiarização com as características do circuito.

A estrutura concebida para o desenvolvimento do microcontrolador M8051 é apresentada no Capítulo 4. Nele encontram-se as representações dos blocos implementados com os sinais de entrada e saída, comprovações de funcionamento correto através de *waveforms* ou *testbenchs* e uma explicação das ações realizadas.

No Capítulo 5 são apresentadas as etapas envolvidas no desenvolvimento da interface de comunicação serial I<sup>2</sup>C, como ela foi integrada ao M8051, um exemplo de como utilizá-la e as comprovações de seu correto funcionamento.

O algoritmo de criptografia AES128 é apresentado no Capítulo 6. Nele encontram-se, também, as etapas realizadas para o desenvolvimento do bloco, os testes realizados para comprovação do funcionamento correto, como foi realizada a integração e um exemplo de como utilizar a estrutura.

No Capítulo 7 é feita uma análise dos resultados apresentados e a conclusão do estudo desenvolvido. Ainda nesse capítulo, são sugeridas idéias para trabalhos futuros.

O apêndice A contém o programa desenvolvido em linguagem *assembly* para utilização e gerenciamento da interface I<sup>2</sup>C e o apêndice B contém o programa desenvolvido em linguagem *assembly* para utilização e gerenciamento da criptografia AES128.

## Capítulo 2

#### 2 FPGA e VHDL

#### 2.1 Introdução

Esse capítulo apresenta a estrutura básica de um FPGA e o conceito da linguagem VHDL. O FPGA que terá suas características abordadas é a Cyclone II EP2C35F672C6 da Altera, presente no sistema de desenvolvimento DE2 da Terasic Technologies. A linguagem adotada para o desenvolvimento deste *hardware* foi a VHDL devido ao maior domínio do Grupo de Microeletrônica quando comparado com as demais linguagens existentes para tal finalidade.

#### 2.2 PLD

Os PLDs são Circuitos Integrados – IC (*Integrated Circuit*) compostos basicamente por portas lógicas, *flip-flop* e registradores. Estas estruturas estão interconectadas através de fusíveis ou chaves especiais que podem ser configuradas e reconfiguradas para cada lógica desenvolvida [1]. Existem vários tipos de PLD e um de grande importância para a indústria é o FPGA [2].

#### 2.2.1 FPGA

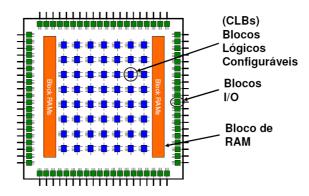

Dos diversos tipos de PLD, o FPGA é o mais complexo. Consiste em um arranjo bidimensional de blocos lógico-programáveis conectados entre si por meio de uma estrutura de interconexões (*Switch Matrix*), como mostrado na Figura 2.1. A estrutura interna do Bloco Lógico Configurável - CLB (*Configurable Logic Block*) é baseada em LUT (*Lookup Table*).

Figura 2.1 - Arquitetura do FPGA.

Essa tecnologia foi desenvolvida pela empresa Xilinx Inc., em 1985, para ser um dispositivo programável de acordo com as necessidades do projetista. Também permiti realizar prototipações de etapas intermediárias do circuito desenvolvido e/ou alterações do projeto final em tempo extremamente reduzido e com custos mais baixos em comparação com todo o processo de um Circuito Integrado para Aplicação Específica – ASIC (*Application Specific Integrated Circuit*).

Por ser um circuito lógico programável ou computação reconfigurável se torna uma opção intermediária na solução de lógicas complexas, pois combina o alto desempenho do *hardware* com a flexibilidade do *software*.

Para configurar o FPGA é utilizado um arquivo binário que contém as informações necessárias para especificar a função de cada unidade lógica e fechar as chaves da matriz de interconexão necessárias. Para gerar o arquivo binário utilizam-se ferramentas de *software* seguindo um determinado fluxo de projeto [2]. Neste projeto foi utilizado o *software* Quartus II 9.1 SP2 Web Edition que é uma versão disponibilizada pela Altera gratuitamente.

Dentre os vários segmentos em relação às arquiteturas reconfiguráveis, destacam-se os processadores reconfiguráveis. Estes processadores combinam as funções de um microprocessador com uma lógica reconfigurável e podem ser adaptados depois do processo de desenvolvimento [3].

#### **2.2.2** Cyclone II EP2C35F672C6

Adotou-se para o desenvolvimento desse projeto, o FPGA Cyclone II EP2C35F672C6 da Família Cyclone II da Altera que é implementado em tecnologia 90nm [4]. As características principais da EP2C35F672C6 são apresentadas na Tabela 2.1.

| Características                                    | EP2C35F672C6 |

|----------------------------------------------------|--------------|

| Quantidade de Pinos                                | 672          |

| Elementos Lógicos                                  | 33216        |

| Blocos RAM M4K (4 kbits mais 512 bits de paridade) | 105          |

| Total RAM bits                                     | 483840       |

| Multiplicadores Embarcados 9 X 9 bits              | 70           |

| PLLs                                               | 4            |

| Quantidade máxima de pinos utilizáveis para I/O    | 475          |

Tabela 2.1- Características do FPGA EP2C35F672C6 [4].

Os FPGAs da família Cyclone II utilizam Memórias Estáticas de Acesso Aleatório – SRAMs (*Static Random Access Memory*), as quais são voláteis, para armazenar suas configurações. Com isso, o arquivo de configuração deve ser transferido para o FPGA toda vez que o sistema for energizado.

Para a transferência do arquivo de configuração do FPGA com o circuito desenvolvido é utilizada a tecnologia Grupo de Ação Conjunta de Teste - JTAG (*Joint Test Action Group*) [5]. O *software* Quartus II da Altera gera automaticamente o arquivo binário de configuração do FPGA e a tecnologia JTAG, através do cabo *USB-Blaster*, torna o processo de gravação do circuito no sistema de desenvolvimento extremamente simples e rápido.

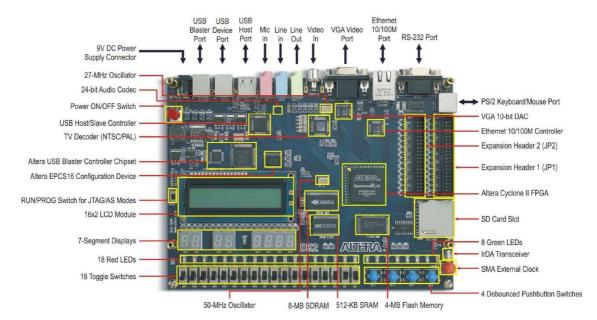

#### 2.2.3 DE2

O sistema de desenvolvimento DE2 apresenta diversos periféricos, facilitando a realização de testes de circuitos desenvolvidos. Estes periféricos são mostrados na Figura 2.2 e as informações técnicas do sistema podem ser encontradas na referência [5].

#### **2.3 VHDL**

A Linguagem de Descrição de *Hardware* de Circuitos Integrados de Altíssima Velocidade – VHDL (*Very High Speed Integrated Circuit Hardware Description Language*) foi desenvolvida com o intuito de ser utilizada em todas as fases da criação de um sistema eletrônico digital. Ela promove o desenvolvimento, verificação, síntese e teste no desenvolvimento do *hardware*, bem como sua manutenção, modificação e expansão [6].

Figura 2.2 - Sistema de Desenvolvimento DE2 [5].

#### 2.3.1 História

Foi originalmente desenvolvida sob o comando do Departamento de Defesa – DoD (*Department of Defense*) dos Estados Unidos, em meados da década de 1980, para documentar o comportamento de ASICs que compunham os equipamentos vendidos às Forças Armadas Americanas. A linguagem foi desenvolvida para substituir os complexos manuais que descreviam o funcionamento dos ASICs. A única metodologia largamente utilizada no projeto de circuitos era a criação através de diagramas de esquemáticos que possuíam como problema o fato de terem menor portabilidade, serem mais complexos para compreensão e extremamente dependentes da ferramenta utilizada para produzi-los [7].

Como os projetos de Circuito Integrado de Altíssima Velocidade - VHSIC (*Very High Speed Integrated Circuit*) eram de alta prioridade militar e haviam dezenas de fornecedores envolvidos, o DoD estava preocupado principalmente com as questões de portabilidade, documentação e compreensibilidade dos projetos. Cada um destes fornecedores atuava desenvolvendo partes dos projetos ou mesmo fornecendo componentes que viriam a se encaixar em outros sistemas maiores. Desta forma, o DoD optou por buscar desenvolver uma linguagem que servisse como base para a troca de informações sobre estes componentes e projetos. A linguagem deveria ser independente do formato original do circuito, e deveria servir como uma descrição e documentação eficiente do circuito, possibilitando os mais diferentes fornecedores e participantes a entender o funcionamento das outras partes e padronizando a comunicação [7].

O desenvolvimento da linguagem VHDL serviu inicialmente aos propósitos de documentação do projeto VHSIC. Entretanto, nesta época buscava-se uma linguagem que facilitasse o projeto de um circuito, ou seja, a partir de uma descrição textual, um algoritmo, pudesse desenvolver o circuito sem necessidade de explicitar as ligações entre componentes. A linguagem encaixa-se adequadamente a tais propósitos, podendo ser utilizada para as tarefas de documentação, descrição, síntese, simulação, teste, verificação formal e em alguns casos a compilação de *software* [7].

Após o sucesso inicial do uso da VHDL, a sua definição foi posta em domínio público o que levou a ser padronizada pelo Instituto de Engenheiros Elétricos e Eletrônicos - IEEE (*Institute of Electrical and Electronic Engineers*) em 1987. O fato de ser padronizada e de ser de domínio público ampliou ainda mais a sua utilização. Novas alterações foram propostas, como é natural num processo de aprimoramento, e a linguagem sofreu uma revisão e um novo padrão mais atualizado, que foi lançado em 1993. Pequenas alterações foram feitas em 2000 e 2002. Em setembro de 2008 foi aprovada pelo Comitê de Revisão do IEEE a mais recente versão, IEEE 1076-2008 [7].

#### 2.3.2 Definição

O VHDL é uma linguagem estruturada que oferece a possibilidade de descrever e simular o *hardware*, com isso facilitando a validação ou verificação, tanto em termos de funcionamento quanto em tempos de atraso dos componentes e desempenho, antes da prototipação do sistema [7].

A descrição pode ser feita basicamente usando dois tipos (modelos) de descrição: estrutural e comportamental. Na descrição estrutural a organização física e topológica do sistema é descrita, ou seja, são especificadas as entradas e/ou saídas, os componentes lógicos, a interligação deles e os sinais que compõem o sistema.

Na descrição comportamental não é preciso descrever a organização física e topológica do sistema, mas, somente, as funções do sistema. Um programa que utiliza esse tipo de descrição possui o mesmo formato de um programa fonte escrito em uma linguagem de programação de alto nível como C++. Essa abordagem diminui a necessidade de conhecimento aprofundado em projeto de *hardware* aumentado a facilidade de desenvolvimento do sistema [7].

#### 2.3.3 Vantagens e desvantagens

Algumas vantagens no uso da linguagem VHDL são projetos independentes da tecnologia, maior facilidade de atualização, exploração de alternativas arquiteturais em um nível mais alto de abstração, eliminação de erros de baixo nível, redução do tempo e custos de projeto e simplificação da documentação. Como desvantagem, o *hardware* gerado é menos otimizado, a controlabilidade/observabilidade de projeto reduzido e as simulações são mais lentas em relação à prototipagem no FPGA [7].

## Capítulo 3

#### 3 Microcontrolador 8051

#### 3.1 Introdução

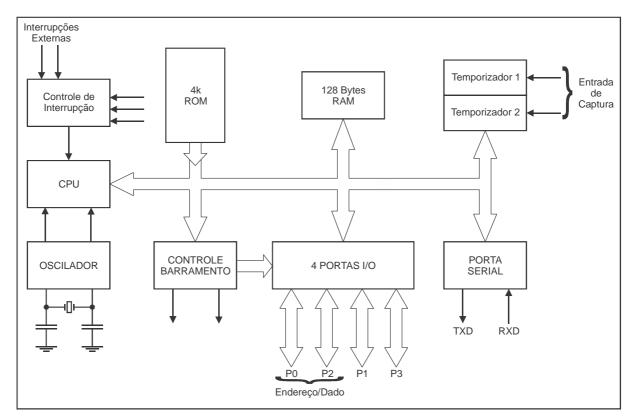

O microcontrolador 8051 é o mais popular [8] entre os microcontroladores e pode operar como um microcontrolador ou como um microprocessador [8] sendo membro original da família MCS-51 e sendo o núcleo (*core*) de todos os dispositivos MCS-51 [9]. A Figura 3.1 apresenta a arquitetura do 8051 com todos os blocos presentes em sua estrutura original.

Figura 3.1 – Representação da arquitetura da estrutura original do 8051 [9].

A Unidade Central de Processamento – CPU (*Central Processing Unit*) do microcontrolador 8051 é otimizada para aplicações de controle e opera com 8 bits. Ela possui a capacidade de processamento booleano que é a ação de realizar processamentos bit a bit.

O microcontrolador 8051 conta com a capacidade de endereçamento externo de até 64 kbytes de espaço de memória, tanto para programa quanto para dados, além de possuir internamente 4k de memória de programa e 128 bytes de memória de dados.

A estrutura do 8051 tem 32 linhas de entrada/saída – I/O (*Input/*Output) bidirecionais e endereçadas individualmente para realizar a interação com outros dispositivos e periféricos como outros microcontroladores, memórias externas, chaves, sensores e *displays*, entre outros. Para utilização de memórias externas, todos os pinos das portas P0 e P2 são utilizados além de alguns pinos específicos.

Para realizar os procedimentos de temporização e/ou contagem, a arquitetura conta com dois registros dedicados de 16 bits, e para a comunicação serial conta com uma interface Transmissor/Receptor Universal Assíncrono — UART (*Universal Asynchronous Receiver Transmitter*) full duplex (transmissão bidirecional). Portanto, para o melhor aproveitamento e gerenciamento dessas estruturas, o microcontrolador tem 5 fontes de interrupções com 5 vetores de tratamento sendo 2 níveis de prioridade (alta ou baixa) selecionáveis por software. As fontes de interrupções são o RESET, dois eventos externos, dois blocos de temporização/contagem e um serial UART, e os níveis de prioridade obedecem à sequência de endereços da Tabela 3.1.

Tabela 3.1– Endereço e Ordem de prioridade das Interrupções na Memória ROM.

| Endereço das Interrupções - ROM |        |                |

|---------------------------------|--------|----------------|

| Prioridade Endereço Tipo        |        | Tipo           |

|                                 | 0x0000 | RESET          |

| 1°                              | 0x0003 | Interrupção 0  |

| 2°                              | 0x000B | Temporizador 0 |

| 3°                              | 0x0013 | Interrupção 1  |

| 4°                              | 0x001B | Temporizador 1 |

| 5°                              | 0x0023 | Serial 1       |

O 8051 contêm a possibilidade de utilizar um oscilador interno ou um oscilador externo com freqüência máxima de 12 MHz, e conta com um conjunto de instruções do tipo Computador com um Conjunto Complexo de Instruções – CISC (*Complex Instruction Set Computer*) de 111 tipos. Considerando as variações de cada tipo totaliza-se 255 instruções em que os códigos de operação estão entre  $00_h$  e FF<sub>h</sub>, excluindo  $A5_h$ , pois é um código reservado.

#### 3.2 Arquitetura do microcontrolador 8051

#### 3.2.1 Organização das Memórias

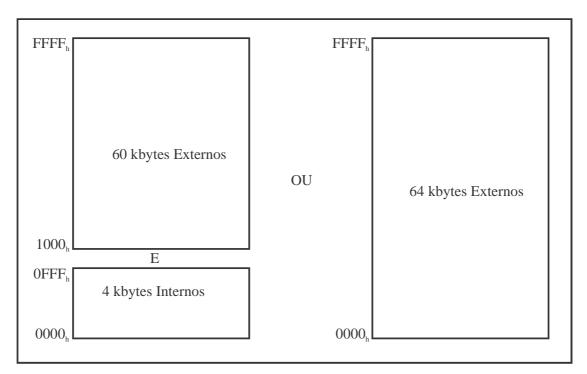

O 8051 possui locações de endereços separados para a memória de programa e para a memória de dados.

A memória de programa pode ser expandida até 64 kbytes. Internamente possui uma memória de 4 kbytes e as possibilidades de utilização das memórias são apresentadas na Figura 3.2.

Figura 3.2 - Organização da memória de programa [9].

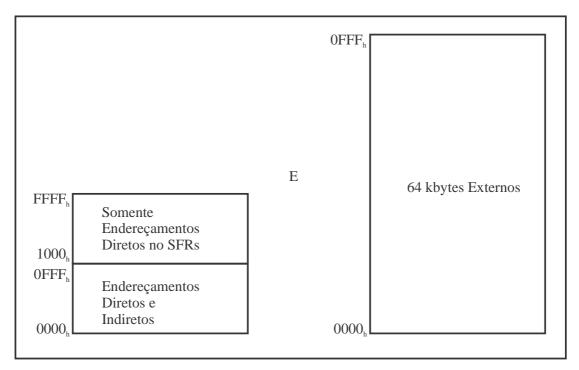

O 8051 pode endereçar até 64 kbytes de memória de dados externa. A instrução MOVX é utilizada para o acesso da memória externa e o microcontrolador possui internamente 128 bytes de RAM e mais 128 bytes de Registros de Funções Especiais – SFR (*Special Function Registers*). Os 128 bytes iniciais podem ser acessados tanto por um endereçamento direto (MOV dado, endereço) ou por um endereçamento indireto (MOV @Ri). A Figura 3.3 apresenta a organização da memória de dados.

Figura 3.3 – Organização da memória de dados [9].

Os 128 bytes da RAM que podem ser acessados por ambos os endereçamentos, direto e indireto, podem ser divididos em 3 segmentos:

- Bancos de Registros 0 até 3: posição de 00<sub>h</sub> até 1F<sub>h</sub> (32 bytes). Após o *RESET*,

o banco de registro padrão será o banco 0. Para utilizar os demais bancos do

8051 deve-se alterar, via *software*, os valores do registro Palavra do Estado do

Programa PSW (*Program Status Word*). Cada banco de registro contém oito

registros de um byte.

- Área de endereçamento por bit: composta por 16 bytes, sendo da posição 20<sub>h</sub> até 2F<sub>h</sub>. Cada um dos 128 bits deste segmento pode ser endereçado diretamente, bit a bit, ou por byte.

- 3. Área para armazenamento temporário: os bytes 30<sub>h</sub> até 7F<sub>h</sub> estão disponíveis para o usuário como dados da RAM. Entretanto, se o apontador de pilha for inicializado nesta área, um número suficiente de bytes deve ser reservado para evitar a perda do dado do apontador de pilha.

### 3.2.2 Registro de Funções Especiais

A Tabela 3.2 apresenta uma lista de todos os registros de funções especiais e seus respectivos endereços. Os SFRs que são bits endereçáveis são apresentados com um \* na frente do nome.

Tabela 3.2 – Registros de Funções Especiais [9].

| Símbolo | Nome                                      | Endereço                   |

|---------|-------------------------------------------|----------------------------|

| *ACC    | Acumulador                                | $E0_h$                     |

| *B      | Registrador B                             | FO <sub>h</sub>            |

| *PSW    | Palavra do Estado do Programa             | $D0_h$                     |

| SP      | Apontador de Pilha                        | 81 <sub>h</sub>            |

| DPTR    | Apontador de dado 2 bytes                 |                            |

| DPL     | Byte Inferior                             | 82 <sub>h</sub>            |

| DPH     | Byte Superior                             | 83 <sub>h</sub>            |

| *P0     | Porta 0                                   | 80 <sub>h</sub>            |

| *P1     | Porta 1                                   | 90 <sub>h</sub>            |

| *P2     | Porta 2                                   | $A0_{h}$                   |

| *P3     | Porta 3                                   | $\mathrm{B0}_{\mathrm{h}}$ |

| *IP     | Controle de Prioridade de Interrupção     | B8 <sub>h</sub>            |

| *IE     | Controle de Habilitação de Interrupção    | A8 <sub>h</sub>            |

| TMOD    | Modo de Controle do Temporizador/Contador | 89 <sub>h</sub>            |

| *TCON   | Controle do Temporizador/Contador         | 88 <sub>h</sub>            |

| TH0     | Byte Superior do Temporizador/Contador 0  | 8C <sub>h</sub>            |

| TL0     | Byte Inferior do Temporizador/Contador 0  | 8A <sub>h</sub>            |

| TH1     | Byte Superior do Temporizador/Contador 1  | 8D <sub>h</sub>            |

| TL1     | Byte Inferior do Temporizador/Contador 1  | 8B <sub>h</sub>            |

| *SCON   | Controle da Serial                        | 98 <sub>h</sub>            |

| SBUF    | Armazenamento de Dado Serial              | 99 <sub>h</sub>            |

| PCON    | Controle de Energia                       | 87 <sub>h</sub>            |

Os valores dos SFR após o *Power-On Reset* - POR ou de um *RESET* são apresentados na Tabela 3.3.

Tabela 3.3 – Valores do SFRs após RESET [9].

| Registro | Tabela 3.3 – Valores do SFRs após RESET [9]. <b>Valor em Binário</b> |

|----------|----------------------------------------------------------------------|

| *ACC     | 00000000                                                             |

| *B       | 00000000                                                             |

| *PSW     | 00000000                                                             |

| SP       | 00000111                                                             |

| DPTR     |                                                                      |

| DPL      | 00000000                                                             |

| DPH      | 00000000                                                             |

| *P0      | 1111111                                                              |

| *P1      | 11111111                                                             |

| *P2      | 11111111                                                             |

| *P3      | 11111111                                                             |

| *IP      | 00000000                                                             |

| *IE      | 00000000                                                             |

| TMOD     | 00000000                                                             |

| *TCON    | 00000000                                                             |

| TH0      | 00000000                                                             |

| TL0      | 00000000                                                             |

| TH1      | 00000000                                                             |

| TL1      | 00000000                                                             |

| *SCON    | 00000000                                                             |

| SBUF     | Indeterminado                                                        |

| PCON     | HMOS 0XXXXXXX                                                        |

|          | CHMOS 0XXX0000                                                       |

### 3.2.3 Instruções

O microcontrolador 8051 possui diversas instruções, sendo cada uma representada por seu mnemônico e por um código em hexadecimal. A nomenclatura apresentada na Tabela 3.4 é adotada para exemplificar o conjunto das instruções:

Tabela 3.4 – Modo de endereçamento [9].

|         | Tabela 5.4 Wodo de endereçamento [7].         |

|---------|-----------------------------------------------|

| Rn      | pode ser registradores de R0 a R7             |

| Ri      | indica registrador R0 ou R1                   |

| @Ri     | endereçado pelo valor de R0 ou R1             |

| #Dado   | valor constante, numeral de 8 bits:           |

|         | #20H(hex), #30(dec), #01010101B(bin)          |

| #Dado16 | valor constante, numeral de 16 bits:          |

|         | #1FF2H(hex)                                   |

| Direto  | um endereço de memória RAM interna (8         |

|         | bits), registradores de status e controles, e |

|         | portas                                        |

| End16   | endereço de 16 bits para ROM (usado por       |

|         | LCALL e LJMP)                                 |

| End11   | endereço de 11 bits para ROM (usado por       |

|         | ACALL e AJMP)                                 |

| rel     | endereço relativo ou utilização de label      |

| bit     | variável da RAM interna, bits de I/O, bits de |

|         | status e controle                             |

A Tabela 3.5 contém os mnemônicos e as descrições de todos os 111 tipos de instruções.

Tabela 3.5 – Conjunto de instruções do 8051 [9].

| Operações Aritméticas |                                                 |

|-----------------------|-------------------------------------------------|

| Mnemônico             | Descrição                                       |

| ADD A,Rn              | Soma o conteúdo de Rn com ACC, o resultado      |

|                       | da soma é gravado no ACC.                       |

| ADD A, direto         | Soma o conteúdo da posição de memória           |

|                       | com ACC, o resultado é gravado no ACC.          |

| ADD A, @Ri            | Soma o conteúdo da posição de memória           |

|                       | indicado por Ri (R1 ou R0) com ACC, gravando    |

|                       | o resultado no ACC.                             |

| ADD A, # dado         | Soma o dado ao ACC. O resultado é gravado       |

|                       | no ACC.                                         |

| ADDC A, Rn            | Soma o conteúdo de Rn (R0 à R7) ao ACC,         |

|                       | e com a flag carry, o resultado é gravado       |

|                       | no ACC.                                         |

| ADDC A, direto        | Soma o conteúdo da posição de memória           |

|                       | com o ACC, e com flag carry, o resultado é      |

|                       | gravado no ACC.                                 |

| ADDC A, @Ri           | Soma o conteúdo da posição de memória           |

|                       | indicado por Ri (R1 ou R0) com o ACC, e         |

|                       | com a flag carry, o resultado é gravado no      |

|                       | ACC.                                            |

| ADDC A, # dado        | Soma o dado ao ACC, e a flag carry, o resultado |

|                       | é gravado no ACC.                               |

| SUBB A, Rn            | Subtrai do ACC, o conteúdo de Rn (R0 à          |

|                       | R7) e o 'vem um' (borrow), o resultado é        |

|                       | gravado no ACC.                                 |

| SUBB A, direto        | Subtrai do ACC. o conteúdo da posição de        |

|                       | memória e o 'vem um' (borrow), o resultado      |

|                       | é gravado no ACC                                |

| CIIDD A @D;        | Subtrai do ACC, o conteúdo da posição de                                                |

|--------------------|-----------------------------------------------------------------------------------------|

| SUBB A, @Ri        | memória indicado por Ri (R1 ou R0) e o                                                  |

|                    | vem um (se existir) o resultado é gravado                                               |

|                    | no ACC.                                                                                 |

| SUBB A, # dado     | Subtrai do ACC, o dado e o 'vem um' (se                                                 |

|                    | existir), o resultado é gravado no ACC.                                                 |

| INC A              | Soma 1 ao ACC.                                                                          |

| INC Rn             | Soma 1 ao conteúdo de Rn (R0 a R7).                                                     |

| INC direto         | Soma 1 ao conteúdo da posição de memória.                                               |

| INC @Ri            | Soma 1 ao conteúdo de memória indicado                                                  |

| PEG 4              | por Ri (R0 ou R1).                                                                      |

| DEC A              | Subtrai 1 do ACC.                                                                       |

| DEC Rn             | Subtrai 1 do conteúdo de Rn (R0 a R7).                                                  |

| DEC direto DEC @Ri | Subtrai 1 do conteúdo da posição de memória.                                            |

| DEC @RI            | Subtrai 1 do conteúdo da posição de memória indicado por Ri (R0 ou R1).                 |

| INC DPTR           | Soma 1 ao registrador DPTR.                                                             |

| MUL AB             | Multiplica o conteúdo do ACC pelo conteúdo                                              |

| MOL AD             | do registrador B. O resultado fica em B                                                 |

|                    | (MSB) e ACC (LSB)                                                                       |

| DIV AB             | Divide o conteúdo do ACC pelo conteúdo                                                  |

|                    | do registrador B. O resultado fica em A e o                                             |

|                    | resto em B.                                                                             |

| DA A               | Converte em BCD, o conteúdo do ACC.                                                     |

|                    | Operações Lógicas                                                                       |

| ANL A, Rn          | Grava no acumulador o resultado da operação                                             |

|                    | lógica AND entre o acumulador e                                                         |

| A 3 4 4 4          | registrador Rn                                                                          |

| ANL A, direto      | Grava no acumulador o resultado da operação                                             |

|                    | lógica AND entre o acumulador e conteúdo do endereço "direto"                           |

| ANL A, @Ri         | Grava no acumulador o resultado da operação                                             |

| mun, em            | lógica AND entre o acumulador e o                                                       |

|                    | conteúdo endereçado pelo registrador Ri                                                 |

| ANL A, #dado       | Grava no acumulador o resultado da operação                                             |

|                    | lógica AND entre o acumulador e o                                                       |

|                    | dado                                                                                    |

| ANL direto, A      | Grava no endereço "direto" o resultado da                                               |

|                    | operação lógica AND entre o endereço "direto"                                           |

| ANT dinete #dede   | e o acumulador                                                                          |

| ANL direto,#dado   | Grava no endereço "direto" o resultado da operação lógica AND entre o endereço "direto" |

|                    | e o dado                                                                                |

| ORL A, Rn          | Grava no acumulador o resultado da operação                                             |

| , <del></del>      | lógica OR entre o acumulador e registrador                                              |

|                    | Rn                                                                                      |

| ORL A, direto      | Grava no acumulador o resultado da operação                                             |

|                    | lógica OR entre o acumulador e conteúdo                                                 |

| ODY 4 071          | do endereço "direto                                                                     |

| ORL A, @Ri         | Grava no acumulador o resultado da operação                                             |

|                    | lógica OR entre o acumulador e o conteúdo endereçado pelo                               |

|                    | registrador Ri                                                                          |

| ORL A, #dado       | Grava no acumulador o resultado da operação                                             |

| Jill II, IIdadu    | lógica OR entre o acumulador e dado                                                     |

| ORL direto, A      | Grava no endereço "direto" o resultado da                                               |

| <u> </u>           | operação lógica OR entre o endereço "direto"                                            |

|                    | e o acumulador                                                                          |

| ORL direto,#dado   | Grava no endereço "direto" o resultado da                                               |

|                    |                                                                                         |

|                                         | operação lógica OR entre o endereço "direto" e o dado                                      |

|-----------------------------------------|--------------------------------------------------------------------------------------------|

| XRL A, Rn                               | Grava no acumulador o resultado da operação lógica XOR entre o acumulador e registrador Rn |

| XRL A, direto                           | Grava no acumulador o resultado da operação                                                |

| ARL A, uneto                            | lógica XOR entre o acumulador e                                                            |

|                                         | conteúdo do endereço "direto"                                                              |

| XRL A, @Ri                              | Grava no acumulador o resultado da operação                                                |

| 111211, 610                             | lógica XOR entre o                                                                         |

|                                         | acumulador e o conteúdo endereçado pelo                                                    |

|                                         | registrador Ri                                                                             |

| XRL A, #dado                            | Grava no acumulador o resultado da operação                                                |

| ,                                       | lógica XOR entre o acumulador e o                                                          |

|                                         | dado                                                                                       |

| XRL direto, A                           | Grava no endereço "direto" o resultado da                                                  |

|                                         | operação lógica XOR entre o endereço "direto"                                              |

|                                         | e o acumulador                                                                             |

| XRL direto,#dado                        | Grava no endereço "direto" o resultado da                                                  |

|                                         | operação lógica XOR entre o endereço "direto"                                              |

| CT D A                                  | e o dado                                                                                   |

| CDI A                                   | Zera o acumulador                                                                          |

| CPL A<br>RL A                           | Inverte todos os bits do acumulador                                                        |

| KL A                                    | Rotaciona todos os bits do acumulador para esquerda                                        |

| RLC A                                   | Rotaciona todos os bits do acumulador para                                                 |

|                                         | esquerda junto com a flag carry                                                            |

| RR A                                    | Rotaciona todos os bits do acumulador para                                                 |

|                                         | direita                                                                                    |

| RRC                                     | Rotaciona todos os bits do acumulador para                                                 |

|                                         | direita junto com a flag carry                                                             |

| SWAP A                                  | Troca os nibbles do acumulador (equivale a 4                                               |

|                                         | instruções RL A) <b>Transferência de Dados</b>                                             |

|                                         |                                                                                            |

| MOV A, Rn                               | Carrega o acumulador com o conteúdo do registrador Rn                                      |

| MOV A, direto                           | Carrega o acumulador com o conteúdo do                                                     |

| vio v n, uneto                          | endereço "direto" (endereços dos registradores                                             |

|                                         | internos)                                                                                  |

| MOV A, @Ri                              | Carrega o acumulador com o conteúdo endereçado                                             |

| <u> </u>                                | pelo registrador Ri                                                                        |

| MOV A, #dado                            | Carrega o acumulador com o dado                                                            |

| MOV Rn, A                               | Carrega o registrador Rn com o conteúdo                                                    |

|                                         | do acumulador                                                                              |

| MOV Rn, direto                          | Carrega o registrador Rn com o conteúdo                                                    |

| MOVD #3.3                               | do endereço "direto"                                                                       |

| MOV directs A                           | Carrega o registrador Rn com o dado                                                        |

| MOV direto, A                           | Carrega o endereço "direto" com o conteúdo do acumulador                                   |

| MOV direto, Rn                          | Carrega o endereço "direto" com o conteúdo                                                 |

| MO v un ciu, Kii                        | do registrador Rn                                                                          |

| MOV direto1,direto2                     | Carrega o endereço "direto1" com o conteúdo                                                |

| - · · · · · · · · · · · · · · · · · · · | endereço2 "direto2"                                                                        |

| MOV direto, @Ri                         | Carrega o endereço "direto" com o conteúdo                                                 |

|                                         | endereçado pelo registrador Ri                                                             |

| MOV direto, #dado                       |                                                                                            |

| MOV @Ri, A                              | Carrega o endereço "direto" com o dado                                                     |

|                                         | Carrega o registrador endereçado por Ri                                                    |

| MOV @Ri, direto                         |                                                                                            |

|                  | com o conteúdo do endereço "direto"                                               |

|------------------|-----------------------------------------------------------------------------------|

| MOV @Ri, dado    | Carrega o registrador endereçado por Ri                                           |

| 1110 ( C111) uuu | com o dado                                                                        |

| MOV DPTR,dado16  | Carrega o registrador DPTR com o dado                                             |

| ,                | de 16 bits                                                                        |

| MOVC A,@A+DPTR   | Carrega o acumulador com o conteúdo endereçado                                    |

|                  | pelo acumulador mais o registrador                                                |

|                  | DPTR                                                                              |

| MOVC A, @A+PC    | Carrega o acumulador com o conteúdo endereçado                                    |

|                  | pelo acumulador mais o registrador                                                |

| 7.502.22.1.0.24  | PC                                                                                |

| MOVX A, @Ri      | Carrega o acumulador com o conteúdo da                                            |

|                  | RAM externa endereçado pelo registrador<br>Ri                                     |

| MOVX A, @DPTR    | Carrega o acumulador com o conteúdo da                                            |

| MOVAA, WDFIK     | RAM externa endereçado pelo registrador                                           |

|                  | DPTR                                                                              |

| MOVX @Ri, A      | Carrega o registrador da RAM externa endereçado                                   |

|                  | pelo registrador de 8 bits Ri, com                                                |

|                  | o conteúdo do acumulador                                                          |

| MOVX @DPTR, A    | Carrega o registrador da RAM externa endereçado                                   |

| ĺ                | pelo registrador de 16 bits DPTR,                                                 |

|                  | com o conteúdo do acumulador                                                      |

| PUSH direto      | Incrementa o registrador SP e salva na pilha                                      |

|                  | o conteúdo do endereço "direto"                                                   |

| POP direto       | Grava na memória o conteúdo da pilha e                                            |

|                  | decrementa o registrador SP                                                       |

| XCH A, Rn        | Troca os dados do acumulador com o registrador                                    |

| VCII A dinata    | Rn                                                                                |

| XCH A, direto    | Troca os dados do acumulador com o endereço "direto"                              |

| XCH A, @Ri       | troca os dados do acumulador com o registrador                                    |

| ACII A, @ KI     | endereçado por Rn                                                                 |

| XCHD A, @Ri      | Troca os nibbles menos significativos do                                          |

|                  | acumulador com o registrador endereçado                                           |

|                  | por Ri                                                                            |

|                  | Variáveis Booleanas                                                               |

| CLR C            | Grava 0 no flag carry                                                             |

| CLR Bit          | Grava 0 no bit endereçável (bit de pino ou                                        |

|                  | bit de registradores)                                                             |

| SETB C           | grava 1 no flag carry                                                             |

| SETB Bit         | Grava 1 no bit endereçável (bit de pino ou                                        |

| CDV C            | bit de registradores)                                                             |

| CPL C            | Complementa o flag carry                                                          |

| CPL Bit          | Complementa o bit endereçável (bit de pino                                        |

| ANI C D:4        | ou bit de registradores)                                                          |

| ANL C, Bit       | Grava no flag carry o resultado da operação lógica AND entre o flag carry e o bit |

|                  | endereçável (bit de pino ou bit de registradores)                                 |

| ANL C, \Bit      | Grava no flag carry o resultado da operação                                       |

| THILL C, IDIL    | lógica AND entre o flag carry e o complemento                                     |

|                  | do bit endereçável (bit de pino ou                                                |

|                  | bit de registradores).                                                            |

| ORL C, Bit       | Grava no flag carry o resultado da operação                                       |

|                  | lógica OR entre o flag carry e o bit                                              |

|                  | endereçável (bit de pino ou bit de registradores)                                 |

| ORL C, \Bit      | Grava no flag carry o resultado da operação                                       |

|                  | lógica OR entre o flag carry e o complemento                                      |

| 1                | do bit endereçável (bit de pino ou                                                |

|                                                      | bit de registradores)                                              |

|------------------------------------------------------|--------------------------------------------------------------------|

| MOV C, Bit                                           | Grava no flag carry o conteúdo do bit                              |

|                                                      | endereçável (bit de pino ou bit de registradores)                  |

| MOV Bit, C                                           | Grava no bit endereçável (bit de pino ou bit                       |

| ,                                                    | de registradores) o conteúdo do flag carry                         |

|                                                      | Fluxo de Execução                                                  |

| ACALL End 11 Chamada curta de sub-rotina (11 bits, 2 |                                                                    |

|                                                      | kbytes da posição atual)                                           |

| LCALL End 16                                         | Chamada longa de sub-rotina (16 bits , qualquer                    |

|                                                      | posição da EPROM )                                                 |

| RET                                                  | Retorno de sub-rotina                                              |

| RETI                                                 | Retorno de sub-rotina de interrupção                               |

| AJMP End 11                                          | Desvio curto para endereço de 11 bits, 2                           |

|                                                      | kbytes da posição atual                                            |

| LJMP End 16                                          | Desvio longo para endereço de 16 bits,                             |

|                                                      | qualquer posição da EPROM                                          |

| SJMP rel                                             | Desvio relativo curto                                              |