# UNIVERSIDADE FEDERAL DE ITAJUBÁ PROGRAMA DE PÓS-GRADUAÇÃO EM ENGENHARIA ELÉTRICA

Modulador por Intervalo de Pulsos (PIM) aplicado à rede de sensores do corpo humano

Décio Rennó de Mendonça Faria

# UNIVERSIDADE FEDERAL DE ITAJUBÁ PROGRAMA DE PÓS-GRADUAÇÃO EM ENGENHARIA ELÉTRICA

## Décio Rennó de Mendonça Faria

# Modulador por Intervalo de Pulsos (PIM) aplicado à rede de sensores do corpo humano

Dissertação submetida ao Programa de Pós-Graduação em Engenharia Elétrica como parte dos requisitos para obtenção do título de Mestre em Ciências em Engenharia Elétrica.

Área de concentração: Microeletrônica

**Orientador:** Prof. Dr. Robson Luiz Moreno **Coorientador:** Prof. Dr. Tales Cleber Pimenta

Maio de 2016 Itajubá

# UNIVERSIDADE FEDERAL DE ITAJUBÁ PROGRAMA DE PÓS-GRADUAÇÃO EM ENGENHARIA ELÉTRICA

# Décio Rennó de Mendonça Faria

# Modulador por Intervalo de Pulsos (PIM) aplicado à rede de sensores do corpo humano

**Dissertação** aprovada por banca examinadora em 03 de maio de 2016, conferindo ao autor o título **de Mestre em Ciências em Engenharia Elétrica.**

### Banca examinadora:

Prof. Dr. Evaldo Renó Faria Cintra Prof. Dr. Paulo Cesar Crepaldi Prof. Dr. Robson Luiz Moreno Prof. Dr. Tales Cleber Pimenta

Orientador: Prof. Dr. Robson Luiz Moreno Coorientador: Prof. Dr. Tales Cleber Pimenta

> Itajubá 2016

# Agradecimentos

Aos professores do curso, especialmente ao Professor Dr. Tales Cleber Pimenta pela grande atenção dada à mim e a todos que o procuram, pelas orientações e otimismo com que encara os problemas, ao Professor Dr. Robson Luiz Moreno, pela contribuição com novas ideias e orientação deste trabalho, ao Prof. Dr. Paulo César Crepaldi pelos valorosos ensinamentos passados na graduação e pós graduação, à equipe da UNIFEI, e a todos os colegas e amigos que de forma direta ou indireta contribuíram com este trabalho.

#### Resumo

Com o avanço da eletrônica e dos meios de comunicação, o uso de dispositivos eletrônicos de monitoramento de funções biométricas vem crescendo. Os dispositivos implantados demandam pequenas dimensões e comunicação sem fios. Estas características limitam o consumo de energia e assim o dispositivo implantado deve executar o menor processamento possível no sinal e a comunicação deve ser sem fio.

Este trabalho apresenta um conversor tensão frequência (VFC) e um conversor de sinais VFC em um sinal de modulação por intervalo de pulsos (PIM), em tecnologia IBM CMOS de 130nm. Esse sistema de modulação diminui o consumo de energia dos sistemas implantados através da redução do tempo em que o transmissor permanece ligado.

Os resultados dos testes em simulador foram bastante satisfatórios confirmando a viabilidade da implementação e utilização de um conversor que transforma os sinais de um VFC em sinais de modulação PIM.

### **Abstract**

With the advancement of electronics and system communications, the interest in body monitoring electronic devices is growing. The implanted devices require small dimensions and wireless communication. These features constraint energy consumption and less processing and wireless communication is desirable.

This work presents a voltage to frequency converter (VFC) and a circuit that converts the VFC signal to pulse interval modulation (PIM) in 130nm IBM CMOS technology. This modulation system reduces the total energy used by shorting the time that the transmitter is turned on

The results were very satisfactory, confirming the viability of implementation and use of a converter to transform VFCs signals into PIM modulation signal.

Keywords: Wireless Sensor Networks, Voltage to frequency converter, PIM modulation.

# Índice de Figuras

# Capitulo 1 – Introdução

| Figura 1.1 – Exemplo de rede de sensores WSN                                      | 14 |

|-----------------------------------------------------------------------------------|----|

| Figura 1.2 – Exemplo de utilização de uma rede de sensores do corpo humano        | 16 |

| Figura 1.3 – Sensor subcutâneo alimentado por enlace de RF                        | 17 |

| Figura 1.4 – Saída típica de um conversor tensão frequência                       | 18 |

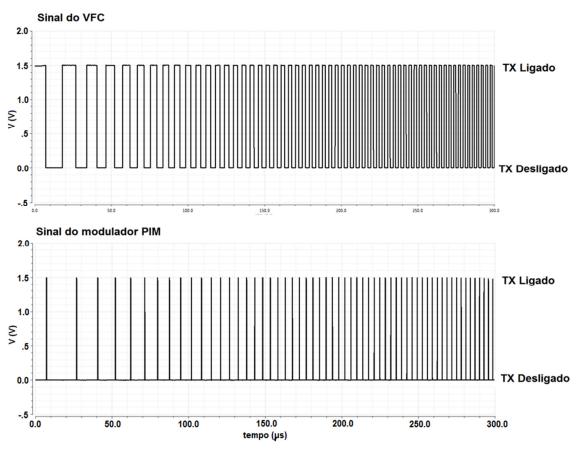

| Figura 1.5 – Comparação entre um sinal transmitido pelo VFC e modulador PIM       | 19 |

| Capitulo 2 – Fundamentação teórica                                                |    |

| Figura 2.1 – Informação transmitida por um VFC                                    | 21 |

| Figura 2.2 – Comparações entre os sinais de um ADC e um VFC                       | 22 |

| Figura 2.3 – Circuito VFC tipo multivibrador                                      | 23 |

| Figura 2.4 – Circuito VFC tipo carga balanceada                                   | 24 |

| Figura 2.5 – Tensão sobre o capacitor C <sub>ent</sub> durante a carga e descarga | 24 |

| Figura 2.6 – Função de transferência e a determinação de FS                       | 26 |

| Figura 2.7 – Erro de offset e erro de ganho de um VFC                             | 27 |

| Figura 2.8 – Ilustração do erro de linearidade                                    | 28 |

| Figura 2.9 – Informação transmitida em um sinal PIM                               | 30 |

| Figura 2.10 – Exemplo de sinal modulado por chaveamento de portadora              | 30 |

| Figura 2.11 – Pulso do modulador PIM e um sinal de 200KHz de um VFC               | 31 |

| Figura 2.12 – Pulso do modulador PIM e um sinal de 800KHz de um VFC               | 32 |

| Figura 2.13 – Uso da energia do modulador PIM comparado ao VFC                    | 33 |

| Capitulo 3 – O circuito VFC                                                       |    |

| Figura 3.1 – Diagrama em blocos do VFC com modulador PIM                          | 34 |

| Figura 3.2 – Esquema completo do conversor VIC                                    | 35 |

| Figura 3.3 – Representação simplificada do conversor VIC                          | 36 |

| Figura 3.4 – Layout do conversor tensão corrente VIC                              | 37 |

| Figura 3.5 – Circuito de carga e descarga                                         | 38 |

| Figura 3.6 – Representação simplificada do circuito de carga e descarga           | 39 |

| Figura 3.7 – Layout do circuito de carga e descarga                               | 39 |

| Figura 3.8 – Circuito controlador de janela de tensão VWC                         | 40 |

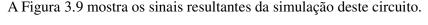

| Figura 3.9 – Sinais de saída do circuito comparador de janela de tensão           | 41 |

| Figura 3.10 – Modelo simplificado do circuito controlador de janela de tensão     | 42 |

| Figura 3.11 – Layout do circuito controlador de janela de tensão VWC              | 42 |

| Figura 3.12 – Esquema e layout da porta inversora                                 | 43 |

| Figura 3.13 – Esquema e layout da porta Não E                                     | 44 |

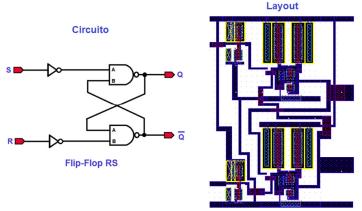

| Figura 3.14 – Esquema do Flip Flop RS                                             | 45 |

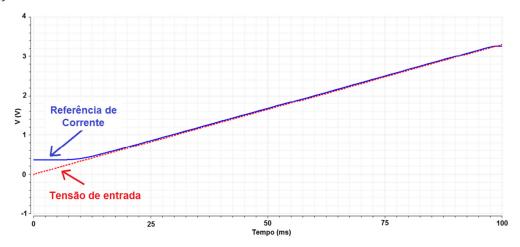

| Figura 3.15 – Corrente de saída e tensão de entrada do VIC                        | 45 |

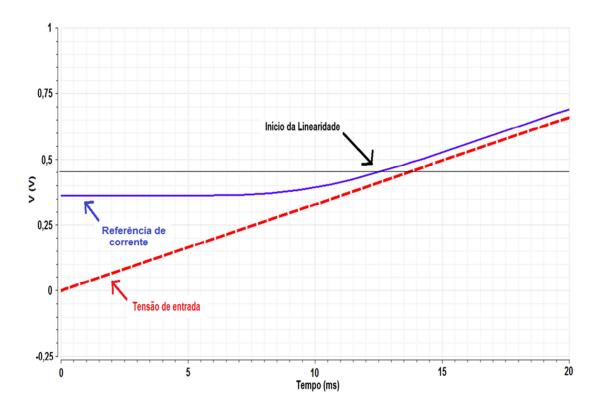

| Figura 3.16 – Linearidade do conversor VIC para tensões de entrada baixas         | 46 |

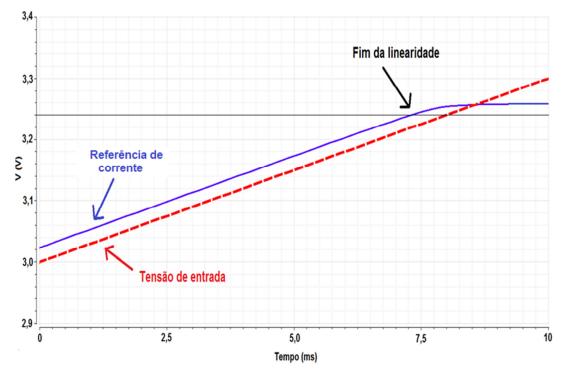

| Figura 3.17 – Linearidade do conversor VIC para tensões de entrada altas          | 47 |

| Figura 3.18 – Tensão no capacitor C1 para 0,5 volts na entrada do VFC       | 48 |  |  |  |  |

|-----------------------------------------------------------------------------|----|--|--|--|--|

| Figura 3.19 – Tensão no capacitor C1 para 3,24 volts na entrada do VFC      | 48 |  |  |  |  |

| Figura 3.20 – Gráfico da frequência em função da tensão de entrada          | 49 |  |  |  |  |

| Figura 3.21 – Frequência de saída do VFC em função da tensão de alimentação | 54 |  |  |  |  |

| Capítulo 4 – O modulador PIM                                                |    |  |  |  |  |

| Figura 4.1 – Esquema completo do modulador PIM                              | 56 |  |  |  |  |

| Figura 4.2 – Layout do circuito modulador PIM implementado                  | 57 |  |  |  |  |

| Figura 4.3 – Esquema simplificado do modulador PIM                          |    |  |  |  |  |

| Figura 4.4 – Tensão sobre o transistor T1                                   |    |  |  |  |  |

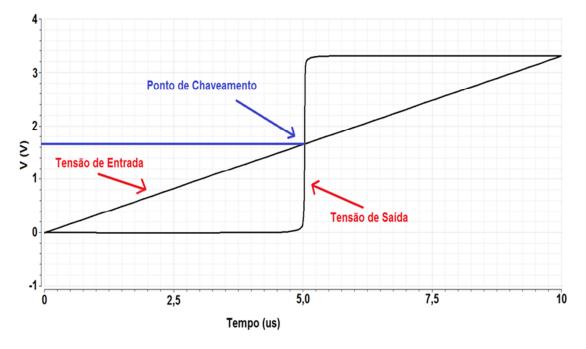

| Figura 4.5 – Teste do ponto de chaveamento dos inversores                   |    |  |  |  |  |

| Figura 4.6 – Ponto de chaveamento dos inversores determinado por RC         | 60 |  |  |  |  |

| Figura 4.7 – Tensões no modulador PIM com alimentação de 1,5V               |    |  |  |  |  |

| Capítulo 5 – Análise do VFC com Modulador PIM                               |    |  |  |  |  |

| Figura 5.1 – Sinal de saída do circuito VFC-PIM com 1,5V de entrada         | 63 |  |  |  |  |

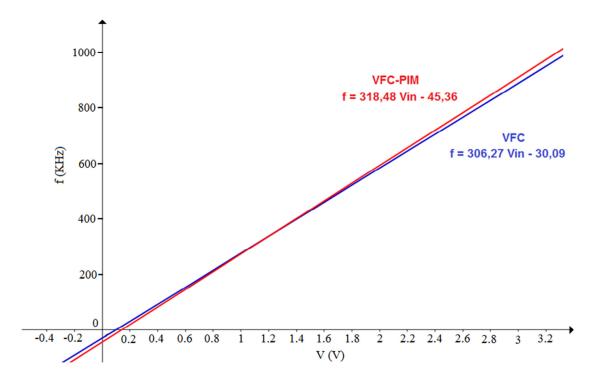

| Figura 5.2 – Retas obtidas pelos valores de saída do VFC e VFC-PIM          | 64 |  |  |  |  |

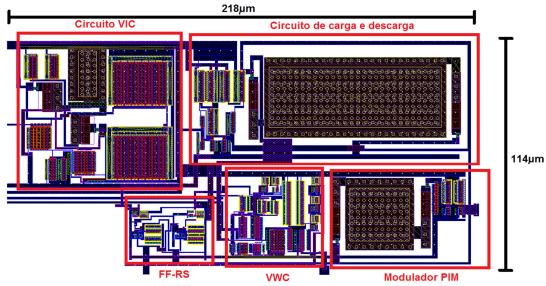

| Figura 5.3 – Layout completo do VFC com modulador PIM                       | 65 |  |  |  |  |

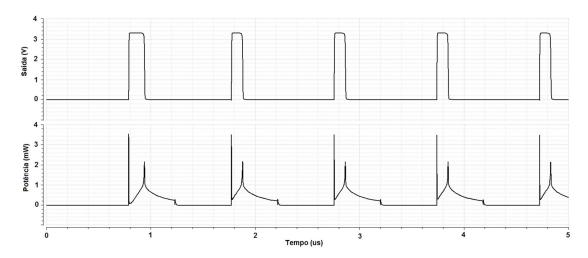

| Figura 5.4 – Consumo de corrente do circuito VFC-PIM                        | 65 |  |  |  |  |

| Figura 5.5 – Potência utilizada somente pelo conversor VFC-PIM              | 66 |  |  |  |  |

# Sumário

| CAPITULO 1 - INTRODUÇÃO                                         | 14 |

|-----------------------------------------------------------------|----|

| 1.1 CONSIDERAÇÕES INICIAIS                                      | 14 |

| 1.2 A REDE DE SENSORES DE CORPO HUMANO SEM FIO                  | 15 |

| 1.3 SENSORES IMPLANTADOS                                        | 17 |

| 1.4 JUSTIFICATIVA                                               |    |

| 1.5 OBJETIVOS DESTE TRABALHO                                    |    |

| 1.6 ESTRUTURA DO TRABALHO                                       |    |

| CAPÍTULO 2 - FUNDAMENTAÇÃO TEÓRICA                              |    |

| 2.1 CONVERSORES TENSÃO FREQUÊNCIA (VFC)                         |    |

| 2.1.1 VFC multivibrador                                         |    |

| 2.1.1 VFC mutiviorador                                          |    |

| 2.2 PARÂMETROS QUE AVALIAM UM VFC                               |    |

| 2.2.1 Níveis máximos e mínimos de sinal na entrada              |    |

| 2.2.2 Níveis máximos e mínimos de sinal na saída                |    |

| 2.2.3 Largura de faixa do sinal de saída                        |    |

| 2.2.4 Sensibilidade (ganho)                                     |    |

| 2.2.5 Erro de ganho                                             |    |

| 2.2.6 Erro de desvio de ajuste                                  |    |

| 2.2.7 Erro relativo                                             |    |

| 2.2.8 Erro de linearidade                                       |    |

| 2.2.9 Erro de linearidade provocado por temperatura             |    |

| 2.2.10 Razão de rejeição de variação da fonte de alimentação    |    |

| 2.3 MODULADORES POR INTERVALO DE PULSO                          |    |

| 2.4 CONSIDERAÇÕES TEÓRICAS SOBRE ESTE TRABALHO                  |    |

| CAPÍTULO 3 – O CIRCUITO VFC                                     |    |

| 3.1 DIAGRAMA GERAL DO VFC                                       | 34 |

| 3.2 O CONVERSOR TENSÃO CORRENTE                                 | 35 |

| 3.3 O CIRCUITO DE CARGA E DESCARGA                              | 37 |

| 3.4 O CIRCUITO DE CONTROLE                                      | 40 |

| 3.5 CIRCUITOS AUXILIARES                                        | 43 |

| 3.5.1 A porta inversora                                         | 43 |

| 3.5.2 A porta Não-E                                             |    |

| 3.5.3 O flip flop RS                                            | 45 |

| 3.6 RESULTADOS DOS TESTES E IMPLEMENTAÇÃO                       | 45 |

| 3.6.1 Linearidade do conversor VIC                              |    |

| 3.6.2 Curva de carga e descarga do capacitor                    |    |

| 3.6.3 Relação tensão de entrada versus frequência de saída      |    |

| 3.6.4 Erro de linearidade                                       |    |

| 3.6.5 Valores máximos e mínimos de entrada e saída              |    |

| 3.6.6 Variação da frequência em função da temperatura           |    |

| 3.6.7 Proporção de rejeição da variação da fonte de alimentação |    |

| CAPÍTULO 4 - O MODULADOR PIM                  | 56 |

|-----------------------------------------------|----|

| 4.1 – Descrição do circuito                   | 56 |

| 4.2 – Tempo do pulso                          | 59 |

| 4.3 – Análise da variação da fonte            | 61 |

| 4.4 – Análise de variação da temperatura      | 62 |

| CAPÍTULO 5 – ANÁLISE DO VFC COM MODULADOR PIM |    |

| 5.1 – Sinal de saída                          | 63 |

| 5.2 – Equação da reta do VFC-PIM              | 64 |

| 5.3 – Layout completo                         | 65 |

| 5.4 – Consumo de energia                      | 65 |

| 5.5 – Conclusão                               |    |

| 5.6 – Recomendação para trabalhos futuros     | 67 |

| LISTA DE REFERÊNCIAS                          | 68 |

### Lista de Abreviaturas

**ADC** – Conversor analógico para digital, circuito que através de um processo de quantização transforma um sinal analógico em um conjunto de bits.

**BSN** – Body Sensor Network, também chamada de WBAN, é uma rede de sensores do corpo humano definida pelo padrão IEEE 802.15.6.

Bluetooth – Rede de uso pessoal de curto alcance definida pelo padrão IEEE 802.15.1.

**Fotodetector** – Dispositivo semicondutor utilizado para transformar intensidade de luz em sinais elétricos.

**Foundry** – Local onde são fabricados os circuitos integrados.

**ISM** – Indutrial, Scientific and Medical band. Faixas de frequências que podem ser utilizadas para qualquer propósito sem a necessidade de licenciamento.

**LED** – Light Emitting Diode, dispositivo semicondutor utilizado para emitir luz.

**MIM Capacitor** – Metal to Metal Capacitor. Capacitor construído com duas camadas de metal isoladas por um fino dielétrico.

**Motes** - Dispositivos WSN na maioria das vezes de baixo consumo, com microcontrolador, sistema embarcado e sensores destinados à coleta e envio de dados.

**NMOS** – Transistor MOSFET com canal formado em um cristal dopado com impurezas trivalente (substrato P).

**NWELL** – Região dopada com impurezas pentavalentes utilizada como base para fabricação de transistores Mosfet tipo P em substrato tipo P.

**OOK** – On Off Keying – Sistema de modulação digital onde os bits 0's e 1's são representados pela presença ou ausência da portadora.

**OTA** – Operational Transcondutance Amplifier. Amplificador de corrente controlado por tensão que utiliza par diferencial.

**PIM** – Pulso interval modulation, tipo de modulação digital de sinal que transmite a informação pela diferença de tempo entre pulsos.

**Pino de I/O** – Terminal de uma placa ou circuito integrado que permite o envio ou a recepção de sinais analógicos ou digitais.

**PMOS** – Transistor MOSFET com canal formado em um cristal dopado com impurezas pentavalentes (substrato N).

**PPM** – Partes por milhão, referencial utilizado para referenciar proporções.

**QOS** - Quality of Service, medida da capacidade de uma rede de transmitir com sucesso uma informação.

Rede 802.15.4 – Padrão de rede WSN de baixo consumo e baixo custo.

Rede 802.11 b/g/n – Padrão de rede utilizado nas redes sem fio domésticas.

**Relação W/L** – Proporção entre a largura do transistor Mosfet com relação ao comprimento do canal do mesmo.

**VCO** – Oscilador controlado por tensão, circuito que produz um sinal com frequência controlada pela tensão de entrada Não exige linearidade com o sinal de controle.

**VFC** – Conversor de tensão para frequência, converte um sinal analógico em um sinal com frequência proporcional à tensão de entrada.

**VFC-PIM** – Conversor de tensão para intervalo de pulsos formado por um VFC e um modulador PIM.

**VNCAP** – Vertical Natural Capacitor. Capacitor construído por ligações metálicas em uma mesma camada na forma interdigital.

**WPAN** – Wireless Personal Area Network, rede de curto alcance, atingindo algumas dezenas de metros, utilizada como meio de comunicação entre dispositivos, ligação de periféricos e transmissão de dados.

WSN – Wireless Sensor Network, rede de sensores com comunicação sem fio utilizada para monitoramento de condições físicas ou ambientais como temperatura, pressão, humidade, batimento cardíaco, etc.

**WBAN** - Wireless Body Area Network, rede curto alcance formada por dispositivos ligados ao corpo humano, definida pelo padrão IEEE 802.15.6.

**WBSN** – Wireless Body Sensor Network, rede de biosensores com transmissão sem fio com a finalidade de monitoramento do corpo humano.

# Capitulo 1 - Introdução

### 1.1 Considerações iniciais

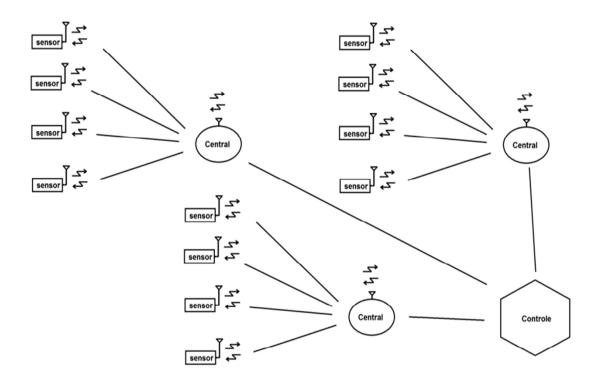

As redes de sensores sem fio - WSN (Wireless Sensor Network) têm importantes aplicações nas áreas de segurança, vigilância, militar, saúde e ambiental [1]. Basicamente é composta por sensores equipados com dispositivos de comunicação que possibilitam a troca de informações com uma central ou com outros sensores como ilustra a Figura 1.1.

Figura 1.1 – Exemplo de rede de sensores WSN.

O projeto desses sensores depende de sua aplicação e varia com o tipo de ambiente a ser utilizado, das fontes de energia disponíveis e do alcance, entre outros. A maioria dos sensores utilizados em redes WSN trabalha com limitação de memória, de bateria, de capacidade de processamento e de comunicação. Desta forma, um sensor WSN normalmente monitora somente uma pequena porção do ambiente.

Uma rede de sensores sem fio geralmente consiste de dezenas ou até milhares de sensores espalhados em um espaço físico com uma ou mais estações bases. Estes sensores, além da coleta dos dados, podem fazer um pré-processamento da informação antes do envio à central.

As redes de sensores sem fio possuem algumas características distintas [2] como:

- Tolerância à erros: Um sensor de uma rede de sensores sem fio pode não ter energia suficiente para enviar a informação naquele momento, ou até mesmo estar danificado. A rede de sensores deve prever isto, e se for o caso informar ou registrar esse evento.

- Mudanças de tamanho: A rede deve estar preparada para um possível aumento ou diminuição do número de sensores.

- Tempo de vida: A manutenção dos sensores, seja pela troca da bateria ou por outro motivo qualquer, deve ser evitada. Por estar na maioria das vezes em grande número e espalhados, uma eventual manutenção nos sensores pode se tornar um grande problema, assim, a duração dos sistemas de alimentação deve ser cuidadosamente analisada.

#### Alguns sistemas exigem:

- Programabilidade: Para permitir flexibilidade, as redes WSN devem permitir alterações como inclusão de novos tipos de dispositivos, mudança ou reprogramação dos sensores e outros.

- Segurança: O controle de acesso, a integridade da mensagem, a confidencialidade dos dados e sistemas que evitam ataques propositais são necessários em alguns sistemas.

- **Disponibilidade:** Sensores de baixo custo e pouca manutenção são necessários devido ao número de dispositivos utilizados.

## 1.2 A rede de sensores de corpo humano sem fio

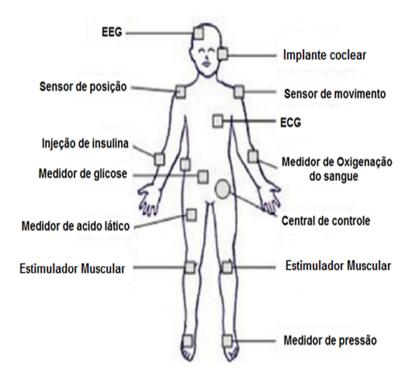

Uma rede de sensores de corpo humano sem fio WBSN (Wireless Body Sensor Network) é formada por biosensores capazes de processar e enviar via rádio a informação coletada [3,4]. Além dos sensores, a concepção desta rede permite a utilização de dispositivos que injetam medicamentos como insulina, e provocam estímulos elétricos [5]. A Figura 1.2 ilustra algumas aplicações desta tecnologia no corpo humano.

Figura 1.2 – Exemplo de utilização de uma rede de sensores do corpo humano.

Fonte: Zion Computer Hardware and Networking Institute [5].

- O sensor eletroencefalograma (EEG) permite analisar a atividade elétrica cerebral espontânea [6,7].

- O implante coclear é um equipamento eletrônico computadorizado que substitui o ouvido de pessoa que têm surdez total ou quase total [8,9].

- Os sensores de posicionamento corporal são utilizados para diagnóstico de distúrbios do sono [10].

- A eletromiografia monitora a atividade elétrica muscular [11,12].

- O eletrocardiograma (ECG) ajuda no diagnostico de doenças cardiovasculares [13,14].

- O medidor de oxigenação do sangue mede indiretamente os níveis de saturação de oxigênio (S<sub>P</sub>O<sub>2</sub>) e pode ser utilizado para calcular a pressão e o ritmo cardíaco [15,16].

- Os estimuladores ativam nervos periféricos e nervos internos [17].

- O medidor de ácido lático mede a fadiga muscular [18,19,20].

- O medidor de glicose associado à bomba de insulina possibilita um controle inteligente dos níveis de glicemia no sangue [21,22,23].

### 1.3 Sensores implantados

Os recentes avanços obtidos na área de desenvolvimento de circuitos integrados de baixíssimo consumo (ultra-low power) estão permitindo a criação de uma nova geração de dispositivos implantados ou fixados ao corpo com o objetivo de monitoramento da saúde do organismo. Um dos maiores desafios enfrentados pelos projetistas que trabalham nessa área é a criação de dispositivos de baixa manutenção, baixo custo e com características que permitam serem implantados ou fixados ao corpo sem provocar desconforto ou procedimentos cirúrgicos complicados. A utilização de baterias pequenas limita o tempo de vida dos sensores e exige a sua substituição periódica. Por outro lado, baterias maiores causam desconforto sendo muitas vezes um limitador do uso desta tecnologia por não permitirem a implantação do sensor. Neste sentido, a utilização de baterias implantadas ou fixadas ao corpo torna-se altamente indesejável [24].

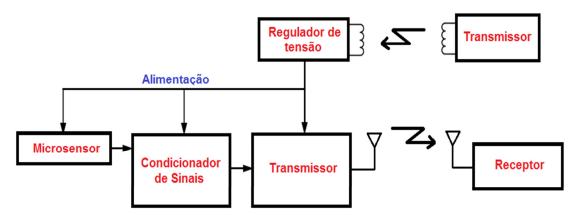

Como fonte de energia alternativa, é possível utilizar a energia do ambiente externo captada, e armazenada ou não, no próprio dispositivo implantado. Como exemplo, têm-se as fontes com gerador termoelétrico e as fontes acopladas via enlace de RF subcutâneo como ilustrado na Figura 1.3 [25].

Figura 1.3 – Sensor subcutâneo alimentado por enlace de RF.

Independente da fonte de energia utilizada, a não utilização de baterias limita drasticamente a quantidade de energia disponível e impõe limites máximos de consumo aos dispositivos. Com o objetivo de otimizar a utilização da energia, técnicas de operação em sub-limiar (sub-thresold) [26,27] e circuitos quasi-digitais, que transmitem um sinal quadrado com informação analógica sem codificação podem ser utilizados.

No enlace de comunicação, os circuitos quase-digitais, transmitem informação em frequência, fase ou ciclo de trabalho, disponibilizando assim a informação com a simplicidade

dos dispositivos de sinal analógico e a precisão e imunidade à ruídos típicos dos circuito digitais [28], dispensando a necessidade de processamento de sinal no circuito implantado, pois a conversão tensão frequência realizada por esses circuitos pode ser feita com circuitos discretos.

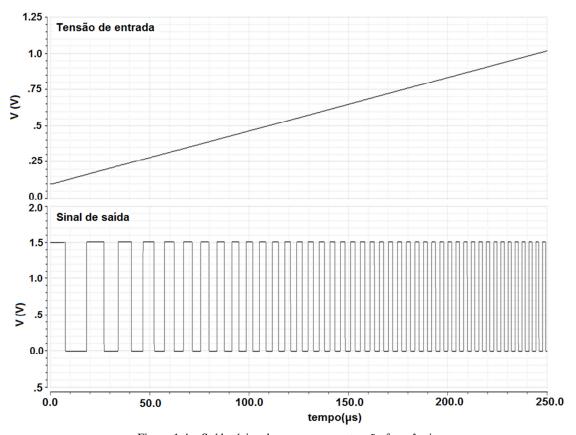

Um exemplo de circuito quase-digital é o circuito conversor tensão frequência VFC (voltage to frequency converter). Este circuito mantém o transmissor 50% do tempo ligado durante uma transmissão, como pode ser visto na Figura 1.4.

Como se pode observar, a medida que a tensão de controle aumenta, a frequência do sinal de saída se eleva. Porém o ciclo de trabalho mantém-se em 50%.

Figura 1.4 – Saída típica de um conversor tensão frequência.

### 1.4 Justificativa

Ao se dispensar o uso de processamento no dispositivo a ser implantado, os circuitos quase-digitais reduzem consideravelmente o consumo de energia [28]. Dependendo do sinal a ser transmitido, este consumo pode ser ainda menor se a informação transmitida puder ser enviada de tempos em tempos, como é o caso do nível de glicemia, temperatura e outros.

Apesar de toda redução de consumo obtida com o uso dessas técnicas, estes circuitos ainda podem apresentar consumo elevado se considerado à energia disponível.

Este trabalho descreve um circuito concebido para ser utilizado como interface entre os conversores tensão frequência e o transmissor. Através da redução da largura do pulso, este circuito transforma o sinal originalmente quadrado proveniente de um conversor tensão frequência VFC (Voltage to Frequency Converter), em um sinal modulado por intervalo de pulso PIM (Pulse Interval Modulation). A redução no consumo ocorre devido ao fato que, na modulação PIM o transmissor permanece ligado por um período muito menor de tempo se comparado à um sinal modulado por VFC convencional.

A redução do tempo do pulso não altera a frequência deste sinal, assim sendo não prejudica o envio da informação, pois o tempo entre os pulsos corresponde à informação desejada. A Figura 1.5 ilustra a diferença entre um sinal transmitido por um VFC e o mesmo sinal sendo transmitido por um modulador PIM.

Figura 1.5 – Comparação entre um sinal transmitido pelo VFC e modulador PIM.

### 1.5 Objetivos deste trabalho

O principal objetivo deste trabalho é o desenvolvimento de um circuito modulador PIM, este pode ser utilizado em conjunto com conversores VFC. O projeto do modulador PIM proposto está dividido em três partes:

- Desenvolvimento de um conversor VFC com tecnologia CMOS 130nm para testes e análise de consumo.

- 2) Desenvolvimento do conversor PIM.

- 3) Avaliação da precisão e consumo do modulador.

### 1.6 Estrutura do trabalho

O presente trabalho está dividido em 5 capítulos. Este primeiro capítulo descreve de uma forma geral a tecnologia atual e os objetivos deste trabalho, servindo como introdução as questões que serão discutidas nos capítulos seguintes.

O segundo capítulo fornece a base teórica que fundamenta e permite uma maior compreensão das razões e técnicas utilizadas neste trabalho.

O terceiro capítulo consiste na descrição detalhada do circuito VFC desenvolvido bem como os pontos críticos e as soluções encontradas em cada etapa do projeto.

O quarto capítulo descreve a concepção e o desenvolvimento do conversor PIM, bem como analisa os resultados obtidos.

O quinto capítulo analisa os resultados do conjunto VFC/Modulador PIM e apresenta as conclusões e sugestões para futuros trabalhos.

# Capítulo 2 - Fundamentação teórica

### 2.1 Conversores tensão frequência (VFC)

Um conversor tensão para frequência - VFC (Voltage to Frequency Converter) é um oscilador de primeira ordem controlado por um sinal analógico de tensão similar ao oscilador controlado por tensão - VCO (Voltage Controlled Oscillator), porém com maior exigência da linearidade entre tensão-frequência, algo normalmente não exigido para um VCO [29,30]. Pode-se representar matematicamente sua saída em função da entrada por:

$$f_o = k.V_{in} \tag{2.1}$$

onde:

$f_o =$ Frequência de saída do VFC,

k =Constante de proporcionalidade,

$V_{in}$  = Tensão de entrada.

Além desta exigência, um VFC tipicamente necessita de alta precisão no fator de escala, e grande estabilidade com relação às variações de temperatura e de tensão de alimentação.

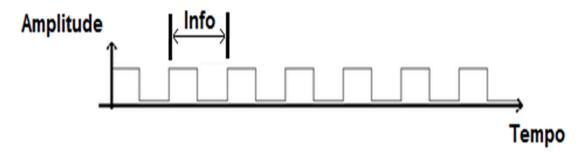

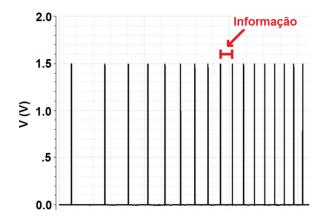

Pelo fato de sua saída resultar em um sinal quadrado, os VFCs são denominados de circuitos quase-digitais. A Figura 2.1 mostra um sinal VFC e a informação transmitida.

Figura 2.1 – Informação transmitida por um VFC.

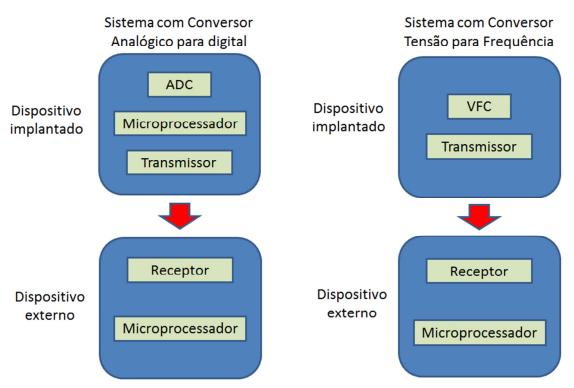

A recuperação da informação analógica proveniente de um VFC consiste basicamente em medir o tempo entre um pulso e outro. Como a frequência do sinal é linearmente proporcional ao sinal analógico, o tempo medido por um contador corresponde à informação analógica transmitida. O contador de tempo pode ser implementado com componentes eletrônicos discretos, microcontroladores, FPGA, CPLD e outros [31,32]. A grande vantagem desse processo em circuitos implantados está no fato do processamento do sinal ser realizado fora do corpo, e assim, reduz-se o consumo de energia do circuito implantado, pois os circuitos necessários ao processamento não ficam embarcados, como ilustra a Figura 2.2.

Figura 2.2 – Comparações entre os sinais de um ADC e um VFC.

Existem basicamente dois tipos de VFC, o multivibrador e o VFC de carga balanceada. O circuito VFC multivibrador é simples, consome pouco e possui um sinal de saída quadrado muito adequado à transmissão. O circuito VFC de carga balanceada é mais preciso e trabalha com transientes de tensão negativos, porém possui um consumo maior e sua saída é um trem de pulso e não um sinal quadrado [32,33].

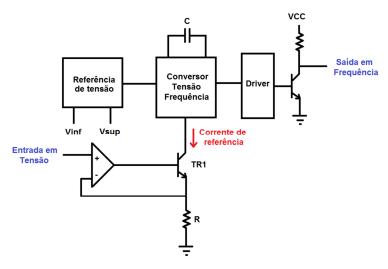

### 2.1.1 VFC multivibrador

O VFC tipo multivibrador converte a tensão de entrada em um valor de corrente que determina o tempo de carga e descarga de um capacitor. Um circuito de controle com duas tensões de referência determina se o circuito está carregando ou descarregando. As tensões de referência estabelecem os valores máximos e mínimos de tensão no capacitor.

O estado atual do circuito (carregando ou descarregando) é fornecido à saída, sendo este um sinal digital com frequência proporcional à tensão de entrada. A Figura 2.3 mostra um circuito utilizado como VFC multivibrador [34].

Figura 2.3 – Circuito VFC tipo multivibrador.

Neste circuito, o sinal de entrada é aplicado ao amplificador operacional configurado como buffer que controla o valor da corrente do transistor TR1. Esta corrente é utilizada pelo circuito conversor de tensão para frequência para carregar e descarregar o capacitor C. As tensões máximas e mínimas que determinam o ponto de chaveamento são fornecidas pelo circuito de referência de tensão. O circuito de driver e o transistor de saída fornecem o sinal digital resultante da conversão.

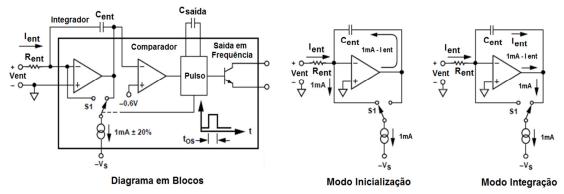

### 2.1.2 VFC de carga balanceada

O VFC de carga balanceada utiliza um circuito integrador, um comparador e um circuito de corrente de carga [32,33]. Neste sistema a tensão de entrada é aplicada ao circuito integrador através de um resistor (R<sub>IN</sub>) que inicia a carga do capacitor (Cint) como ilustrado na Figura 2.4. O capacitor é carregado com uma corrente que é matematicamente igual a corrente de referência interna (1mA) menos a corrente de entrada (I<sub>IN</sub>). Quando a saída do

integrador atinge um determinado valor de tensão o circuito de chaveamento muda a operação para o modo descarga iniciando a descarga do capacitor com um valor de corrente igual a corrente de entrada [35]. A Figura 2.5 mostra o ciclo de carga e descarga do capacitor deste circuito.

Figura 2.4 – Circuito VFC tipo carga balanceada.

Fonte: Voltage-to-Frequency and Frequency-to-Voltage Converter AD650 [35].

Figura 2.5 – Tensão sobre o capacitor C<sub>ent</sub> durante a carga e descarga.

Fonte: Voltage-to-Frequency and Frequency-to-Voltage Converter AD650 [35].

# 2.2 Parâmetros que avaliam um VFC

Em todo processo de conversão, naturalmente se deseja obter uma leitura exata do valor original que foi convertido. Obviamente a exatidão pode não ser possível em sistemas onde sinais analógicos estão envolvidos, pois todo sistema está sujeito à ruídos, distorções, erros e outros fatores que fazem com que o valor obtido não seja exato. Seguem os parâmetros utilizados para avaliar a exatidão da informação final obtida em um sistema utilizando VFC.

#### 2.2.1 Níveis máximos e mínimos de sinal na entrada

É desejável que um VFC suporte qualquer nível de tensão fornecido pelo sensor e forneça sempre uma resposta linear de frequência com relação ao valor de tensão na entrada. Porém, nos circuitos práticos, tensões de entrada acima da tensão de alimentação positiva e abaixo do referencial de terra (ou alimentação negativa) normalmente não são permitidas. Os valores de entrada de um VFC, na maioria dos casos, estão entre o limite inferior (Vent,min) e o limite superior (Vent,max) [30] de tensão de entrada.

#### 2.2.2 Níveis máximos e mínimos do sinal na saída

Como o sinal de saída do VFC é um sinal digital resultante de um oscilador, os valores máximos e mínimos de saída a serem avaliados são valores de frequência. Em baixas frequências o desempenho de um VFC é definido pela estabilidade da fonte de corrente e da limitação de tempo do oscilador que é definida pelo capacitor e outros parâmetros. Em altas frequências efeitos de segunda ordem como transientes de chaveamento do integrador e a precisão do chaveamento de carga e descarga determinam a precisão e a linearidade do sistema [33]. Os valores máximos e mínimos de saída são chamados de limite máximo (fo,max) e limite mínimo (fo,min) [30] de saída.

### 2.2.3 Largura de faixa do sinal de saída

Matematicamente, a largura de faixa do sinal de saída - FS (Frequency Span) é a diferença entre a máxima e mínima frequência de saída:

$$FS = f_{0,max} - f_{0,min} (2.2)$$

onde:

FS = Largura de faixa do VFC,

$f_{0,max}$  = Limite máximo de frequência na saída do VFC,

$f_{0,min}$  = Limite mínimo de frequência na saída do VFC.

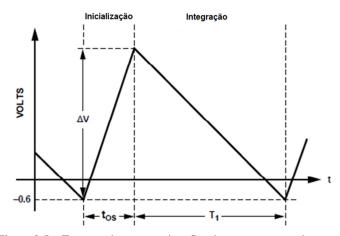

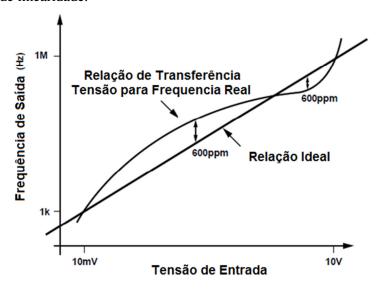

A função de transferência real possui um desvio em relação à ideal. Este desvio deve ser considerado na determinação da largura de faixa do sinal de saída [36]. A Figura 2.6 mostra graficamente a função de transferência ideal e o desvio que pode ocorrer nos conversores práticos.

Figura 2.6 – Função de transferência e a determinação de FS.

Fonte: Handbook of Modern Sensors, Physics, Designs, and Applications [36].

### 2.2.4 Sensibilidade (ganho)

A sensibilidade é uma relação entre a variação da frequência de saída e a variação do sinal de entrada. Este parâmetro é derivado da função de transferência e pode ser definido matematicamente como:

$$S = \frac{d_{fo}}{dV_{in}} \tag{2.3}$$

onde:

S = Sensibilidade ou ganho do VFC,

$d_{fo}$  = Variação da frequência na saída do VFC,

$dV_{in}$  = Variação da tensão na entrada do VFC.

Esta relação considera o VFC como um dispositivo linear onde a sensibilidade determina a inclinação de uma reta levando a seguinte equação [30]:

$$f_o = S.V_{in} \tag{2.4}$$

onde:

$f_0$  = Frequência de saída do VFC,

S = Sensibilidade ou ganho do VFC,

$V_{in}$  = Tensão de entrada do VFC.

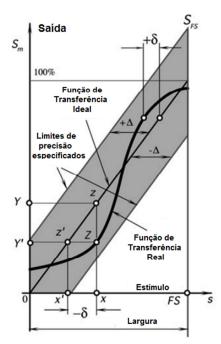

### 2.2.5 Erro de ganho

Como especificado no Item 2.2.4, o ganho ou sensibilidade é um fator de escala que relaciona a tensão de entrada com a frequência de saída. O erro de ganho é um desvio provocado pela inclinação da reta de transferência real em relação à inclinação da reta de transferência ideal. Este desvio deve ser medido quando o circuito está com a maior frequência de saída [37]. A Figura 2.7 mostra duas retas, uma delas sem erro de desvio de ajuste (erro de offset) e outra com erro. A terceira reta é a reta real com erro de ganho provocado pela inclinação.

Figura 2.7 – Erro de offset e erro de ganho de um VFC.

Fonte: 3V/5V Low Power, Synchronous Voltage-to-Frequency Converter AD7740 [37].

### 2.2.6 Erro de desvio de ajuste

Idealmente a frequência mínima de saída (fo,min) para o valor mínimo de tensão na entrada (Vin,min) deve obedecer a função de transferência. Um desvio deste valor provoca um deslocamento de valor fixo em todos os pontos de operação do circuito. Graficamente o erro de desvio de ajuste, também chamado de erro de offset, pode ser representado por uma reta paralela à reta ideal, como ilustrado na Figura 2.7. O erro de desvio de ajuste é comumente medido em mV [37].

### 2.2.7 Erro relativo

O erro relativo em um determinado ponto de operação é calculado a partir de uma medida experimental da frequência neste ponto levando-se em conta o valor ideal esperado [30]. Esse erro é medido percentualmente, dado por:

$$Erro\ relativo = \frac{f_{0,medido} - f_{0,te\'orico}}{f_{0,te\'orico}}.100\%$$

(2.5)

onde:

Erro relativo = Erro em um determinado ponto de operação do conversor, fo, medido = Frequência de saída medida no ponto de operação, fo, teórico = Frequência de saída calculada teoricamente para o ponto de operação.

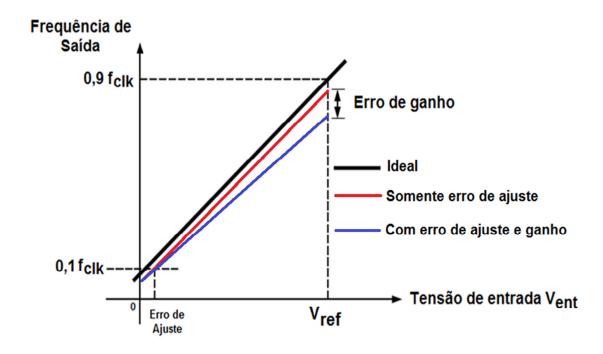

#### 2.2.8 Erro de linearidade

O erro de linearidade é uma medida de desvio. Existem várias formas de se fazer a medição do erro de linearidade de um VFC. Uma das formas é fazer medidas em muitos pontos de operação e através de regressão linear obter uma reta que passa entre esses pontos. O ponto que mais se distancia desta reta determina o erro de linearidade [30]. Outra forma de se fazer a medida de erro de linearidade é utilizar como referência a reta ideal de conversão, fazer as medidas experimentalmente e verificar o desvio máximo [33,34,35]. A Figura 2.8 ilustra um erro de linearidade.

Figura 2.8 – Ilustração do erro de linearidade.

Fonte: Voltage-to-Frequency and Frequency-to-Voltage Converter AD650 [35].

### 2.2.9 Erro de linearidade provocado por temperatura

É a medição do erro de linearidade com variação de temperatura mantendo os demais parâmetros constantes [30].

### 2.2.10 Razão de rejeição de variação da fonte de alimentação.

O erro provocado pela variação da tensão da fonte - PSRR (Power Supply Rejection Ratio) é um erro que altera o ganho do VFC. Este erro pode ser medido em ppm/% (partes por milhão por porcentagem) [34] ou expresso em decibel (dB) [30]. Como exemplo suponha um VFC alimentado com uma fonte simétrica de +15V e -15V tenha na entrada uma tensão de 10V e produza uma saída de 100KHz. Mudando a tensão de alimentação para +12,5V e -12V o mesmo VFC altera sua saída para 99,9KHz. Como ilustrado na Tabela 2.1.

Tabela 2.1 – Variação da frequência de saída em função da variação da fonte de alimentação.

| Tensão de alimentação | Tensão na entrada | Frequência na saída |

|-----------------------|-------------------|---------------------|

| +15V e -15V           | 10V               | 100,0KHz            |

| +12,5V e -12,5V       | 10V               | 99,9KHz             |

A variação de frequência é dada por:

Variação de frequência =

$$\frac{100}{99,9}$$

= 1,001 (2.6)

Esse valor corresponde à uma variação de 0,1% ou 1000 ppm. Como a tensão de alimentação teve uma variação de 5V em 30V, a variação representa 5/30 = 16,67%. Assim a razão de rejeição da fonte de alimentação é [34]:

$$PSRR = \frac{1000}{16.67} = 60ppm/\% \tag{2.7}$$

### 2.3 Moduladores por intervalo de pulso

Um modulador por intervalo de pulso PIM (Pulse Interval Modulation) transmite pulsos de pequena duração em determinados espaços de tempos. A informação transmitida é representada pelo espaço de tempo entre estes pulsos [38], como ilustra a Figura 2.9.

Figura 2.9 – Informação transmitida em um sinal PIM.

O modulador PIM é utilizado em sistemas de transmissão baseados na detecção de energia e possuem baixa complexidade e custo. Diferentemente dos sistemas que utilizam a informação da fase do sinal, chamados de recepção coerente, os sistemas de detecção de energia recebem somente o envelope do sinal, como exemplo a potência instantânea [39].

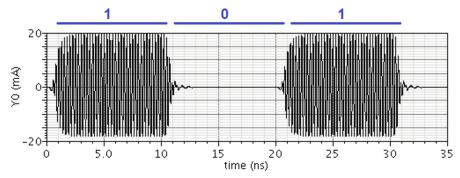

Nos sistemas atuais baseados na detecção de energia é comum a utilização da modulação por chaveamento de portadora OOK (On Off Keying) e modulação por posição de pulso PPM (Pulse Position Modulation). A modulação por chaveamento de portadora consiste em chavear o transmissor de acordo com o bit a ser transmitido [40], por exemplo, o "bit 1" pode ser representado pela presença da portadora e o "bit 0" representado pela ausência da portadora, como mostra a Figura 2.10.

Figura 2.10 - Exemplo de sinal modulado por chaveamento de portadora.

Fonte: Design of Wide Band OOK Transmitter for Biomedical Applications [40].

Na modulação por posição de pulso o sinal de entrada controla a posição do pulso com relação à um referencial de tempo ou janela de tempo. Apesar de bastante popular e possuir grandes vantagens em alguns contextos, este sistema de modulação é vulnerável à perda de sincronismo mesmo quando recebido em bom nível e sem ruído [41].

É possível transmitir altas taxas, como 20 Mbps, com a modulação OOK [40], porém apresenta alto consumo. A modulação PPM reduz consideravelmente o consumo quando comparada com a modulação OOK, no entanto apresenta alta taxa de erros em velocidades de transferência de dados mais altas. A modulação PIM, que tem sido amplamente estudada em sistemas de comunicação óticos, é uma opção intermediária com consumo reduzido e taxa de transferência maior que a propiciada pelo modulador PPM [42].

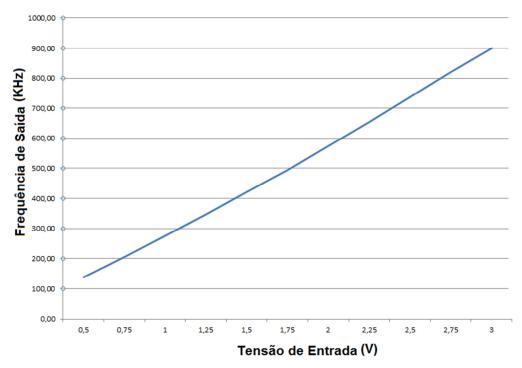

# 2.4 Considerações teóricas sobre este trabalho

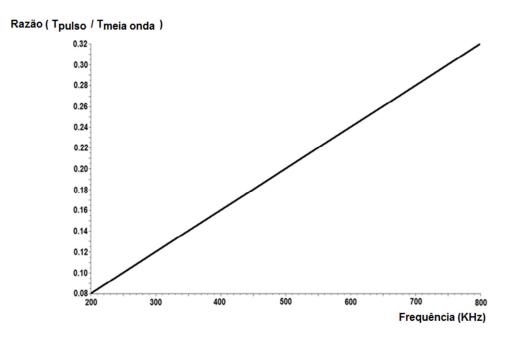

Neste trabalho a modulação PIM é utilizada para reduzir o consumo total de energia transmitida por um VFC. Como mencionado no Item 1.3, a economia de energia se dá pela redução do tempo em que o transmissor permanece ligado. Para analisar o consumo de energia, considere um modulador PIM com largura de pulso ajustado para  $0.2\mu$ s. Quando o VFC está transmitindo um sinal de 200KHz, cada ciclo liga o transmissor por  $2.5\mu$ s. Nesta situação, como a largura do sinal do modulador PIM está fixada em  $0.2\mu$ s, há uma relação de 0.2/2.5 = 0.08 ou seja 8%, como ilustra a Figura 2.11.

Figura 2.11 – Pulso do modulador PIM e um sinal de 200KHz de um VFC.

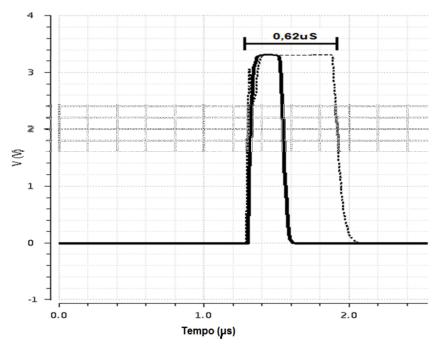

A economia de energia não é fixa. Na frequência de 800KHz o modulador PIM tem os mesmos  $0.2\mu$ s de largura de pulso e o VFC um sinal com tempo ligado de  $0.62\mu$ s. Assim a relação é de 0.2/0.62 = 0.323 ou seja 32.3%, como ilustra a Figura 2.12.

Figura 2.12 – Pulso do modulador PIM e um sinal de 800KHz de um VFC.

Assim, no pior caso há uma economia maior que 67% de energia uma vez que o transmissor permanecerá ligado por 32,3% do tempo. Pode-se determinar o valor exato da economia para cada frequência. O período do sinal do VFC é o inverso de sua frequência.

$$T_{VFC} = \frac{1}{f_{VFC}} \tag{2.8}$$

O tempo em que o transmissor fica ligado é a metade do período.

$$T_{\text{meia onda}} = \frac{T_{\text{VFC}}}{2} \tag{2.9}$$

A razão entre o tempo do pulso do modulador PIM e período em que o transmissor fica ligado pode ser calculado por:

$$Raz\tilde{a}o = \frac{T_{Pulso}}{T_{meia\ onda}}$$

(2.10)

Esta razão determina diretamente a porcentagem total de energia utilizada por um modulador PIM e pode ser reescrita como:

$$Raz\tilde{a}o = 2.T_{pulso}.f_{VFC}$$

(2.11)

A Figura 2.13 mostra graficamente a razão calculada para cada frequência. Para validação dos resultados, um VFC completo e um conversor PIM foram projetados em tecnologia IBM CMOS de 130nm, como descrito nos Capítulos 3 e 4.

Figura 2.13 – Uso da energia do modulador PIM comparado ao VFC.

# Capítulo 3 – O circuito VFC

# 3.1 Diagrama geral do VFC

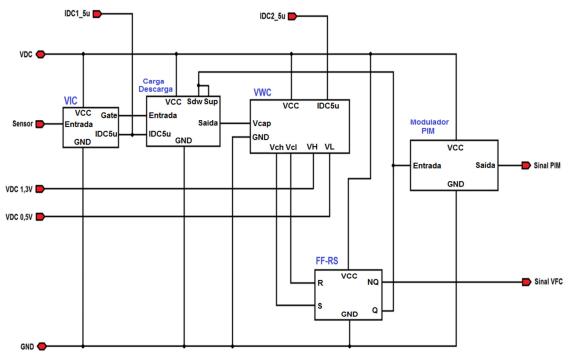

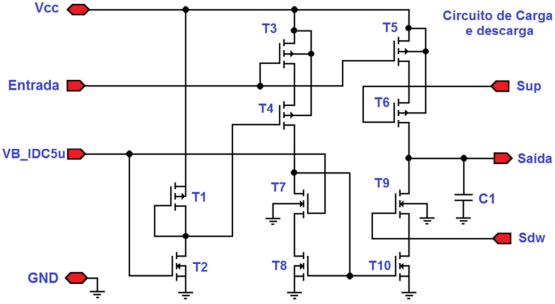

O diagrama de blocos do VFC desenvolvido neste trabalho está representado na Figura 3.1.

Figura 3.1 – Diagrama em blocos do VFC com modulador PIM.

A tensão fornecida pelo sensor é aplicada à entrada do conversor tensão corrente –*VIC*, como indicado na Figura 3.1. Esta tensão é convertida linearmente em uma corrente, e um referencial de controle desta corrente é fornecido ao circuito de carga e descarga.

O circuito de carga e descarga é responsável por carregar e descarregar um capacitor com uma corrente constante. O valor desta corrente é determinado pelo referencial fornecido pelo circuito *VIC*. Os pinos *Sdw* e *Sup* do bloco "*Carga Descarga*" determinam se o circuito está no modo carga ou modo descarga.

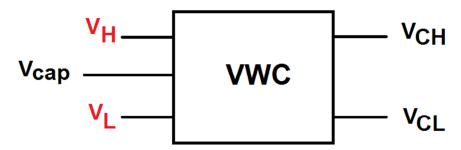

A saída do circuito de carga e descarga é ligada diretamente no capacitor que se encontra no bloco denominado comparador de janela de tensão *VWC* (Voltage Window Comparator). Este bloco recebe as tensões de referência *VH* (Voltage High) e *VL* (Voltage Low) que respectivamente determinam o maior e o menor valor de tensão permitida ao capacitor e consequentemente os pontos de chaveamento do circuito. Os pinos *Vch* e *Vcl* produzem o chaveamento através de um circuito *FF-RS*. O *FF-RS* evita sinais transitórios durante o chaveamento, fornece a saída de sinal do VFC e um sinal de controle para o circuito de carga e descarga alterando sua condição.

O *Modulador PIM* é a inovação proposta por este trabalho. Ele transforma o sinal quadrado característico de um circuito VFC em um sinal modulado por intervalo de pulso.

### 3.2 O conversor tensão corrente

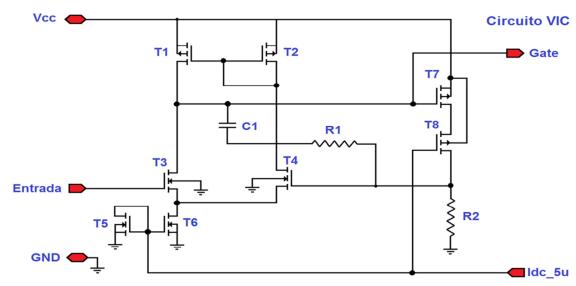

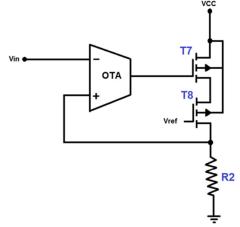

O circuito conversor tensão corrente - *VIC* (Voltage to Current Converter) é o circuito de entrada do VFC. A Figura 3.2 mostra o diagrama esquemático deste conversor.

Figura 3.2 – Esquema completo do conversor VIC.

As dimensões W/L dos transmissores MOS utilizados neste circuito são mostradas na Tabela 3.1, o capacitor C1 possui uma capacitância de 400fF, o resistor R1 possui uma resistividade de  $5K\Omega$  e o resistor R2 uma resistividade de  $20K\Omega$ .

Tabela 3.1 – Dimensões do circuito conversor VIC.

| Transistor | T1     | T2     | Т3     | T4     | T5     | Т6     | T7      | T8      |

|------------|--------|--------|--------|--------|--------|--------|---------|---------|

| W/L (µm)   | 20/1,2 | 20/1,2 | 60/1,2 | 60/1,2 | 10/1,2 | 20/1,2 | 300/1,2 | 300/1,2 |

Este circuito VIC é baseado em um modelo proposto por [30] que utiliza um amplificador com par diferencial na configuração clássica formando um amplificador operacional de transcondutância - OTA (Operational Transcondutance Amplifier) [43,44,45] e uma resistência que fornece a corrente de referência. Para adequação à tecnologia IBM CMOS de 130nm, os transistores foram dimensionados com canal de  $0,4\mu$ m e larguras reduzidas. Através de análise de sinais e aplicação de conceitos teóricos, foram realizados ajustes nas dimensões dos transistores até se obter os resultados desejados. Neste circuito o transistor T5 com dreno ligado ao gate recebe uma corrente constante de  $5\mu$ A proveniente de uma fonte de referência. Este transistor é utilizado como referência de corrente para o transistor T6 que fornece uma corrente constante de  $10\mu$ A ao circuito amplificador operacional de transcondutância OTA formado pelos transistores T1, T2, T3 e T4.

Os transistores T1 e T2 trabalham no modo saturação e são utilizados neste circuito como carga ativa [44,45] dos transistores T3 e T4. Para evitar picos de tensão em altas frequências e oscilações no amplificador OTA, um circuito de compensação RC formado por R1 e C1 é ligado entre a entrada e a saída.

Uma representação simplificada deste circuito pode ser visualizada na Figura 3.3.

Figura 3.3 – Representação simplificada do conversor VIC.

Inicialmente parece ser um amplificador com realimentação positiva, porém o transistor T7 é do tipo PMOS e trabalha como inversor, assim a realimentação é negativa. O transistor T8 recebe uma tensão de referência fixa no gate e é utilizado como amplificador gate comum, e assim tem como entrada um sinal aplicado em sua fonte. Os transistores T7 e T8 funcionam como um amplificador cascode [45]. A utilização de um circuito cascode melhora o espelhamento de corrente [30].

O amplificador OTA com o circuito de realimentação mostrado na Figura 3.2 foi projetado para funcionar como buffer (ganho unitário). Assim, a tensão sobre o resistor R2 é igual à tensão de entrada Vin sendo a corrente produzida diretamente proporcional à tensão de entrada. A tensão do gate de T7 é fornecida na saída do circuito VIC permitindo através do espelhamento de corrente replicar a corrente do resistor R2 [44,45,46].

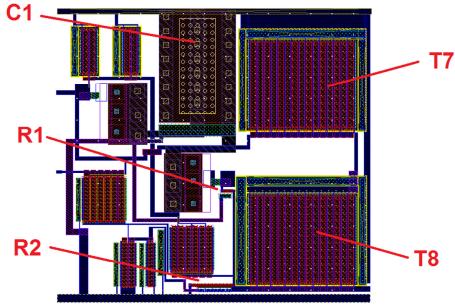

Para garantir o fornecimento de corrente com grande linearidade, os transistores T7 e T8 foram projetados com alta transcondutância e ocupam uma área considerável do layout do circuito tensão corrente, como pode ser visto na Figura 3.4.

Figura 3.4 – Layout do conversor tensão corrente VIC.

Os transistores T7 e T8 foram implementados com layout na forma dobrada, diminuindo assim a resistividade dos terminais do gate [45] e melhorando a disposição física destes componentes no layout como um todo.

## 3.3 O circuito de carga e descarga

O circuito de carga e descarga é um circuito de chaveamento que, carrega e descarrega um capacitor com corrente constante. Este circuito foi baseado em [30]. Os transistores foram redimensionados adequando-se à tecnologia IBM CMOS de 130nm. A Figura 3.5 mostra seu diagrama esquemático.

Figura 3.5 – Circuito de carga e descarga.

As dimensões W/L dos transmissores MOS utilizados neste circuito são mostradas na Tabela 3.2.

Tabela 3.2 – Dimensões dos transistores do circuito de carga e descarga.

| Transistor | T1        | T2       | T3     | T4     | T5     | T6     | T7    | Т8    | T9     | T10   |

|------------|-----------|----------|--------|--------|--------|--------|-------|-------|--------|-------|

| W/L (μm)   | 11,25/1,2 | 3,75/1,2 | 14/1,2 | 14/1,2 | 14/1,2 | 14/1,2 | 5/1,2 | 5/1,2 | 10/1,2 | 5/1,2 |

Neste circuito, os transistores T5 e T6 formam um circuito cascode que carrega o capacitor ligado à saída. A corrente de carga é determinada pelo sinal de entrada que é a tensão de referência do gate do circuito VIC. Os transistores T1 e T2 fornecem o referencial de tensão para que o transistor T4 opere na configuração gate comum. Os transistores PMOS T3 e T4 fazem o espelhamento da corrente. Para ter uma referência desta mesma corrente em relação ao terra com transistores NMOS, os transistores T7 e T8 formam um circuito de espelho de corrente de ampla excursão [47]. Esta referência de corrente é passada para o transistor T10, que junto com o transistor T9 formam o circuito de descarga. As entradas Sdw e Sup definem o modo de operação carga ou modo descarga do circuito. A Figura 3.6 indica o funcionamento deste circuito.

Figura 3.6 – Representação simplificada do circuito de carga e descarga.

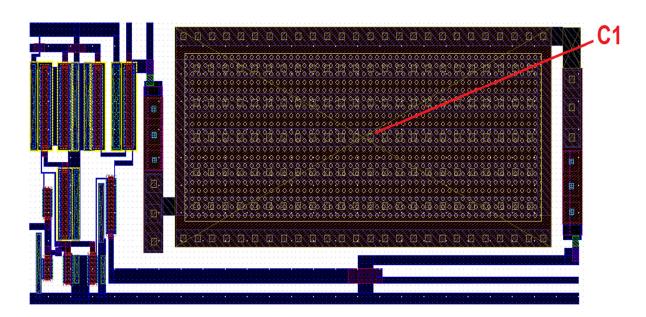

O componente de maior área neste circuito é o capacitor C1, como pode ser visto na Figura 3.7.

Figura 3.7 – Layout do circuito de carga e descarga.

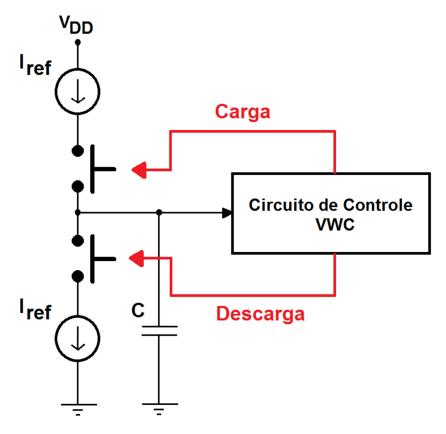

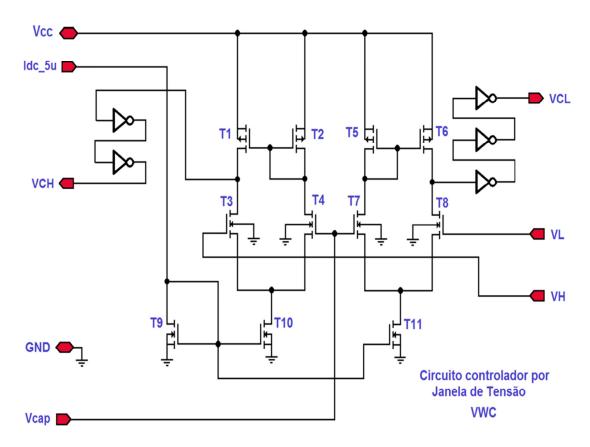

#### 3.4 O circuito de controle

O circuito de controle é um comparador de janela de tensão - VWC (Voltage Window Comparator), como ilustrado na Figura 3.8. O transistor T9 fornece uma tensão de referência para os transistores T10 e T11 que funcionam como espelho de corrente para o dois pares diferencias do circuito, formados pelos transistores T1, T2, T3 e T4 e os transistores T5, T6, T7 e T8. A tensão do capacitor V<sub>cap</sub> é aplicada diretamente na entrada dos pares diferenciais.

Figura 3.8 – Circuito controlador de janela de tensão VWC.

As dimensões W/L dos transmissores MOS utilizados neste circuito são mostradas na Tabela 3.3.

Tabela 3.3 – Dimensões dos transistores do circuito controlador de janela de tensão.

| Transistor | T1    | T2    | T3     | T4     | T5     | T6     | T7     | T8     | T9     | T10    | T11    |

|------------|-------|-------|--------|--------|--------|--------|--------|--------|--------|--------|--------|

| W/L (μm)   | 5/0,4 | 5/0,4 | 40/0,4 | 40/0,4 | 20/0,4 | 20/0,4 | 20/0,4 | 20/0,4 | 10/1,2 | 16/0,4 | 40/1,2 |

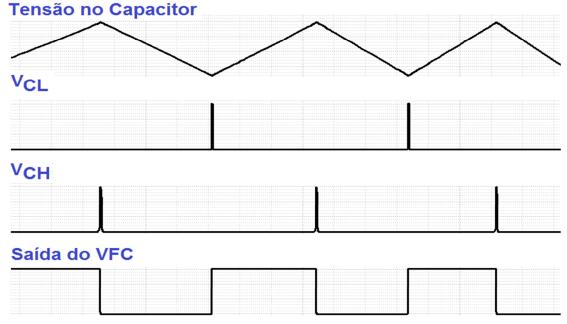

A utilização de dois pares diferenciais e portas inversoras para reduzir os efeitos transitórios deste circuito é uma sugestão de [30]. Baseado nesta concepção, a lógica de chaveamento foi feita. Inúmeros testes permitiram determinar as dimensões ideais dos transistores. Como pode ser visto na Tabela 3.3 a grande maioria possui um canal de  $0.4\mu m$ , uma dimensão muito próxima do limite da tecnologia IBM CMOS de 130nm e compatível com redução de custo e área. Os inversores do circuito VWC e do Flip Flip RS descrito no Item 3.5.3 não são simétricos, isso é necessário para evitar que o circuito encontre um ponto de repouso e consequentemente pare ou não inicie a oscilação. Supondo que o circuito do VFC tenha sido ligado e esteja no modo de carga, estando a tensão do capacitor menor que  $V_H$ e maior que  $V_L$ , as saídas  $V_{CL}$  e  $V_{CH}$  estarão com níveis lógicos zero. Ao atingir o valor de tensão  $V_H$ , a tensão do capacitor altera o estado do par diferencial formado por T1, T2, T3 e T4, que leva à saída V<sub>CH</sub> ao estado lógico 1. Este estado leva o flip flop RS para o estado lógico 1 que chaveia o circuito carga e descarga para o modo descarga. Neste instante o capacitor começa a descarregar. Quando a tensão do capacitor ficar abaixo do nível de tensão  $V_H$ , a saída  $V_{CH}$  retorna para o estado lógico 0. O mesmo ocorre com o par diferencial formado por T5, T6, T7 e T8, porém neste com valores abaixo de V<sub>L</sub>. De forma resumida, este circuito carrega o capacitor até o limite superior onde inicia a descarga do mesmo até o limite inferior onde passa a carregar o capacitor novamente.

Figura 3.9 – Sinais de saída do circuito comparador de janela de tensão.

A Figura 3.10 mostra um modelo simplificado do circuito controlador de janela de tensão onde  $V_H$  e  $V_L$  representam os valores constantes de referência,  $V_{CAP}$  representa a tensão do capacitor e  $V_{CH}$  e  $V_{CL}$  representam as saídas. Os inversores utilizados neste circuito funcionam como buffer e amenizam o efeito de sinais transitórios provocados pelo chaveamento dos pares diferenciais.

Figura 3.10 – Modelo simplificado do circuito controlador de janela de tensão.

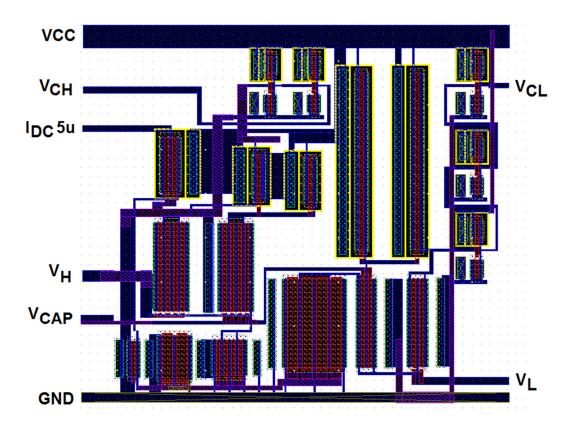

A Figura 3.11 mostra o layout do circuito controlador de janela de tensão implementado.

Figura 3.11 – Layout do circuito controlador de janela de tensão VWC.

#### 3.5 Circuitos auxiliares

#### 3.5.1 A porta inversora

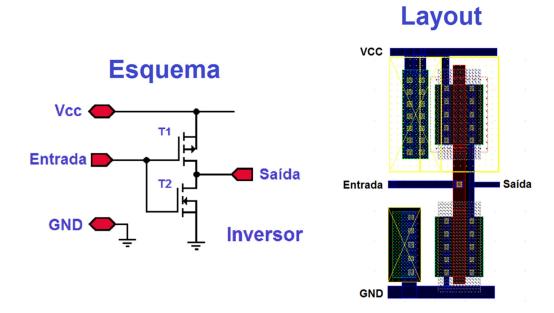

A porta inversora utilizada neste projeto possui uma não-simetria que a diferencia dos projetos tradicionais. A Figura 3.12 mostra o esquema e o layout utilizados.

A mobilidade de carga de um cristal N não é a mesma de um cristal tipo P. Assim sendo a relação W/L não é a mesma em uma porta inversora simétrica, ou seja, uma porta inversora que muda de estado quando a tensão atinge um valor próximo à metade do valor da tensão de alimentação [44].

Figura 3.12 – Esquema e layout da porta inversora.

As dimensões W/L dos transmissores MOS utilizados neste circuito são mostradas na Tabela 3.4.

Tabela 3.4 – Dimensões do circuito da porta inversora.

| Transistor | T1    | T2    |

|------------|-------|-------|

| W/L (μm)   | 2/0,4 | 2/0,4 |

Como pode ser visto na Figura 3.12, os dois transistores possuem as mesmas dimensões e consequentemente a porta muda de estado com um valor de entrada menor que a metade da tensão de alimentação. Esta configuração foi propositalmente utilizada pois a simetria dos circuitos cria situações de estabilidade onde o circuito não inicia ou para de oscilar. Esse recurso também foi utilizado no circuito controlador de janela de tensão.

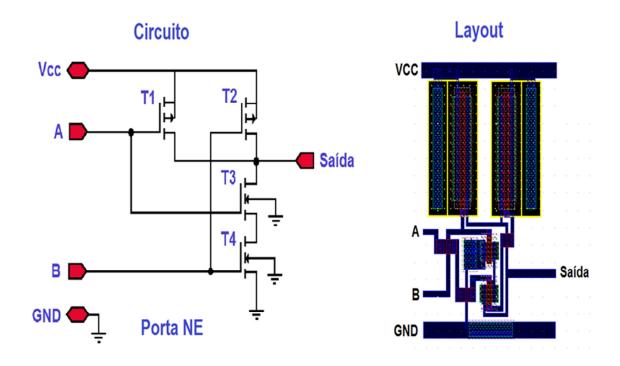

### 3.5.2 A porta Não-E

A porta Não-E utilizada foi projetada para atender as necessidades do circuito VFC com a menor área possível. Ela é composta de 4 transistores, que combinados implementam a lógica Não-E [44]. O esquema e layout são mostrados na Figura 3.13.

Figura 3.13 – Esquema e layout da porta Não E.

As dimensões W/L dos transmissores MOS utilizados neste circuito são mostradas na Tabela 3.5.

Tabela 3.5 – Dimensões do circuito da porta Não E.

| Transistor | T1    | T2    | T3    | T4    |

|------------|-------|-------|-------|-------|

| W/L (µm)   | 6/0,4 | 6/0,4 | 1/0,4 | 1/0,4 |

#### 3.5.3 O flip flop RS

O flip flop RS é formado pela interligação de duas portas Não E e duas portas inversores, como mostra a Figura 3.14.

Figura 3.14 – Esquema e layout do flip flop RS.

## 3.6 Resultados dos testes e implementação

Neste item, além da determinação dos principais parâmetros do VFC projetado, o desempenho do mesmo é avaliado baseado nos critérios de avaliação descritos no Item 2.2.

#### 3.6.1 Linearidade do conversor VIC

Como descrito no Item 3.2, o circuito conversor VIC tem como finalidade a conversão da tensão de entrada em uma corrente diretamente proporcional. A Figura 3.15 mostra a corrente de saída do conversor tensão corrente VIC (Voltage to Current Converter) com relação à tensão de entrada.

Figura 3.15 – Referência de corrente de saída e tensão de entrada do VIC.

Para análise da linearidade foi utilizada uma fonte de tensão variável na entrada com tensão inicial em 0V e tensão final em 3,3V que corresponde à tensão de alimentação do VFC. Claramente há uma boa linearidade em toda faixa, demonstrando a operação esperada do conversor, apesar dos desvios que ocorrem para tensões menores que 0,4V, como ressaltado na Figura 3.16.

Figura 3.16 – Linearidade do conversor VIC para tensões de entrada baixas.

Esta não linearidade para valores de tensão de entrada menores que 0,4 volts ocorre devido ao fato que, o transistor T7 mostrado nas Figuras 3.2 e 3.3 necessita operar no modo saturação. O ponto exato desta não linearidade pode variar com o processo de fabricação e até mesmo em circuitos integrados de um mesmo processo, fato esse conhecido como descasamento e variação de processo local LPVM (Local Process Variation and Mismatch) [48].

A Figura 3.17 mostra o ponto superior onde a linearidade termina, para uma máxima tensão na entrada de 3,24V.

Figura 3.17 – Linearidade do conversor VIC para tensões de entrada altas.

Neste caso, as tensões entre dreno e fonte VDS dos transistores T7 e T8 em saturação impedem que a resistência R2 mostrada nas Figuras 3.2 e 3.3 receba a tensão  $V_{CC}$ . Desta forma, a máxima corrente de saída está limitada em:

$$I_{max} = \frac{V_{cc} - V_{DS,sat\ T7} - V_{DS,sat\ T8}}{R_2}$$

(3.1)

É possível observar que, entre estes limites o conversor VIC apresenta grande linearidade.

### 3.6.2 Curva de carga e descarga do capacitor

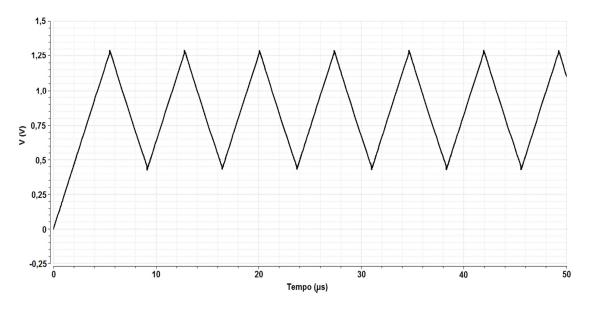

O circuito de carga e descarga funciona como integrador, assim o resultado esperado da forma de onda no capacitor C1, mostrado na Figura 3.5, é uma onda triangular linear [30]. A Figura 3.18 mostra a tensão no capacitor para uma tensão de entrada de 0,5V, ou seja, uma tensão próxima à tensão mínima de entrada.

Figura 3.18 – Tensão no capacitor C1 para 0,5 volts na entrada do VFC.

A Figura 3.19 ilustra a mesma forma de onda, porém esta com valor de entrada próximo ao limite de linearidade superior. Apesar de parecidos, os gráficos apresentam escalas de tempo diferentes. O período da onda triangular do gráfico da Figura 3.18 é de aproximadamente  $7,2\mu$ s, o período da onda no gráfico da Figura 3.19 é de  $0,85\mu$ S. A similaridade dos gráficos indica uma grande linearidade do circuito.

Figura 3.19 - Tensão no capacitor C1 para 3,24 volts na entrada do VFC.

### 3.6.3 Relação tensão de entrada versus frequência de saída

A Tabela 3.6 apresenta os valores de período e frequência de saída medidos para vários valores de tensão de entrada do VFC.

| Tensão de entrada | Período | Frequência (KHz) |

|-------------------|---------|------------------|

| 0,50V             | 7,29µs  | 137,24           |

| 0,75V             | 4,87µs  | 205,34           |

| 1,00V             | 3,63µs  | 275,48           |

| 1,25V             | 2,88μs  | 347,22           |

| 1,50V             | 2,38µs  | 420,17           |

| 1,75V             | 2,02μs  | 495,05           |

| 2,00V             | 1,74μs  | 574,71           |

| 2,25V             | 1,53μs  | 653,59           |

| 2,50V             | 1,36µs  | 735,29           |

| 2,75V             | 1,22μs  | 819,67           |

| 3,00V             | 1,11µs  | 900,90           |

Tabela 3.6 – Valores do período e frequência na saída do VFC em função a entrada.

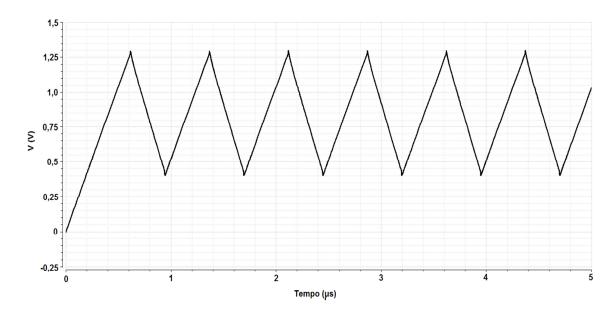

A Figura 3.20 mostra o gráfico obtido à partir dos valores da Tabela 3.6. Propositalmente valores abaixo de 0,5V e acima de 3V foram omitidos.

$0.38 \mu s$

2.631,57

3,24V

Figura 3.20 – Gráfico da frequência em função da tensão de entrada.

#### 3.6.4 Erro de linearidade

Utilizando regressão linear, pode-se obter a equação de transferência do circuito a partir dos valores da Tabela 3.6. O método dos mínimos quadrados foi utilizado. Deseja-se encontrar a constante de proporcionalidade k de uma reta para atender a equação descrita no Item 2.1. Matematicamente tem-se:

$$Y = k.X + \mathcal{E} \tag{3.2}$$

onde:

Y = Frequência de saída do VFC,

X = Tensão de entrada do VFC,

K =Coeficiente de regressão,

$\mathcal{E}$  = Constante de regressão.

pela regressão linear tem-se:

$$k = \frac{\sum X_i Y_i - \frac{\sum X_i \sum Y_i}{n}}{\sum X_i^2 - \frac{(\sum X_i)^2}{n}} \qquad \mathcal{E} = \overline{Y} - k\overline{X}$$

(3.3)

assim  $\,k=306,\!267747\,$  e  $\,\mathcal{E}=-30,\!0889781,\,$  portanto a resposta do VFC e dada por

$$f_o = 306,267747.V_{in} - 30,0889781 (3.4)$$

Como descrito no Item 2.2.8, uma das formas de se medir o erro de linearidade é tomar o ponto mais distante da reta encontrada. Como mostra a tabela 3.7.

Tabela 3.7 – Medida de desvio utilizada para determinação do erro de linearidade.

| Tensão de entrada | Frequência<br>Calculada (KHz) | Frequência<br>Medida (KHz) | Desvio | Erro de<br>Linearidade |

|-------------------|-------------------------------|----------------------------|--------|------------------------|

| 0,50V             | 123,04                        | 137,24                     | 14,20  | 11,53%                 |

| 0,75V             | 199,61                        | 205,34                     | 5,73   | 2,86%                  |

| 1,00V             | 276,18                        | 275,48                     | -0,70  | 0,25%                  |

| 1,25V             | 352,75                        | 347,22                     | -5,52  | 1,56%                  |

| 1,50V             | 429,31                        | 420,17                     | -9,15  | 2,13%                  |

| 1,75V             | 505,88                        | 495,05                     | -10,83 | 2,14%                  |

| 2,00V             | 582,45                        | 574,71                     | -7,73  | 1,32%                  |

| 2,25V             | 659,01                        | 653,59                     | -5,42  | 0,82%                  |

| 2,50V             | 735,58                        | 735,29                     | -0,29  | 0,04%                  |

| 2,75V             | 812,15                        | 819,67                     | 7,53   | 0,93%                  |

| 3,00V             | 888,71                        | 900,90                     | 12,19  | 1,37%                  |

O erro de linearidade calculado na Tabela 3.7 foi determinado por:

$$Erro de linearidade = \frac{Desvio}{Frequência Calculada}$$

(3.5)

Pode-se concluir que o erro de linearidade do circuito é de 2,86% se a tensão de entrada for  $0.75 \, \text{V} < V_{\text{entrada}} < 3.0 \, \text{V}$ .

#### 3.6.5 Valores máximos e mínimos de entrada e saída

A Figura 3.16 mostra que o conversor tensão frequência VIC não responde linearmente para valores abaixo de 0,4V. Para garantir que o dispositivo trabalhe sempre dentro da linearidade, o valor mínimo de 0,5V foi adotado para cálculo da equação linear. A Tabela 3.8 fornece os valores de desvio e erro de linearidade obtidos para uma tensão de entrada abaixo de 0,5V.

Tabela 3.8 – Medida de desvio e erro para tensões abaixo de 0,5V de entrada.

| Tensão de entrada | Frequência<br>Calculada (KHz) | Frequência<br>Medida (KHz) | Desvio | Erro de<br>Linearidade |

|-------------------|-------------------------------|----------------------------|--------|------------------------|

| 0,50V             | 123,04                        | 137,24                     | 14,20  | 11,53%                 |

| 0,48V             | 116,92                        | 131,87                     | 14,95  | 12,79%                 |

| 0,46V             | 110,79                        | 126,49                     | 15,69  | 14,16%                 |

| 0,44V             | 104,67                        | 121,11                     | 16,44  | 15,71%                 |

| 0,42V             | 98,54                         | 115,74                     | 17,19  | 17,44%                 |

| 0,40V             | 92,42                         | 110,36                     | 17,93  | 19,41%                 |

| 0,38V             | 86,29                         | 104,98                     | 18,69  | 21,66%                 |

| 0,36V             | 80,17                         | 99,60                      | 19,43  | 24,24%                 |

A Tabela 3.9 fornece os mesmos valores para tensões de entrada acima de 3V.

Tabela 3.9 – Medida de desvio e erro para tensões acima de 3,0V de entrada.

| Tensão de entrada | Frequência<br>Calculada (KHz) | Frequência<br>Medida (KHz) | Desvio  | Erro de<br>Linearidade |

|-------------------|-------------------------------|----------------------------|---------|------------------------|

| 3,00V             | 888,71                        | 900,90                     | 12,190  | 1,37%                  |

| 3,05V             | 904,03                        | 925,93                     | 21,90   | 2,42%                  |

| 3,10V             | 919,34                        | 952,38                     | 33,04   | 3,59%                  |

| 3,15V             | 934,65                        | 1020,41                    | 85,75   | 9,17%                  |

| 3,20V             | 949,97                        | 1333,33                    | 383,37  | 40,35%                 |

| 3,24V             | 962,22                        | 2631,58                    | 1669,36 | 173,49%                |

Os níveis máximo e mínimo do sinal de entrada são respectivamente o maior e o menor valor possíveis de tensão que produzem uma frequência de saída obedecendo a linearidade do VFC. Se para o valor medido for permitido um erro de até 15%, o VFC proposto passa a apresentar os limites de entrada e saída mostrados na Tabela 3.10.

Tabela 3.10 – Valores máximos e mínimos de operação.

| Tensão de entrada mínima                                | 0,46 V     |

|---------------------------------------------------------|------------|

| Tensão de entrada máxima                                | 3,15 V     |

| Frequência de saída mínima                              | 110,79 KHz |

| Frequência de saída máxima                              | 934,65 KHz |

| Largura de faixa (F <sub>max</sub> - F <sub>min</sub> ) | 811,61 KHz |

### 3.6.6 Variação da frequência em função da temperatura

Apesar de ser projetado para trabalhar em um ambiente com temperatura controlada, ou seja, o corpo humano, uma análise de funcionamento em função da temperatura foi realizada. O número de portadores de carga em um cristal é influenciado pela temperatura, assim sendo, o comportamento dos circuitos eletrônicos se alteram [44,49]. Neste sentido, os componentes eletrônicos semicondutores são classificados de acordo com sua utilização. A Tabela 3.11 mostra uma definição adotada pela indústria de semicondutores [50].

Tabela 3.11 – Faixas de temperatura de trabalho definidas para componentes eletrônicos.

| Aplicação  | Faixa de temperatura |

|------------|----------------------|

| Comercial  | 0°C à 85°C           |

| Industrial | -40°C à 100°C        |

| Extendida  | -40°C à 125°C        |

| Militar    | -55°C à 125°C        |

| Automotiva | -40°C à 125°C        |

Neste trabalho, o VFC será avaliado para a faixa comercial. A Tabela 3.12 mostra o resultado das simulações para diferentes temperaturas.

Tabela 3.12 – Frequência de saída do VFC para diferentes temperaturas.

| Temperatura | Entrada = $0.5V$ | Entrada = $3.0V$ |

|-------------|------------------|------------------|

| 0° C        | 139,03 KHz       | 930,22 KHz       |

| 27° C       | 137,25 KHz       | 903,09 KHz       |

| 50° C       | 136,18 KHz       | 886,36 KHz       |

| 85° C       | 134,95 KHz       | 869,94 KHz       |

A porcentagem de desvio é dada por

$$Variação = 139,03 - 134,95 = 4,08KHz$$

(3.6)

Frequência média =

$$\frac{139,03+134,95}{2}$$

= 136,99 KHz (3.7)

$$Variação (\%) = \frac{4,08/2}{136,99} = 1,49\%$$

(3.8)

Fazendo o mesmo para uma tensão de entrada de 3,0V, tem-se:

$$Variação = 930,22 - 869,94 = 60,28 \, KHz$$

(3.9)

Frequência média =

$$\frac{930,22+869,94}{2}$$

= 900,08 KHz (3.10)

$$Variação (\%) = \frac{60,28/2}{900,08} = 3,35\%$$

(3.11)

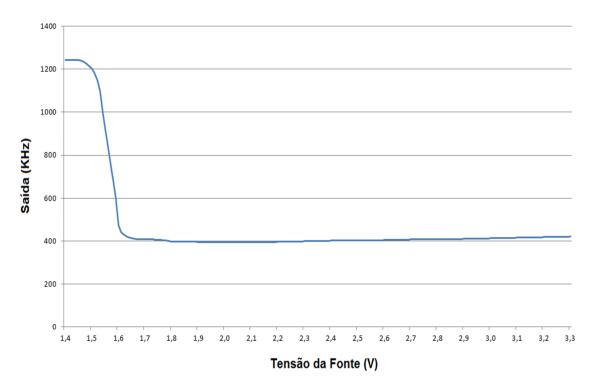

#### 3.6.7 Proporção de rejeição da variação da fonte de alimentação

As referências de tensão utilizadas no VFC estão fixadas em 0,5V e 1,3V, o que determina o ponto de chaveamento de carga e descarga do capacitor. Para análise da rejeição da variação da fonte, foram considerados valores de tensão de alimentação acima de 1,4V, pois o circuito necessita de uma tensão acima de 1,3V para carregar o capacitor. A Tabela 3.13 mostra os resultados obtidos para variação da fonte com uma tensão de entrada de 1,5V. A Figura 3.21 mostra os mesmos resultados graficamente.

Tabela 3.13 – Frequência de saída do VFC em função da tensão de alimentação.

| Tensão da Fonte | Frequência de saída |

|-----------------|---------------------|

| 1,4V            | 1241,0 KHz          |

| 1,5V            | 1191,0 KHz          |

| 1,6V            | 473,5 KHz           |

| 1,7V            | 407,2 KHz           |

| 1,8V            | 396,8 KHz           |

| 1,9V            | 393,2 KHz           |

| 2,0V            | 393,4 KHz           |

| 2,1V            | 395,2 KHz           |

| 2,2V | 397,0 KHz |

|------|-----------|

| 2,3V | 399,0 KHz |

| 2,4V | 400,9 KHz |

| 2,5V | 402,7 KHz |

| 2,6V | 404,7 KHz |

| 2,7V | 406,6KHz  |

| 2,8V | 408,5 KHz |

| 2,9V | 410,5 KHz |

| 3,0V | 412,8 KHz |

| 3,1V | 415,1 KHz |

| 3,2V | 417,8 KHz |

| 3,3V | 420,6 KHz |

Figura 3.21 – Frequência de saída do VFC em função da tensão de alimentação.

A tensão de alimentação prevista para este circuito é de 3,3V, e com esta tensão o circuito VFC deve fornecer na saída uma frequência de 429,31 KHz. Analisando os dados obtidos, pode-se considerar para funcionamento normal, tensões maiores que 1,7V. Em 1,7V a frequência de operação é de 407,2 KHz, portanto:

Variação de frequência =

$$\frac{429,31}{407,2}$$

= 1,0543 (3.12)

Esse valor corresponde à uma variação de 5,43% ou 54300 ppm. Como a tensão de alimentação variou 1,6V em 3,3V, a variação representa 1,6/3,3 = 48,48%. Assim a razão de rejeição da fonte de alimentação é de

$$PSRR = \frac{54300}{48,48} = 1120ppm/\% \tag{3.13}$$

## Capítulo 4 – O modulador PIM

## 4.1 - Descrição do circuito

A Figura 4.1 mostra o circuito completo do modulador PIM.

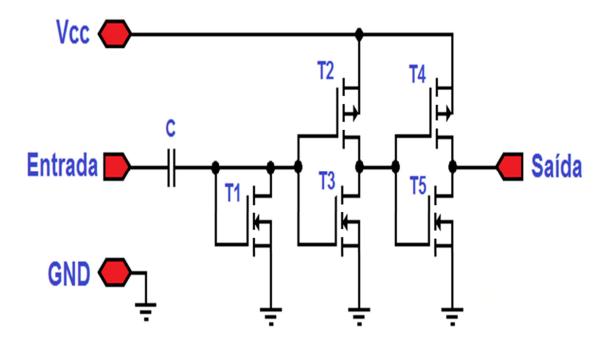

Figura 4.1 – Esquema completo do modulador PIM.

Este circuito é composto por dois inversores formados pelos transistores T2, T3 e T4, T5 e por um circuito de entrada formado pelo transistor T1 e pelo capacitor C.

As dimensões W/L dos transmissores MOS neste circuito utilizam as menores dimensões possíveis da tecnologia IBM CMOS de 130nm levando-se em consideração efeitos já conhecidos como a mobilidade de carga e modulação do canal [44,45]. Estas dimensões são mostradas na Tabela 4.1, o capacitor C possui uma capacitância de 1,5pF.

Tabela 4.1 – Dimensões dos transistores do circuito modulador PIM.

| Transistor | T1   | T2     | T3    | T4     | T5    |

|------------|------|--------|-------|--------|-------|

| W/L (µm)   | 1/15 | 10/1,2 | 3/1,2 | 10/1,2 | 3/1,2 |

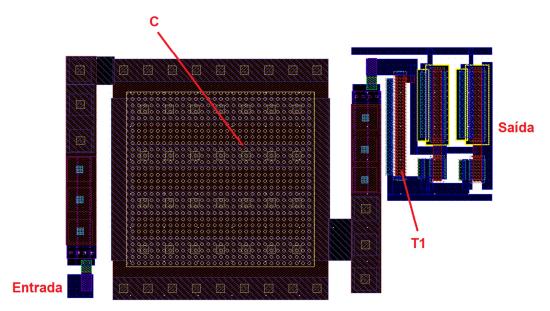

A Figura 4.2 mostra o layout do circuito modulador PIM implementado.

Figura 4.2 – Layout do circuito modulador PIM implementado.

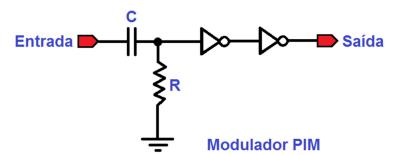

O capacitor C e o transistor T1 formam um circuito RC de entrada que funciona como um temporizador. A Figura 4.3 mostra o esquema simplificado do modulador PIM.

Figura 4.3 – Esquema simplificado do modulador PIM.

Devido à alta impedância de entrada dos transistores T2 e T3, o circuito RC de entrada possui uma constante de tempo dada por

$$\tau = R.C \tag{4.1}$$

onde:

$\tau$  = constante de tempo do circuito de entrada,

R = Valor da resistividade oferecida pelo transistor T1,

C = Capacitância do capacitor C.

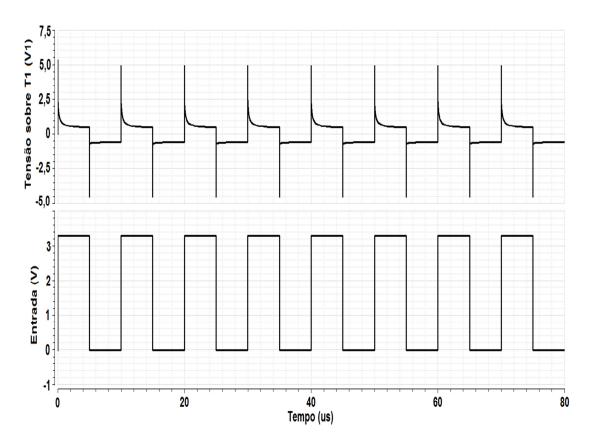

O sinal sobre o transistor T1 representado pela resistência R em resposta à um sinal quadrado ligado à entrada é mostrada na Figura 4.4.

Figura 4.4 – Tensão sobre o transistor T1.

O flanco positivo do sinal de entrada provoca um pulso positivo de tensão sobre T1 e este produz uma mudança de estado dos inversores. O pulso negativo ocorrido no flanco negativo é provocado pela descarga do capacitor que força uma corrente em sentido contrário no transistor T1.

O pulso positivo em T1 é proporcional à corrente do capacitor [51] e pode ser calculado por

$$V_{T1} = V_{CC} \cdot e^{-t/RC} (4.2)$$

A largura do pulso na saída do modulador PIM depende do tempo em que esta tensão permanece acima do limiar de chaveamento dos inversores e da tensão de chaveamento dos inversores.

O transistor T1 trabalha na configuração conexão diodo funcionando como um

resistor. Nesta configuração o transistor está em saturação e sua impedância aproximada pode ser calculada como o inverso da sua transcondutância [45].

$$R = \frac{1}{gm} \tag{4.3}$$

$$gm = \mu_n C_{ox} \frac{W}{L} (V_{GS} - V_{TH}) \tag{4.4}$$

onde:

R = Impedância apresentada entre dreno e fonte,

gm = Transcondutância,

$\mu$ n = Mobilidade das cargas,

C<sub>ox</sub> = Capacitância por unidade área da porta,

V<sub>GS</sub> = Tensão entre gate e fonte,

$V_{TH}$  = Tensão limiar do Mosfet.

### 4.2 – Tempo do pulso

Para determinação do valor da tensão de chaveamento dos inversores, um sinal em rampa foi introduzido diretamente sobre o transistor T1. A Figura 4.5 mostra a resposta à este sinal.

Figura 4.5 – Teste do ponto de chaveamento dos inversores.

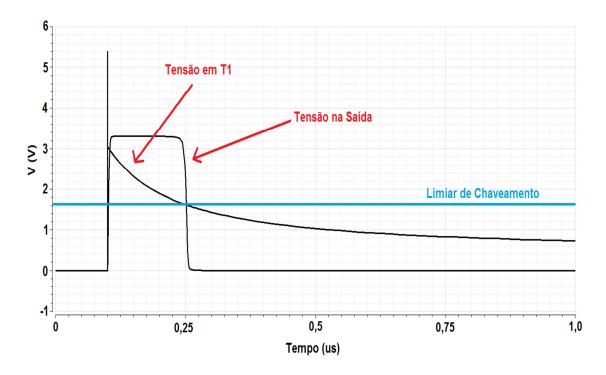

Pelo gráfico, pode-se observar que, para tensões acima de 1,65V em T1 o modulador PIM fornece nível lógico 1 na saída. A Figura 4.6 mostra o comportamento deste circuito com o circuito RC formado pelo capacitor C e o transistor T1.

Figura 4.6 – Ponto de chaveamento dos inversores determinado por RC.

Através da variação da capacitância de C ou das dimensões de T1 pode-se controlar a largura do pulso. A Tabela 4.2 mostra o tempo do pulso em função das dimensões de T1 e capacitância de C igual à 1,5pF.

Tabela 4.2 – Tempo do pulso do modulador PIM em função das dimensões de T1.

| Dimensões W/L | Tempo    |

|---------------|----------|

| 1/5           | 55,46us  |

| 1/10          | 103,95us |

| 1/15          | 155,29us |

| 1/20          | 199,79us |

| 1/25          | 249,70us |

| 1/30          | 294,98us |

Obviamente é possível controlar o tempo do pulso pela variação da capacitância de C, porém essa mudança implica em um redimensionamento deste capacitor e uma grande alteração do layout.

### 4.3 – Análise da variação da fonte

Com o objetivo de testar o funcionamento deste circuito com relação às variações da fonte, um sinal quadrado de período igual à 10us e tensões entre 0 e  $V_{CC}$  foi aplicado na entrada do modulador. A tensão máxima deste sinal acompanhará a tensão da fonte pois, estando o modulador PIM acoplado ao VFC as tensões de alimentação são compartilhadas.

Como a largura do pulso não altera a informação transmitida, o que se espera obter como resposta é se o circuito responde ou não ao sinal de entrada. A tabela 4.3 mostra os resultados deste teste.

| Tensão da fonte | Funcionamento correto |

|-----------------|-----------------------|

| 0,3V            | Não                   |

| 0,6V            | Não                   |

| 0,9V            | Não                   |

| 1,2V            | Não                   |

| 1,5V            | Sim                   |

| 1,8V            | Sim                   |

| 2,1V            | Sim                   |

Tabela 4.3 – Funcionamento do modulador PIM com variação da fonte.

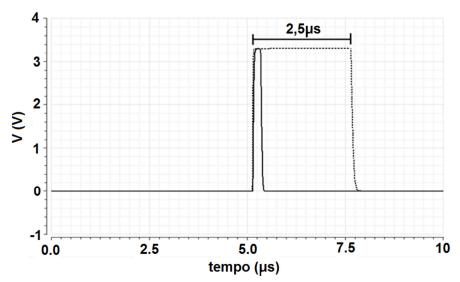

A Figura 4.7 mostra a resposta à um sinal quadrado na entrada com tensão de alimentação de 1,5V.

Figura 4.7 – Tensões no modulador PIM com alimentação de 1,5V.

O pulso inicial de saída largo ocorre devido ao fato do capacitor estar inicialmente todo descarregado. Após o primeiro pulso o circuito se estabiliza e mantém-se com uma largura de pulso de saída constante. Pode-se então concluir que, o circuito funciona corretamente para tensões de alimentação acima de 1,5V.

## 4.4 – Análise de variação da temperatura

Para o teste de temperatura do modulador PIM foi considerado a faixa de temperatura comercial, como mostrado na Tabela 3.11. A Tabela 4.4, da mesma forma que a Tabela 4.3 mostra a condição de funcionamento do modulador PIM.

Tabela 4.4 – Condição de funcionamento do modulador PIM com variação de temperatura.

| Temperatura | Funcionamento correto |

|-------------|-----------------------|

| 0° C        | Sim                   |

| 27° C       | Sim                   |

| 50° C       | Sim                   |

| 85° C       | Sim                   |

No teste, o sinal de saída se manteve com a variação da temperatura.

# Capítulo 5 – Análise do VFC com Modulador PIM

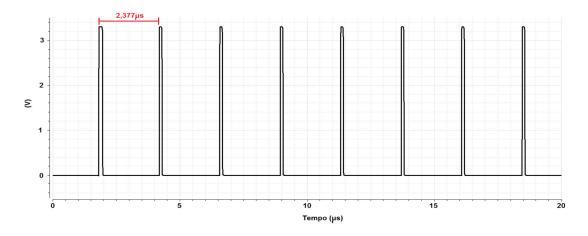

Neste capítulo o VFC será analisado em conjunto com o modulador PIM, que para diferenciar do circuito VFC será denominado VFC-PIM.

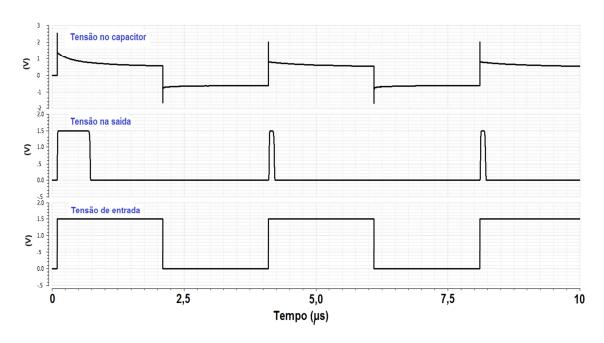

### 5.1 – Sinal de saída

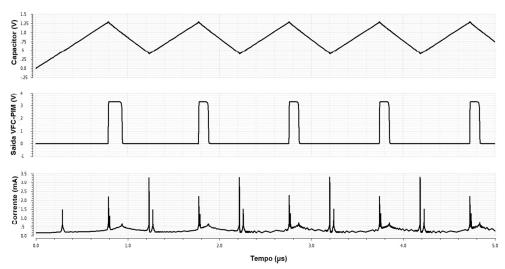

A Figura 5.1 mostra o sinal de saída do conjunto VFC e modulador PIM quando se aplica 1,5V na sua entrada.

Figura 5.1 – Sinal de saída do circuito VFC-PIM com 1,5V de entrada.

Como o VFC trabalha linearmente de 0,46V à 3,15V, deve-se analisar o intervalo entre pulsos referente à esses valores. A Tabela 5.1 mostra os resultados dos testes.

| Tensão de entrada | Intervalo entre pulsos | Frequência  |

|-------------------|------------------------|-------------|

| 0,46V             | 7,90µs                 | 126,58 KHz  |

| 0,75V             | 4,87μs                 | 205,34 KHz  |

| 1,00V             | 3,63µs                 | 275,48 KHz  |

| 1,25V             | 2,88µs                 | 347,22 KHz  |

| 1,50V             | 2,38µs                 | 420,17 KHz  |